MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 11-17

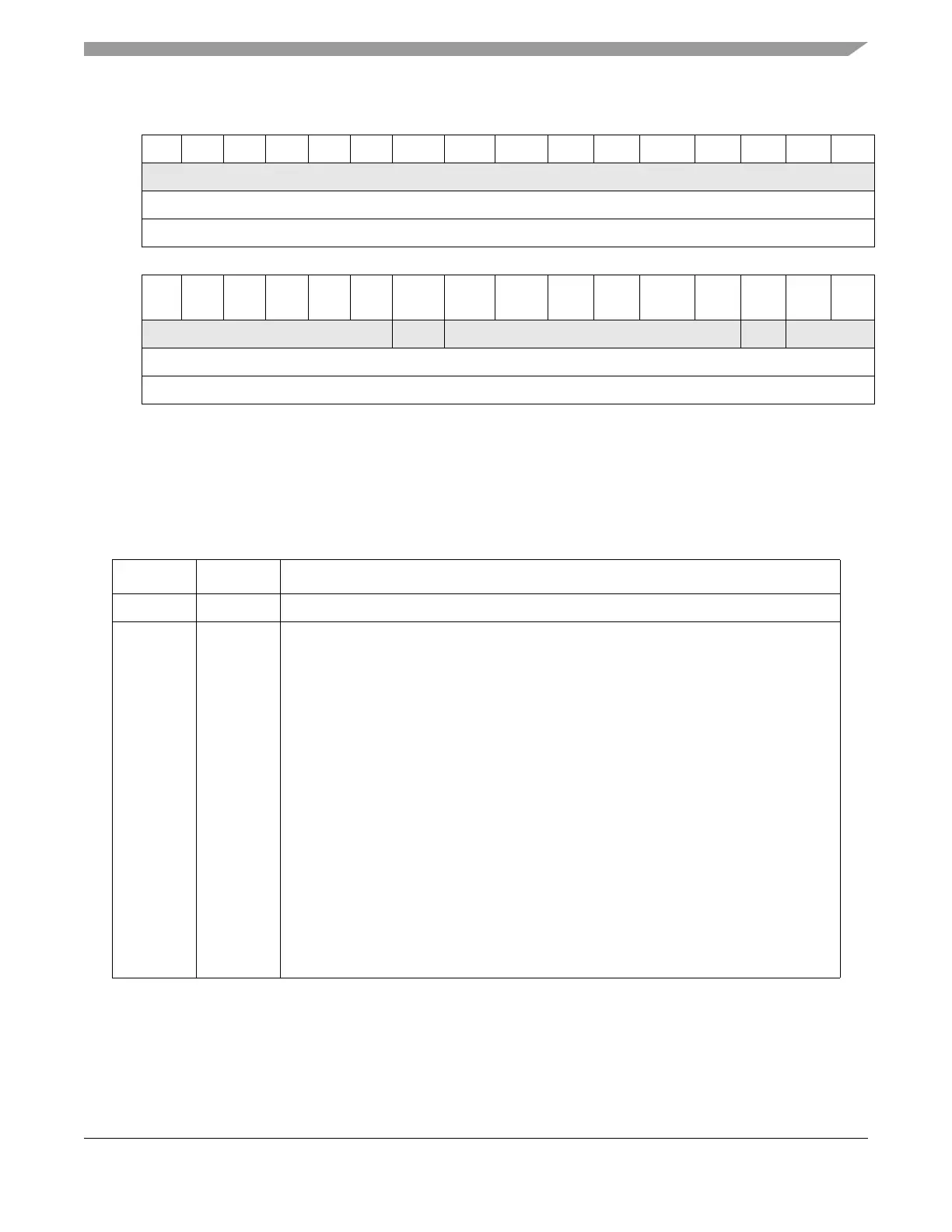

012345 6 7 8 910 11 12131415

R000000 0 0 0 0 0 0 0 0 0 0

W

Reset000000 0 0 0 0 0 0 0 0 0 0

Reg Addr Base + 0x0004

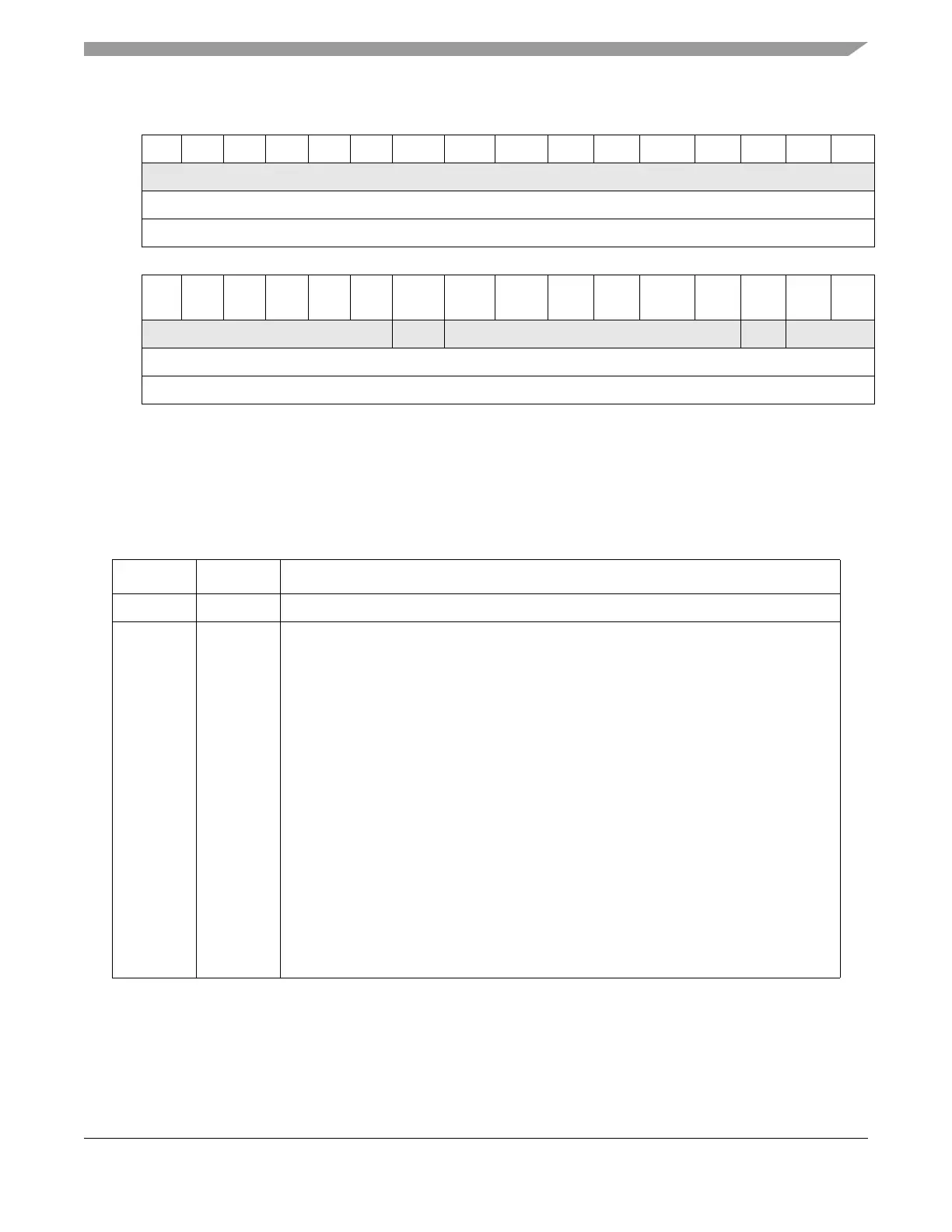

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 0 LOLF LOC MODE PLL

SEL

PLL

REF

LOCKS LOCK LOCF CALD

ONE

CAL

PASS

W

w1c w1c

Reset000000 0 0 —

1

—

1

—

1

—

1

—

2

000

Reg Addr Base + 0x0004

1

Reset state determined during reset configuration. (See Section 11.1.4, “FMPLL Modes of Operation,” for more

information.)

2

Reset state determined during reset.

3

“w1c” signifies that this bit is cleared by writing a 1 to it.

Figure 11-9. Synthesizer Status Register (FMPLL_SYNSR)

Table 11-6. FMPLL_SYNSR Field Descriptions

Bits Name Description

0–21 — Reserved.

22 LOLF Loss-of-lock flag. Provides the interrupt request flag. This is a write 1 to clear (w1c) bit; to

clear the flag, the user must write a 1 to the bit. Writing 0 has no effect. This flag will not be

set, and an interrupt will not be requested, if the loss of lock condition was caused by a

system reset, a write to the FMPLL_SYNCR which modifies the MFD bits, or enabling

frequency modulation. If the flag is set due to a system failure, writing the MFD bits or

enabling FM will not clear the flag. Asserting reset will clear the flag. This flag bit is sticky

in the sense that if lock is reacquired, the bit will remain set until either a write 1 or reset is

asserted.

0 Interrupt service not requested

1 Interrupt service requested

Note: Upon a loss-of-lock that is not generated by:

• a system reset

• a write to the FMPLL_SYNCR that modifies the MFD or PREDIV bits

• enabling of frequency modulation

the LOLF is set only if LOLIRQ is set. If the FMPLL reacquires lock and any of the

previous conditions in the bulleted list occurs, the LOLF is set again. To avoid

generating an unintentional interrupt, clear LOLIRQ before changing MFD or

PREDIV, or before enabling FM after a previous interrupt and relock occurred.

Loading...

Loading...