MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-29

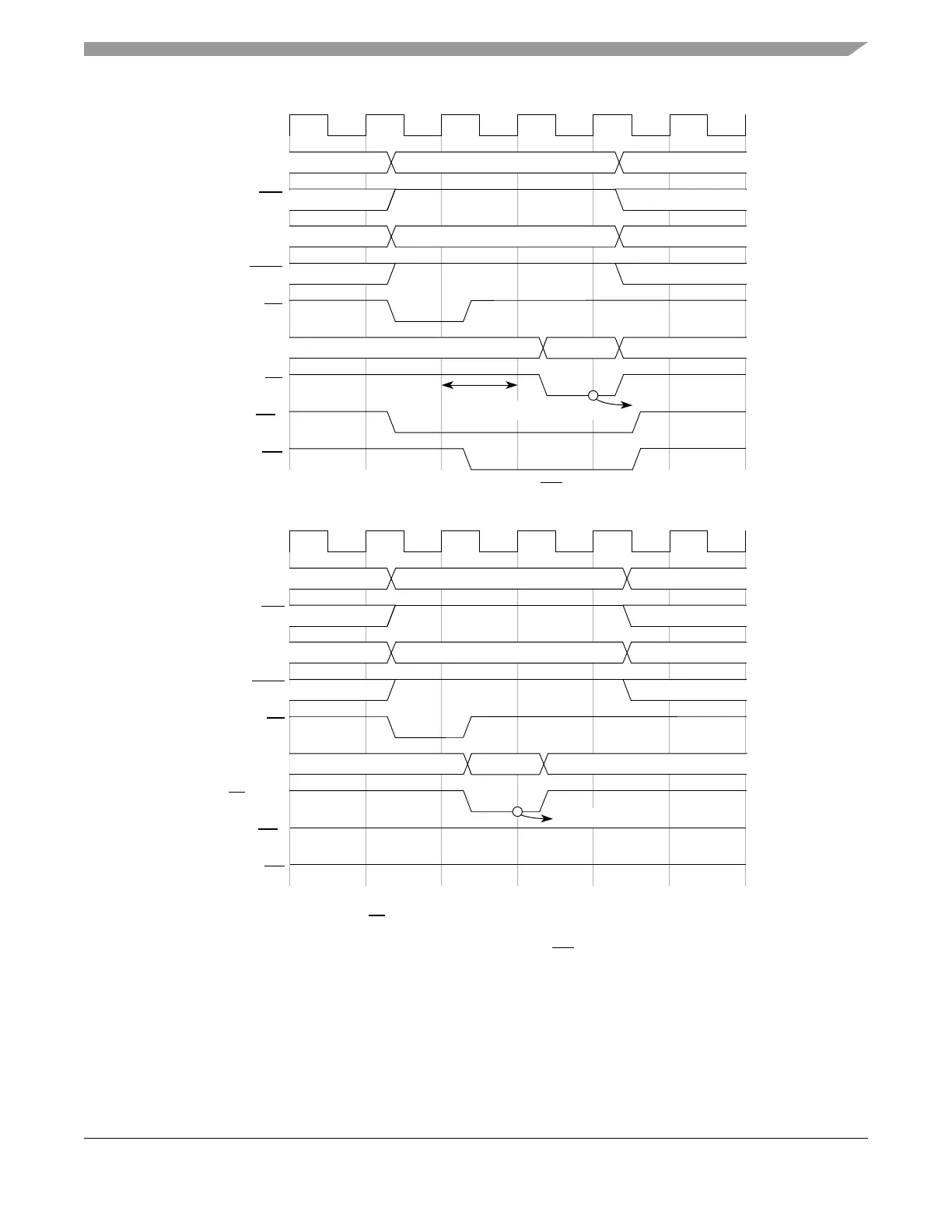

Figure 12-11. Single Beat 32-bit Read Cycle, CS Access, One Wait State

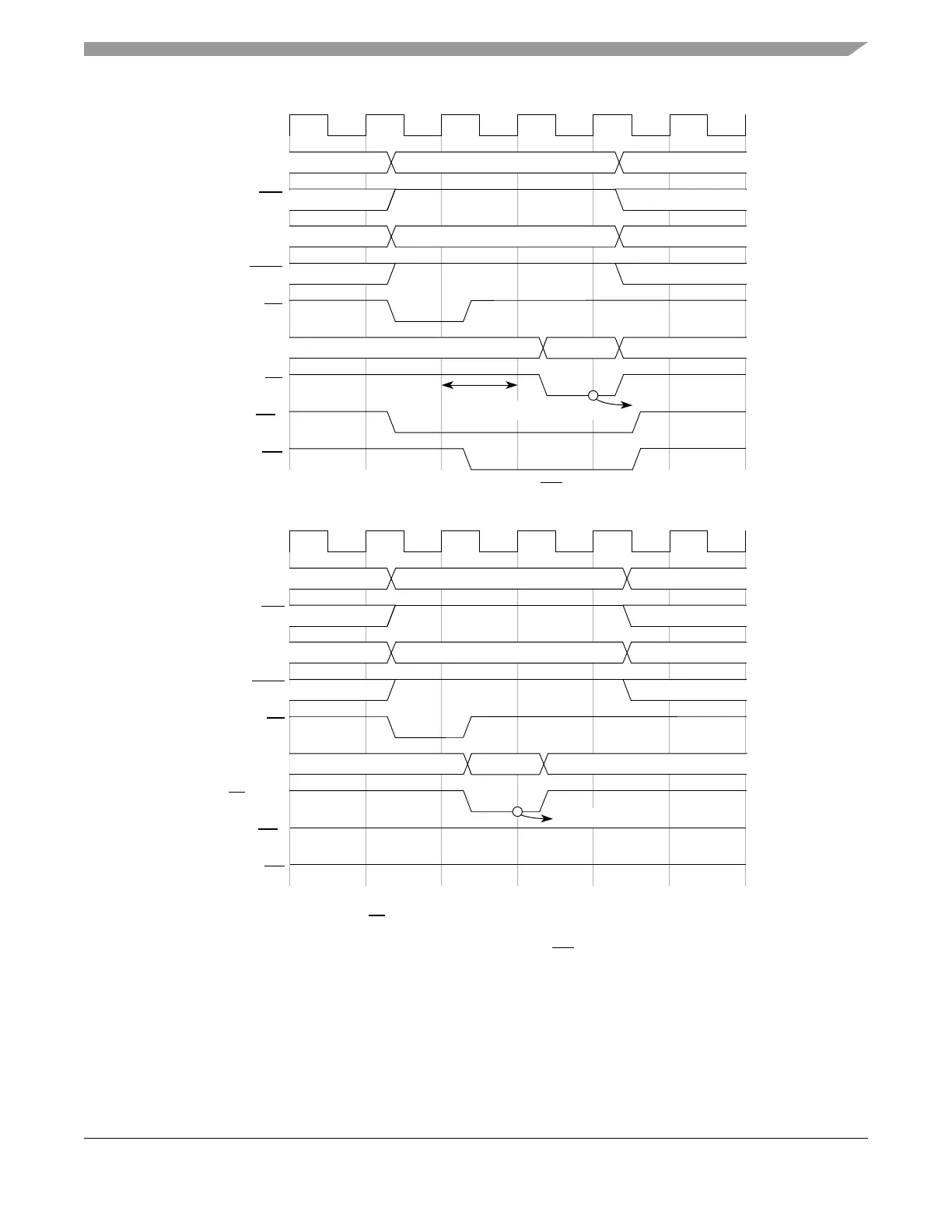

Figure 12-12. Single Beat 32-bit Read Cycle, Non-CS

Access, Zero Wait States

Wait state

00

DATA is valid

CLKOUT

ADDR[8:31]

TS

DATA[0:31]

TA

RD_WR

TSIZ[0:1]

BDIP

OE

CSx

00

DATA is valid

The EBI drives address and control signals an extra cycle because it uses a latched

version of the external TA (1 cycle delayed) to terminate the cycle.

*

*

CLKOUT

ADDR[8:31]

TS

DATA[0:31]

T

A(input)

RD_WR

TSIZ[0:1]

BDIP

OE

CSx

Loading...

Loading...