MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 14-31

14.3.4.3.1 FIFO Receive Start Register (FRSR)

The FRSR is a 32-bit register with one 8-bit field programmed by the user to indicate the starting address

of the receive FIFO. FRSR marks the boundary between the transmit and receive FIFOs. The transmit

FIFO uses addresses from the start of the FIFO to the location four bytes before the address programmed

into the FRSR. The receive FIFO uses addresses from FRSR to FRBR inclusive.

The FRSR register is initialized by hardware at reset. FRSR only needs to be written to change the default

value.

14.3.4.3.2 Receive Descriptor Ring Start (ERDSR)

The ERDSR is written by the user. It provides a pointer to the start of the circular receive buffer descriptor

queue in external memory. This pointer must be 32-bit aligned; however, it is recommended it be made

128-bit aligned (evenly divisible by 16).

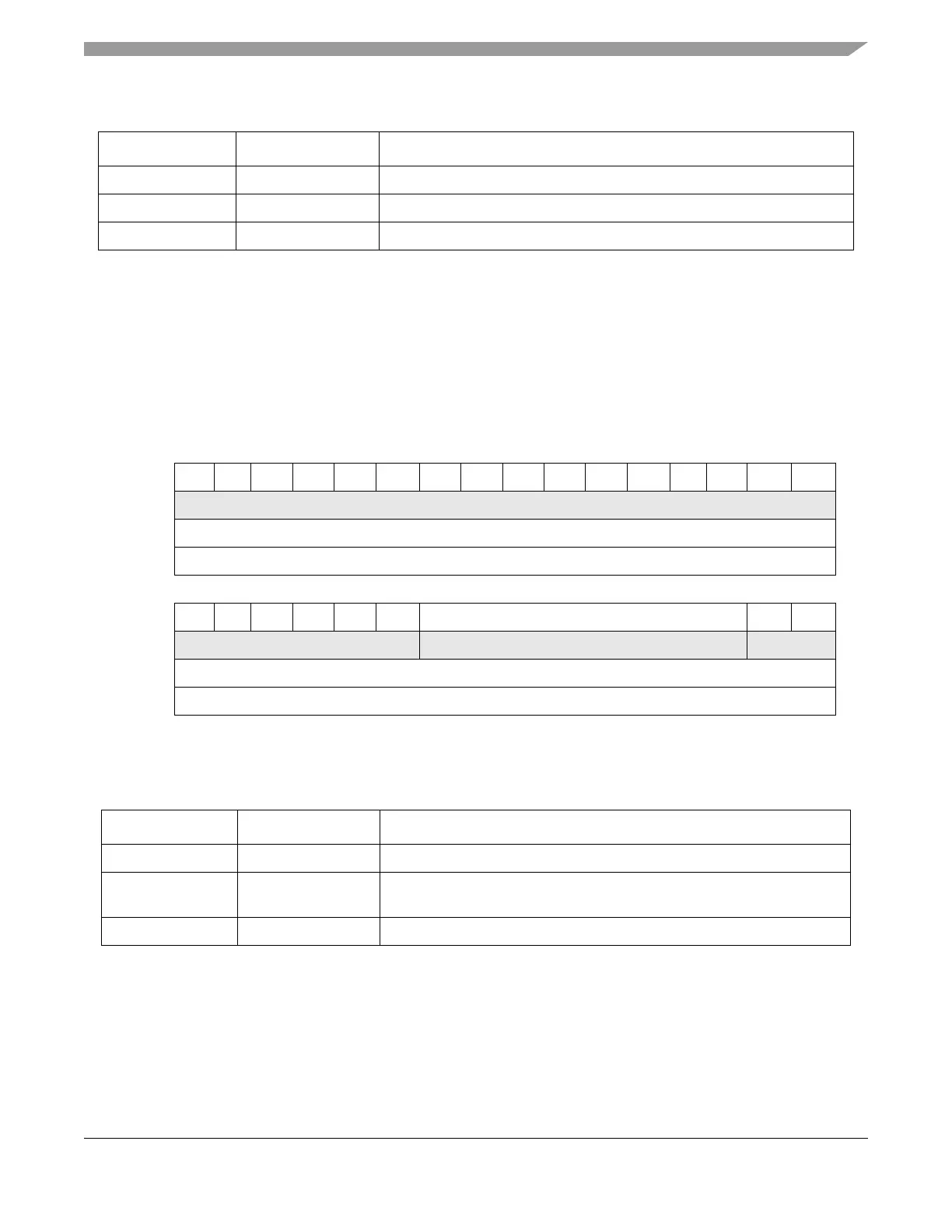

Table 14-24. FRBR Field Descriptions

Bits Name Descriptions

0–21 — Reserved, read as 0 (except bit 10, which is read as 1).

22–29 R_BOUND Read-only. Highest valid FIFO RAM address.

30–31 — Reserved, should be cleared.

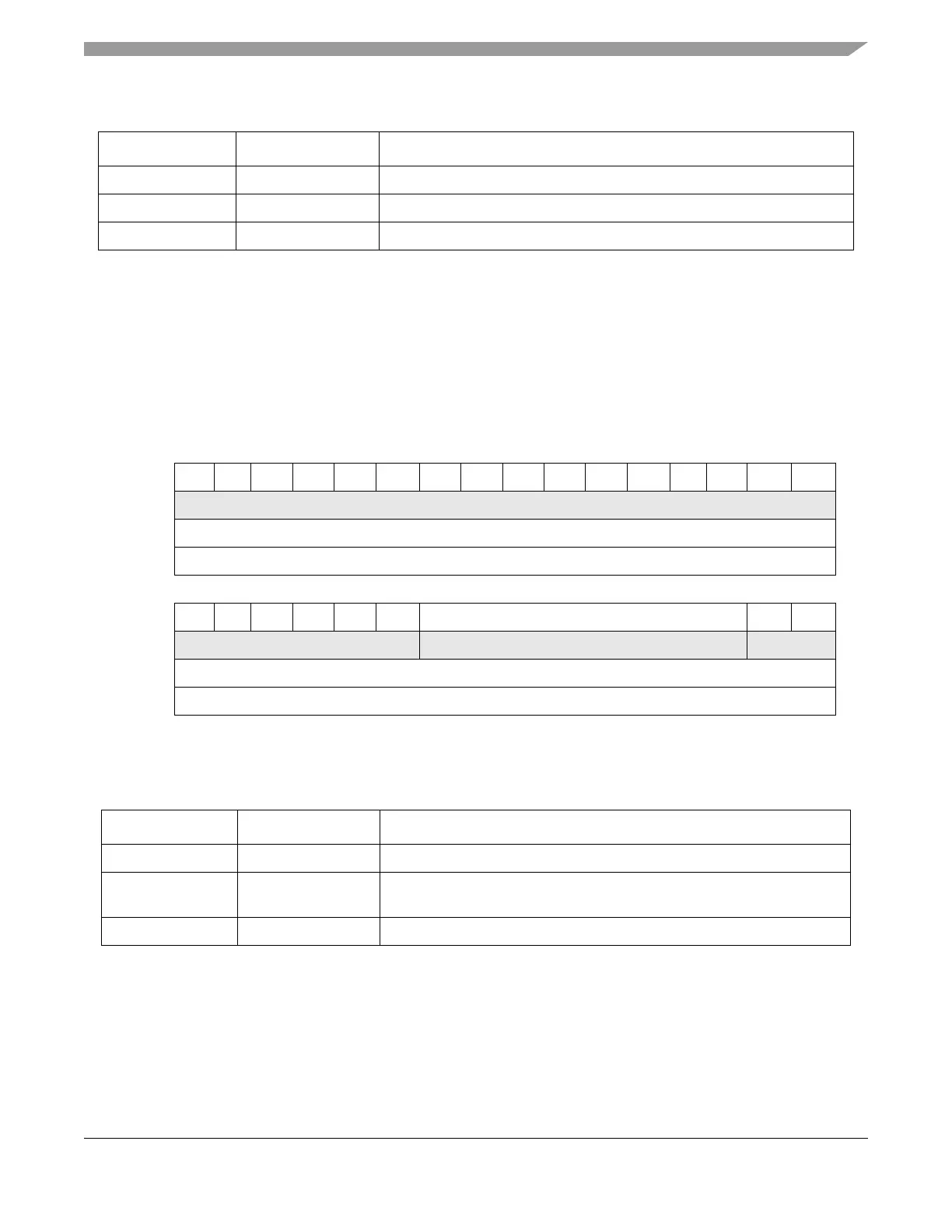

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R000000000000000 0

W

Reset000000000000000 0

Address Base + 0x0150

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 0 0 0 0 0 R_FSTART 0 0

W

Reset000001010000000 0

Address Base + 0x0150

Figure 14-22. FIFO Receive Start Register (FRSR)

Table 14-25. FRSR Field Descriptions

Bits Name Descriptions

0–21 — Reserved, read as 0 (except bit 10, which is read as 1).

22–29 R_FSTART Address of first receive FIFO location. Acts as delimiter between receive and

transmit FIFOs.

30–31 — Reserved, read as 0.

Loading...

Loading...