MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-9

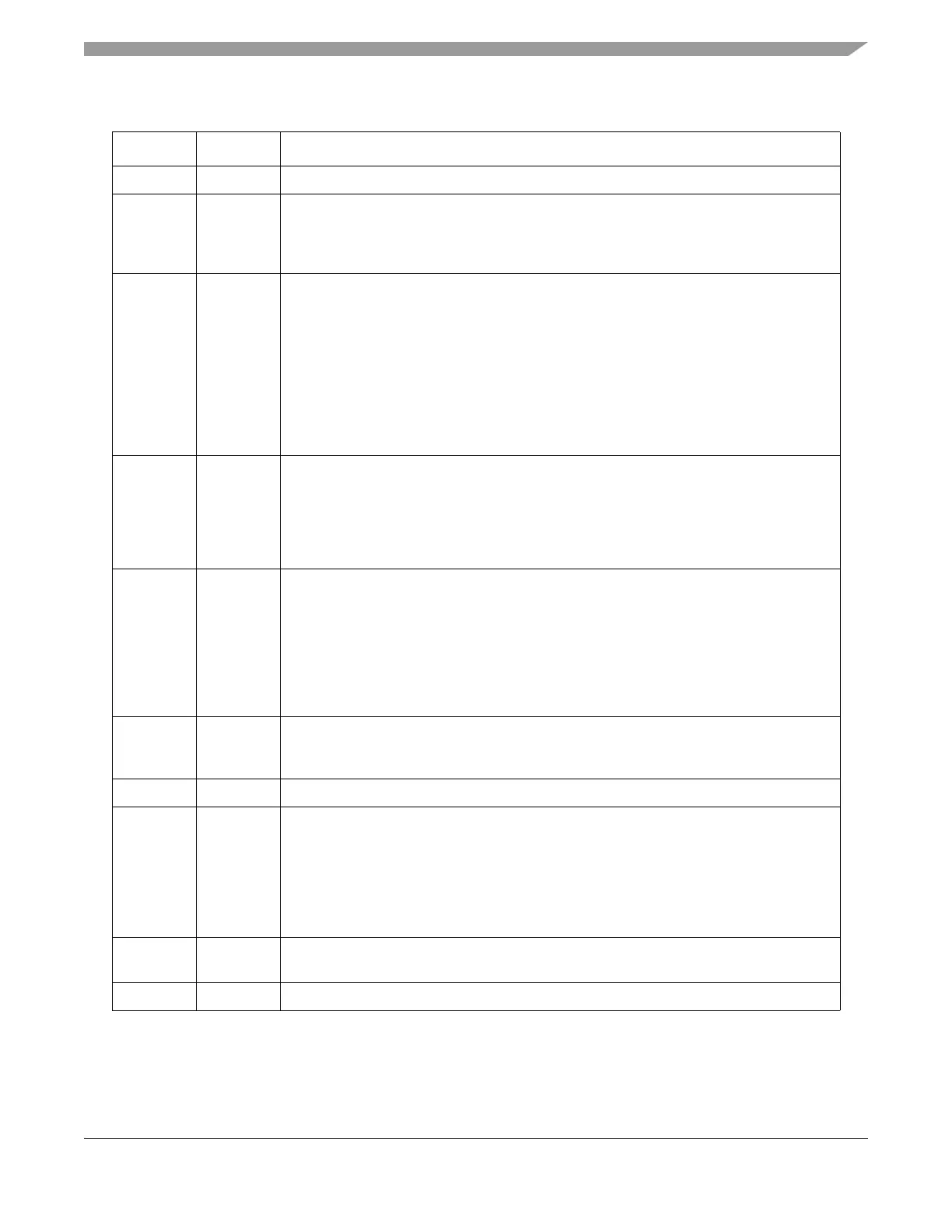

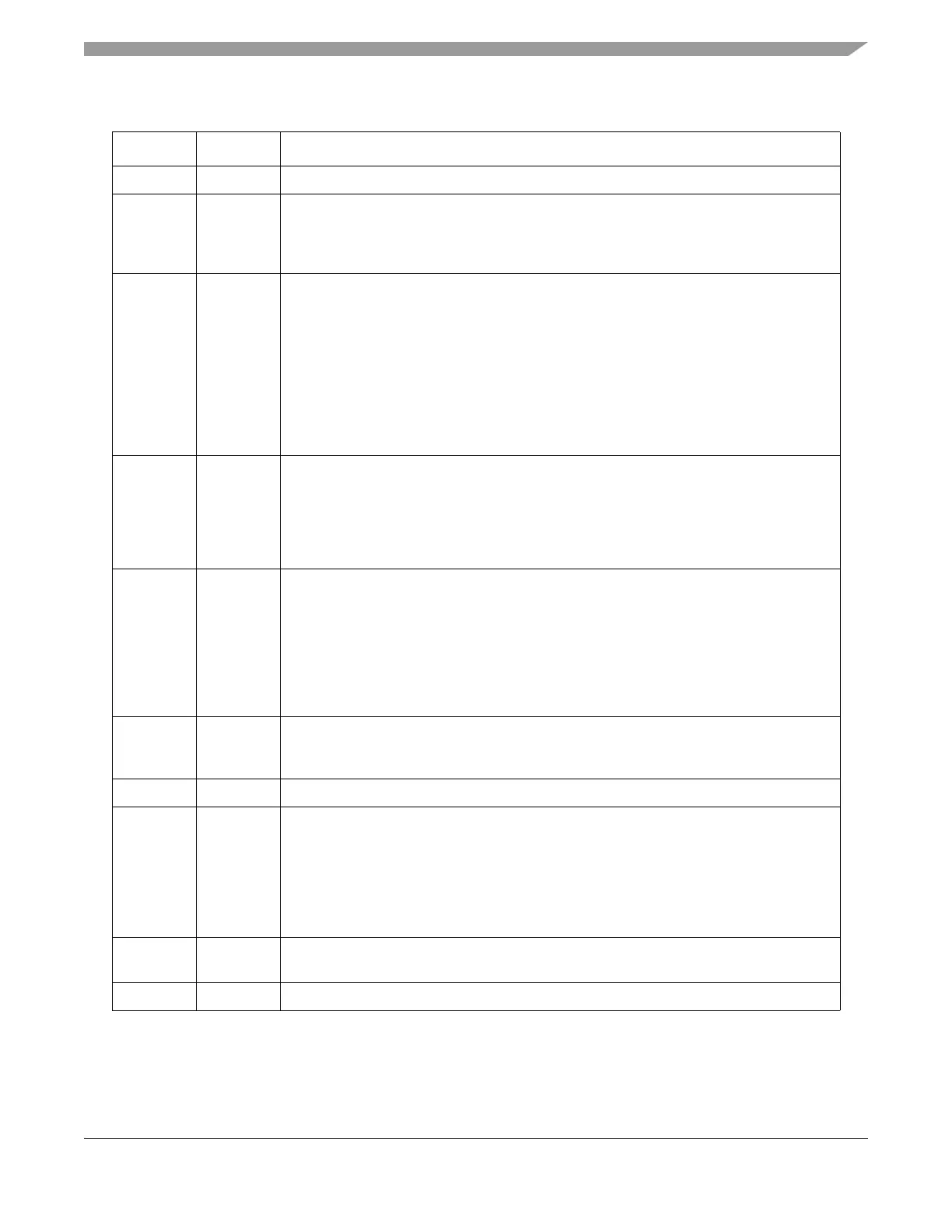

Table 17-6. EMIOS_MCR Field Descriptions

Bits Name Description

0 — Reserved. This bit is readable/writable, but has no effect.

1 MDIS Module disable. Puts the eMIOS in low power mode. The MDIS bit is used to stop the clock

of the module, except the access to registers EMIOS_MCR and EMIOS_OUDR.

0 Clock is running

1 Enter low power mode

2 FRZ Freeze. Enables the eMIOS to freeze the registers of the unified channels when debug

mode is requested at MCU level. Each unified channel should have FREN bit set in order

to enter freeze mode. While in freeze mode, the eMIOS continues to operate to allow the

MCU access to the unified channels registers. The unified channel will remain frozen until

the FRZ bit is written to zero or the MCU exits debug mode or the unified channel FREN

bit is cleared.

0 Allows unified channels to continue to operate when device enters debug mode and the

EMIOS_CCRn[FREN] bit is set

1 Stops unified channels operation when in debug mode and the EMIOS_CCRn[FREN]

bit is set

3GTBE

1

1

The GTBE signal is an inter-module signal, not an external pin on the device.

Global time base enable. Used to export a global time base enable from the module and

provide a method to start time bases of several modules simultaneously.

0 Global time base enable out signal negated

1 Global time base enable out signal asserted

Note: The global time base enable input signal controls the internal counters. When

asserted, internal counters are enabled. When negated, internal counters disabled.

4 ETB External time base. Selects the time base source that drives counter bus[A].

0 Unified channel 23 drives counter bus[A]

1 STAC drives counter bus[A]

Note: If ETB is set to select STAC as the counter bus[A] source, the GTBE must be set to

enable the STAC to counter bus[A]. See Section 17.4.2, “STAC Client Submodule” and the

shared time and angle clock (STAC) bus interface section and the STAC bus configuration

register (ETPU_REDCR) section of the eTPU chapter for more information about the

STAC.

5 GPREN Global prescaler enable. Enables the prescaler counter.

0 Prescaler disabled (no clock) and prescaler counter is cleared

1 Prescaler enabled

6–11 — Reserved.

12–15 SRV

[0:3]

Server time slot. Selects the address of a specific STAC server to which the STAC client

submodule is assigned (refer to Section 17.4.2, “STAC Client Submodule,” for details)

0000 – eTPU engine A, TCR1

0001 – eTPU engine B, TCR1

0010 – eTPU engine A, TCR2

0011 – eTPU engine B, TCR2

0100–1111 reserved

16–23 GPRE

[0:7]

Global prescaler. Selects the clock divider value for the global prescaler, as shown in

Ta bl e 1 7- 7 below.

24–31 — Reserved.

Loading...

Loading...