MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

17-14 Freescale Semiconductor

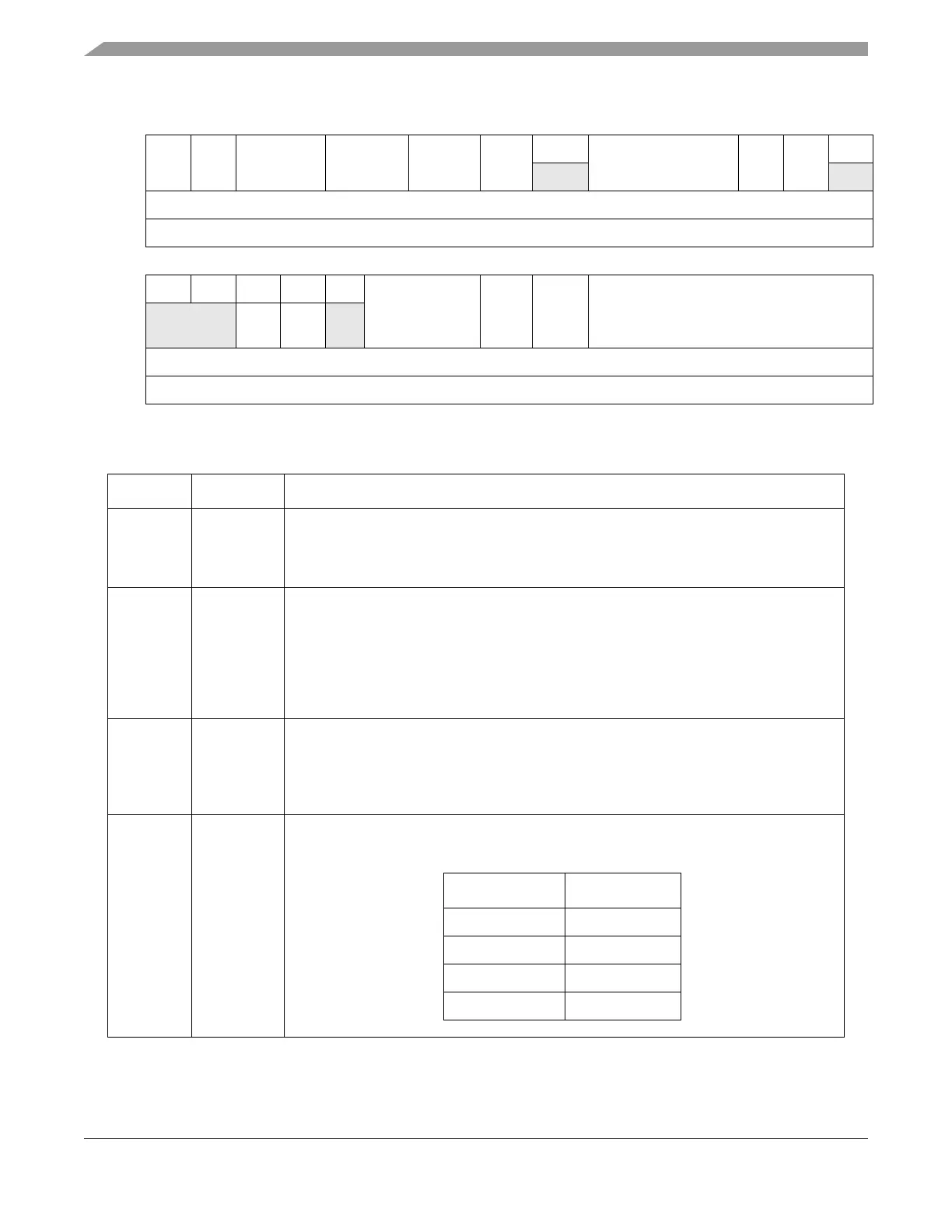

012345 6 7 8 9101112131415

R FREN ODIS ODISSL UCPRE UCPREN DMA 0 IF FCK FEN 0

W

Reset000000 0 0 00000000

Reg Addr UCn Base + 0x000C

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000 BSL EDSELEDPOL MODE

W FOR

CMA

FOR

CMB

Reset000000 0 0 00000000

Reg Addr UCn Base + 0x000C

Figure 17-8. eMIOS Channel Control Register (EMIOS_CCRn)

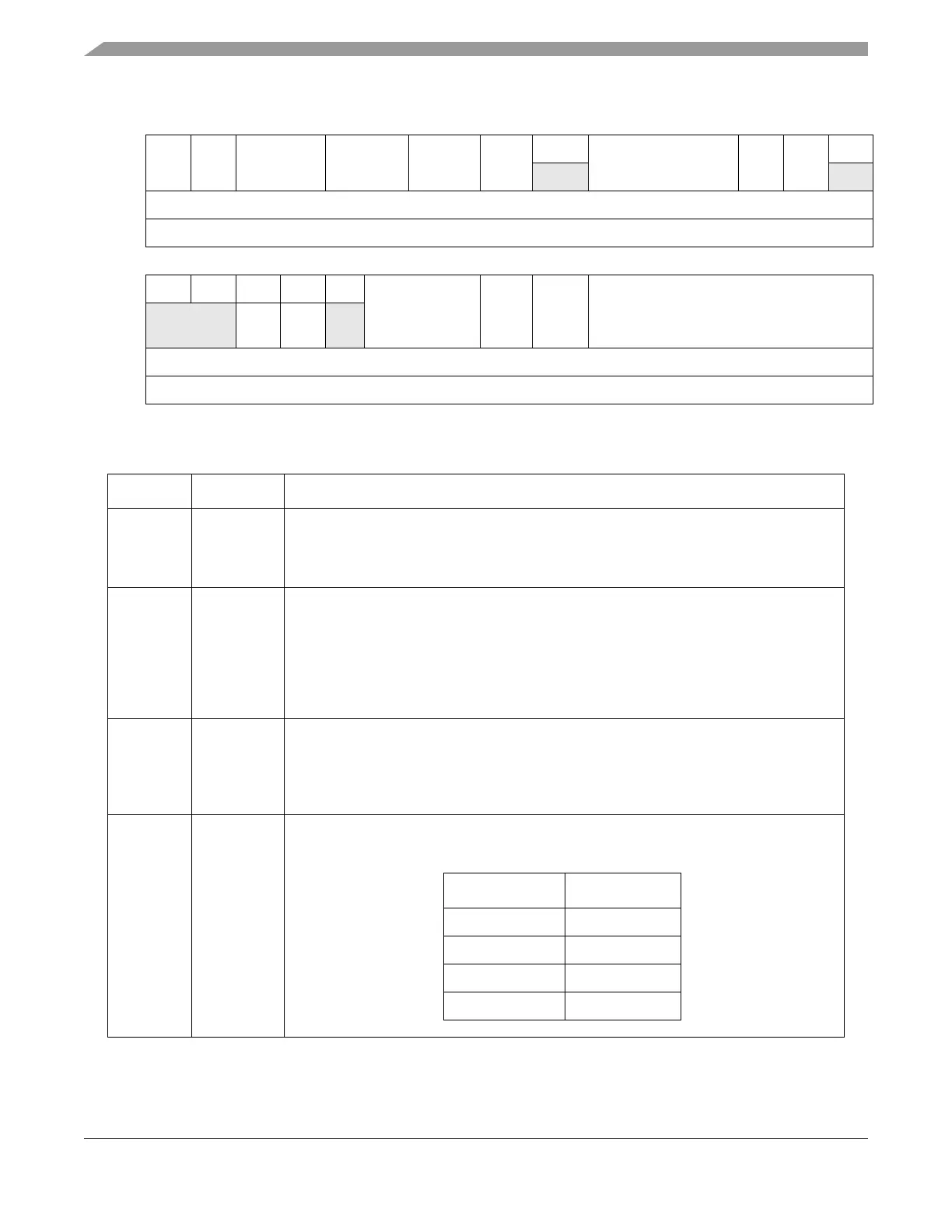

Table 17-10. EMIOS_CCRn Field Description

Bits Name Description

0 FREN Freeze enable. If set and validated by FRZ bit in EMIOS_MCR, freezes all registers values

when in debug mode, allowing the MCU to perform debug functions.

0 Normal operation

1 Freeze UC registers values

1 ODIS Output disable. Allows output disable in any output mode except GPIO.

0 The output pin operates normally

1 If the selected output disable input signal is asserted, the output pin goes to the

complement of EDPOL for OPWFM, OPWFMB, and OPWMB modes, but the unified

channel continues to operate normally; that is, it continues to produce FLAG and

matches. When the selected output disable input signal is negated, the output pin

operates normally.

2–3 ODISSL

[0:1]

Output disable select. Selects one of the four output disable input signals.

00 output disable input 0

01 output disable input 1

10 output disable input 2

11 output disable input 3

4–5 UCPRE

[0:1]

Prescaler. Selects the clock divider value for the unified channel internal prescaler, as

shown below.

UCPRE[0:1] Divide Ratio

00 1

01 2

10 3

11 4

Loading...

Loading...