MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

17-16 Freescale Semiconductor

8 — Reserved.

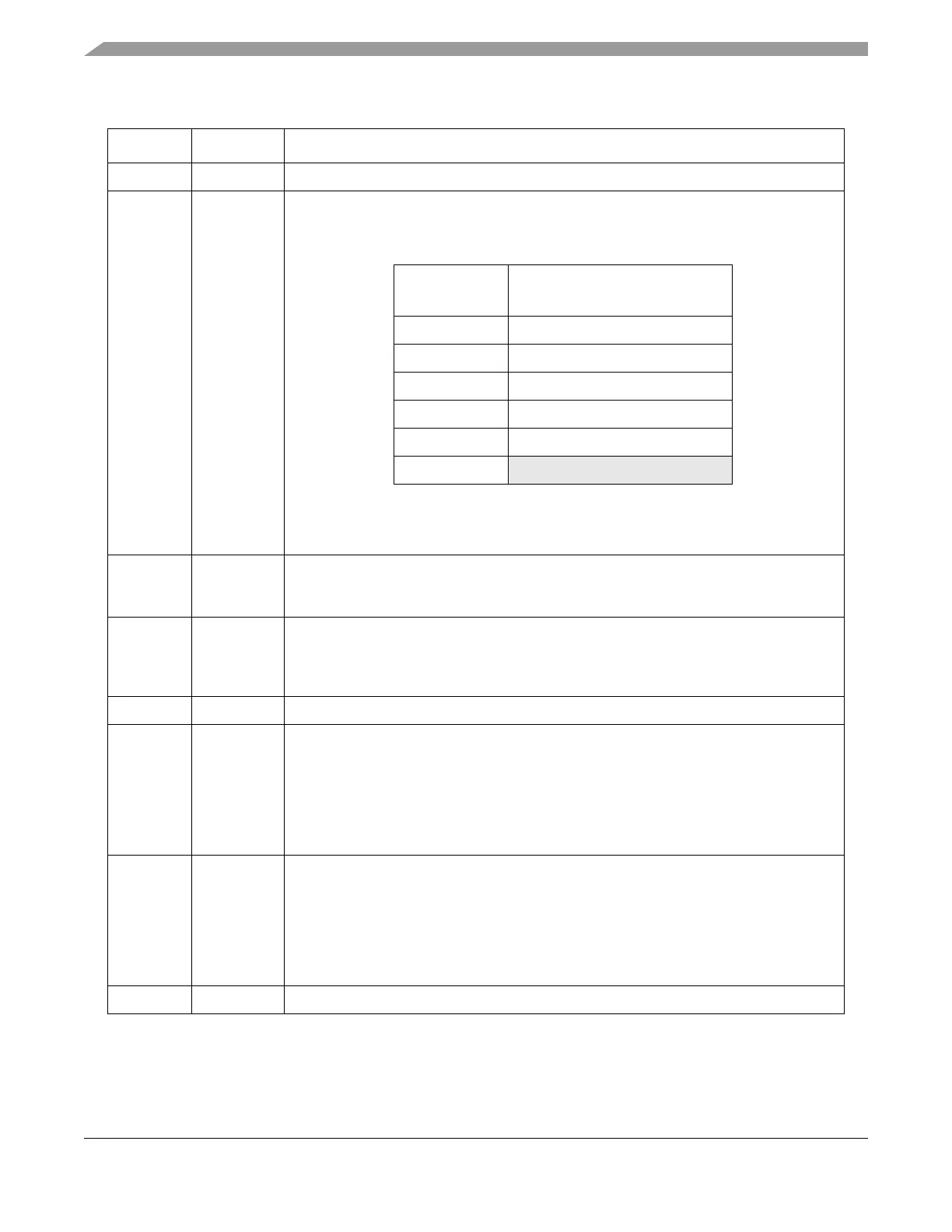

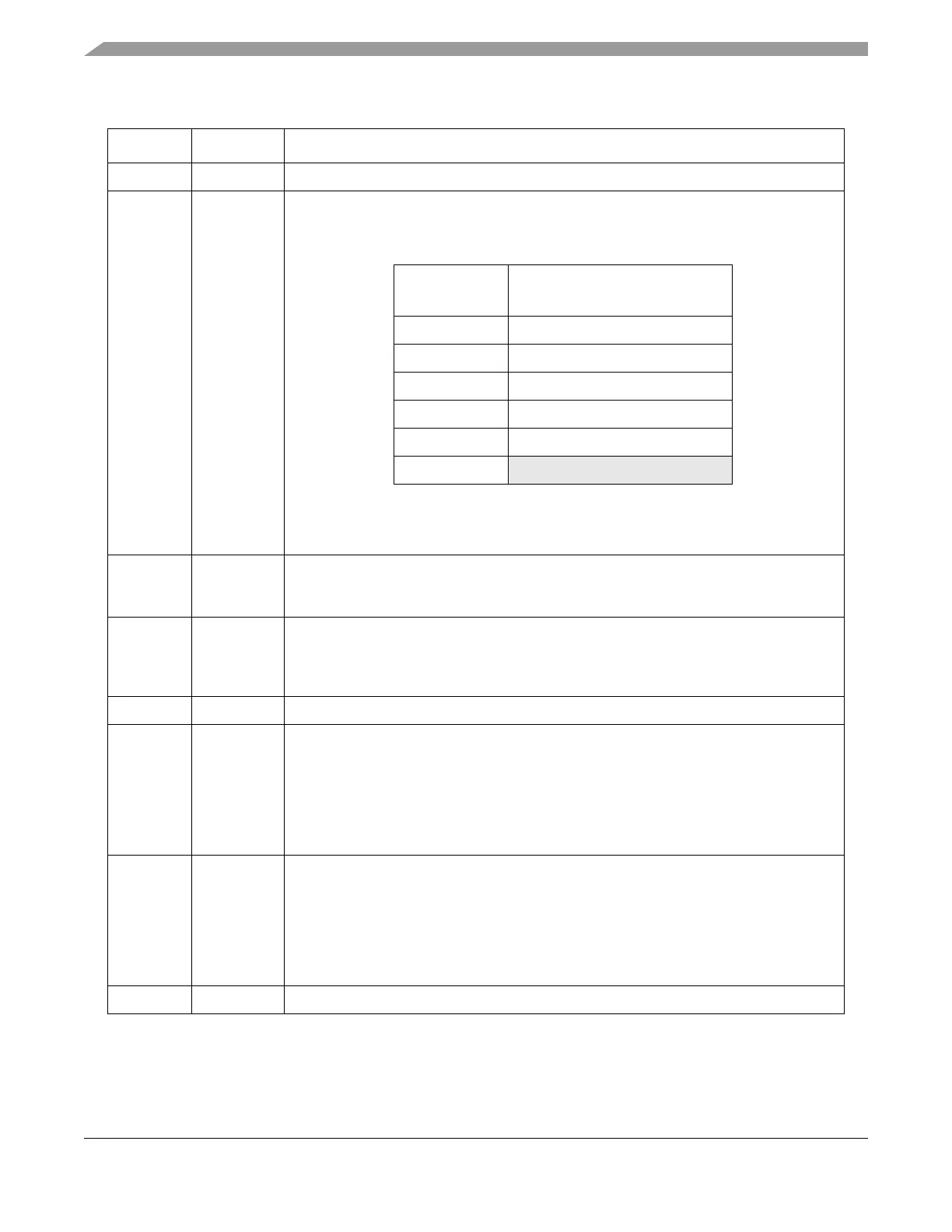

9–12 IF

[0:3]

Input filter. Controls the programmable input filter, selecting the minimum input pulse width

that can pass through the filter, as shown below. For output modes, these bits have no

meaning.

13 FCK Filter clock select. Selects the clock source for the programmable input filter.

0 Prescaled clock

1 Main clock

14 FEN FLAG enable. Allows the unified channel FLAG bit to generate an interrupt signal or a DMA

request signal (The type of signal to be generated is defined by the DMA bit).

0 Disable (FLAG does not generate an interrupt or DMA request)

1 Enable (FLAG will generate an interrupt or DMA request)

15–17 — Reserved.

18 FORCMA Force match A. For output modes, the FORCMA bit is equivalent to a successful

comparison on comparator A (except that the FLAG bit is not set). This bit is cleared by

reset and is always read as zero. This bit is valid for every output operating mode which

uses comparator A, otherwise it has no effect.

0 Has no effect

1 Force a match at comparator A

For input modes, the FORCMA bit is not used and writing to it has no effect.

19 FORCMB Force match B. For output modes, the FORCMB bit is equivalent to a successful

comparison on comparator B (except that the FLAG bit is not set). This bit is cleared by

reset and is always read as zero. This bit is valid for every output operating mode which

uses comparator B, otherwise it has no effect.

0 Has no effect

1 Force a match at comparator B

For input modes, the FORCMB bit is not used and writing to it has no effect.

20 — Reserved.

Table 17-10. EMIOS_CCRn Field Description (Continued)

Bits Name Description

IF[0:3]

1

1

Filter latency is 3 clock cycles.

Minimum input pulse width

[filter clock periods]

0000 Bypassed

2

2

The input signal is synchronized before arriving at the

digital filter.

0001 2 filter clock periods

0010 4 filter clock periods

0100 8 filter clock periods

1000 16 filter clock periods

all others Reserved

Loading...

Loading...