MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-17

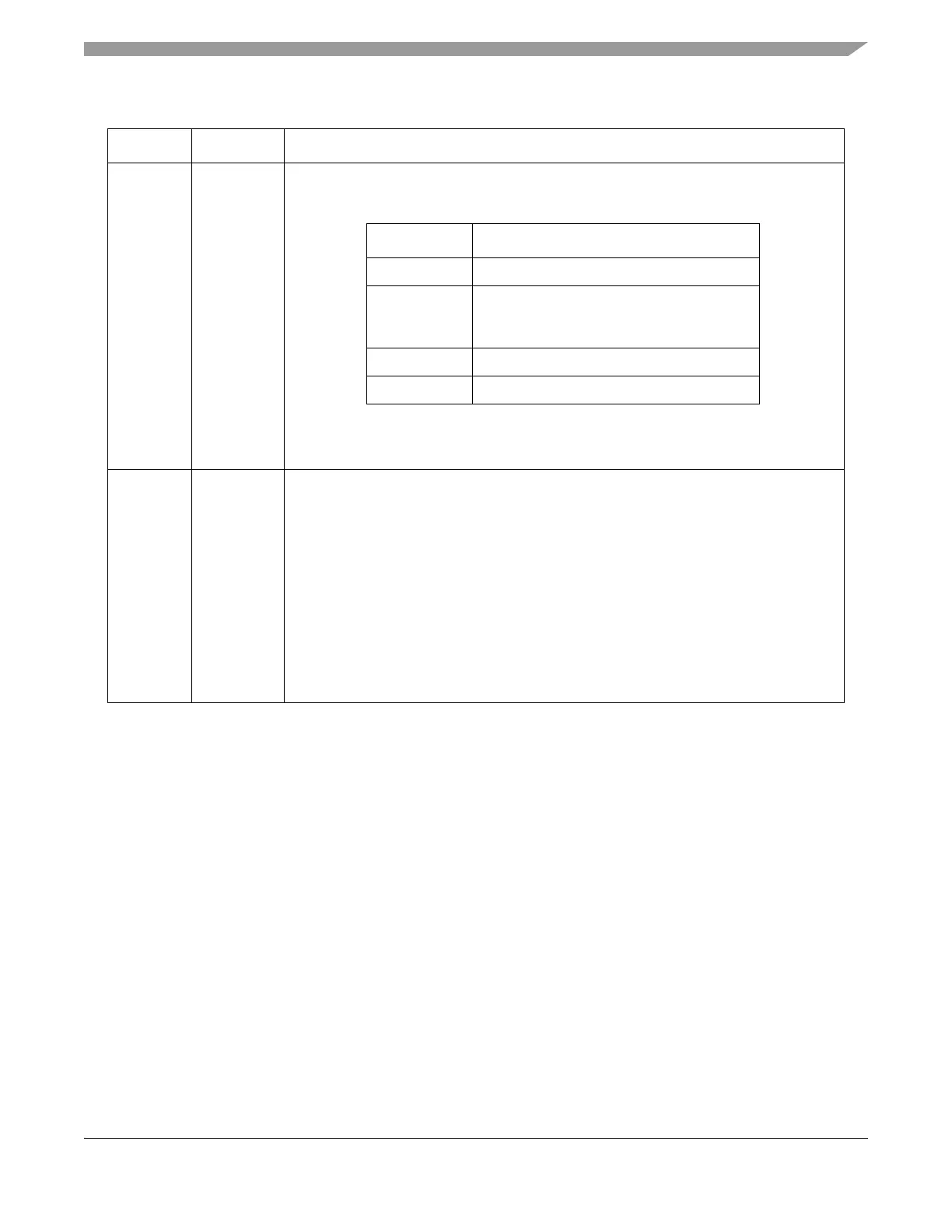

21–22 BSL

[0:1]

Bus select. Used to select either one of the counter buses or the internal counter to be used

by the unified channel.

Note: In certain modes the internal counter is used internally and therefore cannot be

used as the channel time base.

23 EDSEL Edge selection bit. For input modes, the EDSEL bit selects whether the internal counter is

triggered by both edges of a pulse or just by a single edge as defined by the EDPOL bit.

When not shown in the mode of operation description, this bit has no effect.

0 Single edge triggering defined by the EDPOL bit

1 Both edges triggering

For GPIO input mode, the EDSEL bit selects if a FLAG can be generated.

0 A FLAG is generated as defined by the EDPOL bit

1 No FLAG is generated

For SAOC mode, the EDSEL bit selects the behavior of the output flip-flop at each match.

0 The EDPOL value is transferred to the output flip-flop

1 The output flip-flop is toggled

Table 17-10. EMIOS_CCRn Field Description (Continued)

Bits Name Description

BSL[0:1] Selected Bus

00 All channels: counter bus[A]

01 Channels 0 to 7: counter bus[B]

Channels 8 to 15: counter bus[C]

Channels 16 to 23: counter bus[D]

10 Reserved

11 All channels: internal counter (see Note)

Loading...

Loading...