MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

17-18 Freescale Semiconductor

24 EDPOL Edge polarity.

For input modes (except QDEC and WPTA mode), the EDPOL bit asserts which edge

triggers either the internal counter or an input capture or a FLAG. When not shown in the

mode of operation description, this bit has no affect.

0 Trigger on a falling edge

1 Trigger on a rising edge

For WPTA mode, the internal counter is used as a time accumulator and counts up when

the input gating signal has the same polarity of EDPOL bit.

0 Counting occurs when the input gating signal is low

1 Counting occurs when the input gating signal is high

For QDEC (MODE[6] cleared), the EDPOL bit selects the count direction according to

direction signal (UCn input).

0 Counts down when UCn is asserted

1 Counts up when UCn is asserted

NOTE: UC[n-1] EDPOL bit selects which edge clocks the internal counter of UCn

0 Trigger on a falling edge

1 Trigger on a rising edge

For QDEC (MODE[6] set), the EDPOL bit selects the count direction according to the

phase difference.

0 Internal counter decrements if phase_A is ahead phase_B signal

1 Internal counter increments if phase_A is ahead phase_B signal

NOTE: In order to operate properly, EDPOL bit must contain the same value in UCn and

UC[n-1]

For output modes, the EDPOL bit is used to select the logic level on the output pin. When

software selects any output mode except GPIO, the initial state of the output flip-flop is the

complement of EDPOL.

0 A match on comparator A clears the output flip-flop, while a match on comparator B sets

it

1 A match on comparator A sets the output flip-flop, while a match on comparator B clears

it

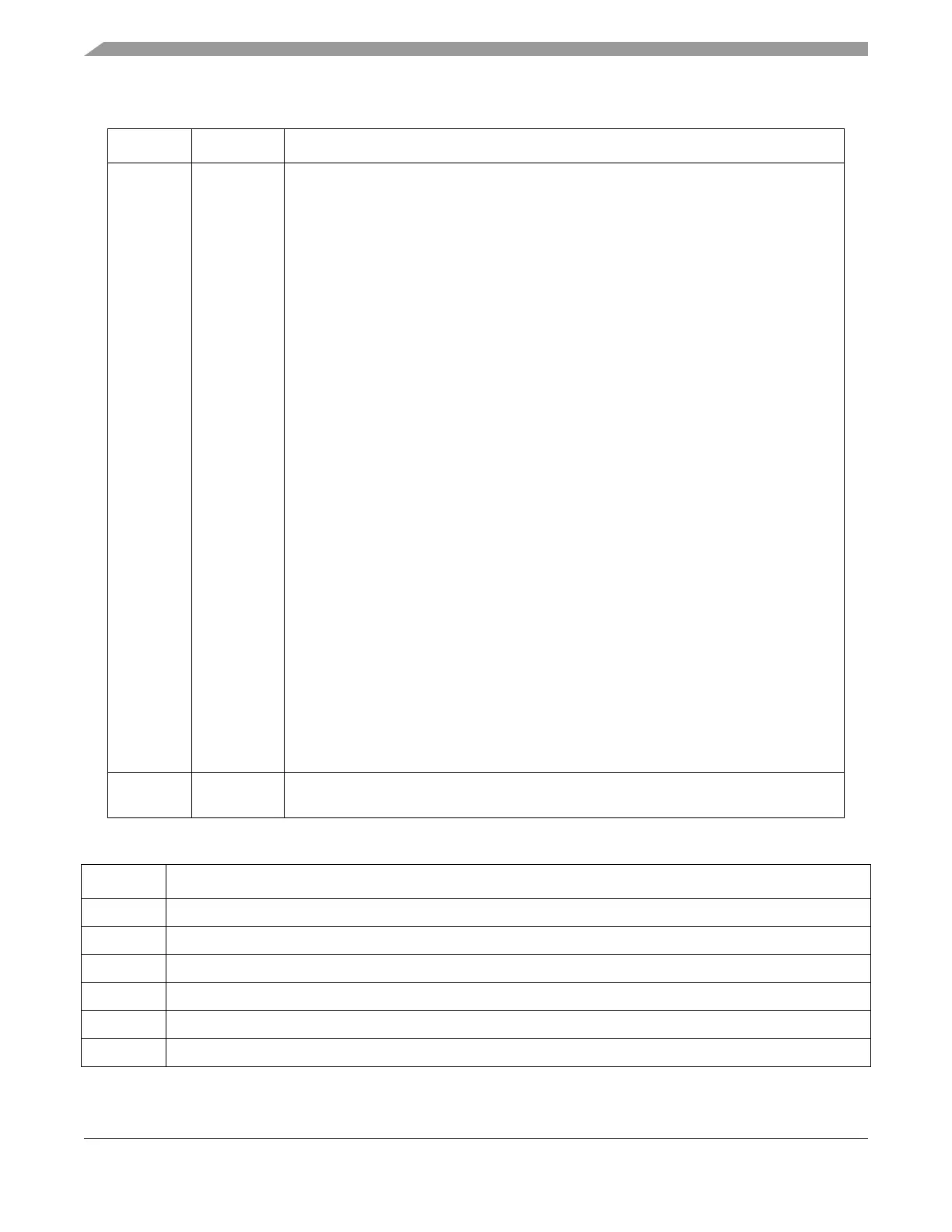

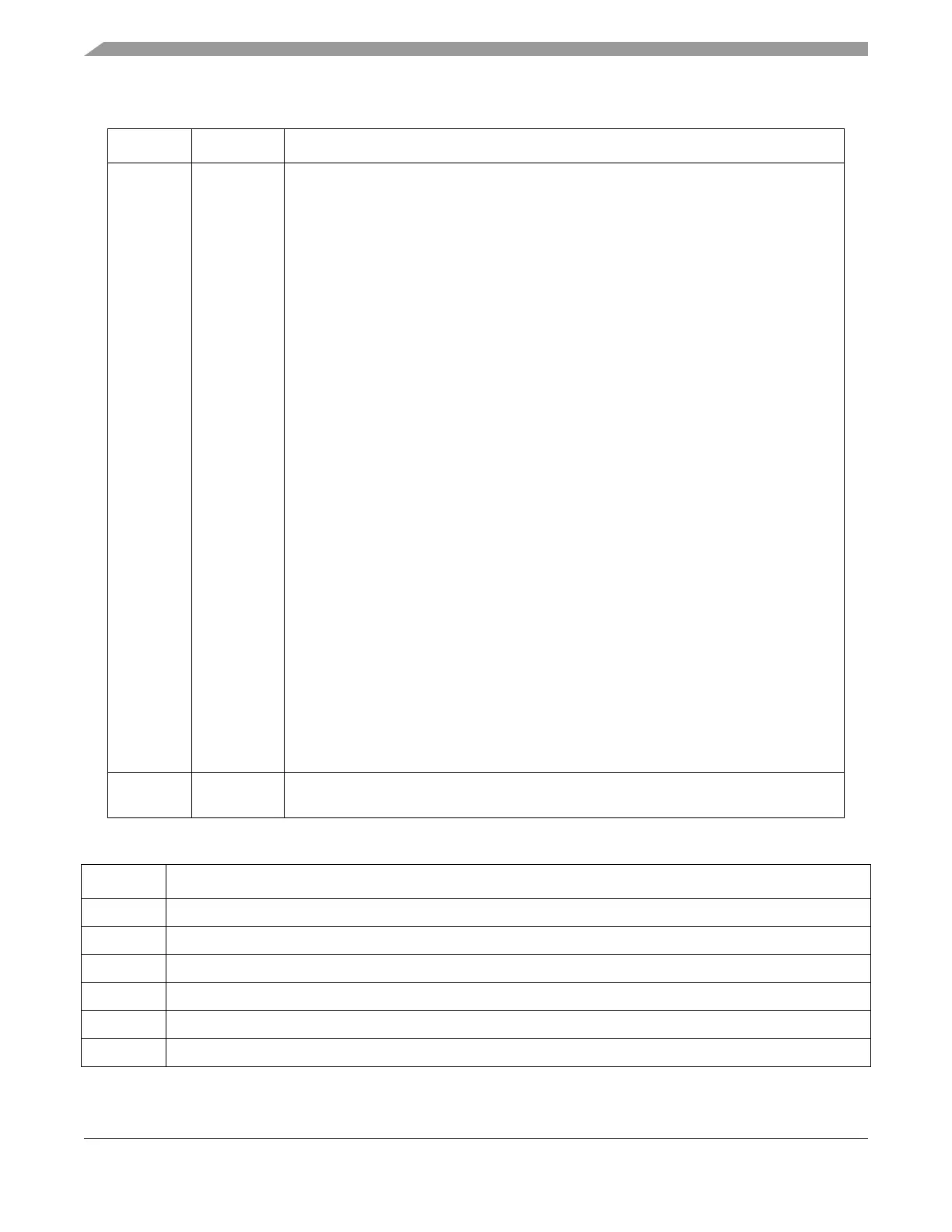

25–31 MODE

[0:6]

Mode selection. Selects the mode of operation of the unified channel, as shown in

Table 17-11.

Table 17-11. Unified Channel MODE Bits (Sheet 1 of 4)

MODE0:6] Unified Channel Mode of Operation

0000000 General purpose input/output mode (input)

0000001 General purpose input/output mode (output)

0000010 Single action input capture

0000011 Single action output compare

0000100 Input pulse width measurement

0000101 Input period measurement

Table 17-10. EMIOS_CCRn Field Description (Continued)

Bits Name Description

Loading...

Loading...