MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-26 Freescale Semiconductor

18.4.2.2 Time Base Registers

Time base registers allow the configuration and visibility of internally-generated time bases TCR1 and

TCR2. There is one of each of these registers for each eTPU engine.

NOTE

Writes to this register issue a bus error and are ineffective when MDIS=1.

Reads are always allowed.

18.4.2.2.1 eTPU Time Base Configuration Register (ETPU_TBCR)

This register configures several time base options.

18–26 — Reserved.

27–31 ETB

[0:4]

Entry table base. Determines the location of the microcode entry table for the eTPU

functions in SCM. More information about entry points is located in the eTPU reference

manual. The following table shows the entry table base address options.

1

The time base registers can still be read in stop mode, but writes are ineffective and a bus error is issued. Global

channel registers and SDM can be accessed normally.

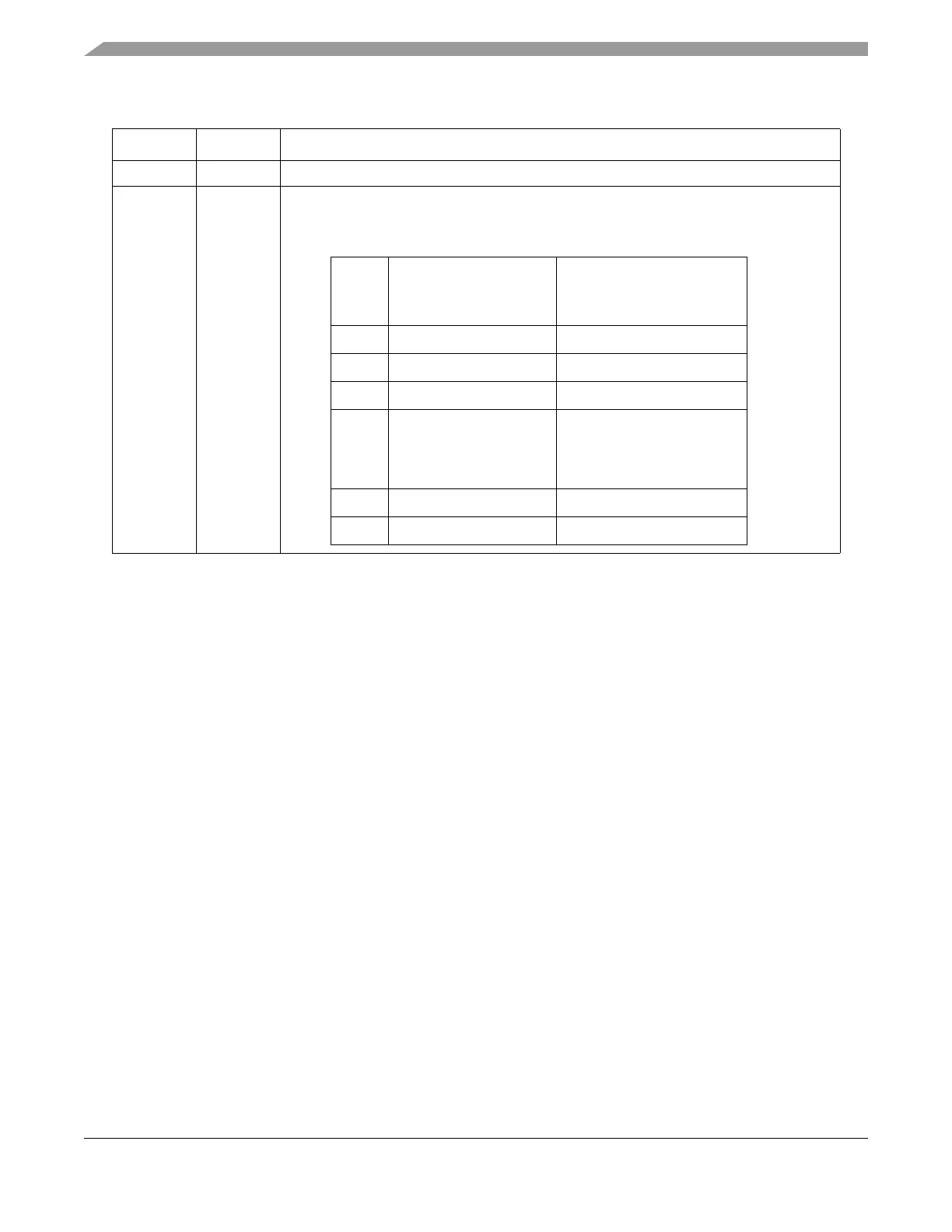

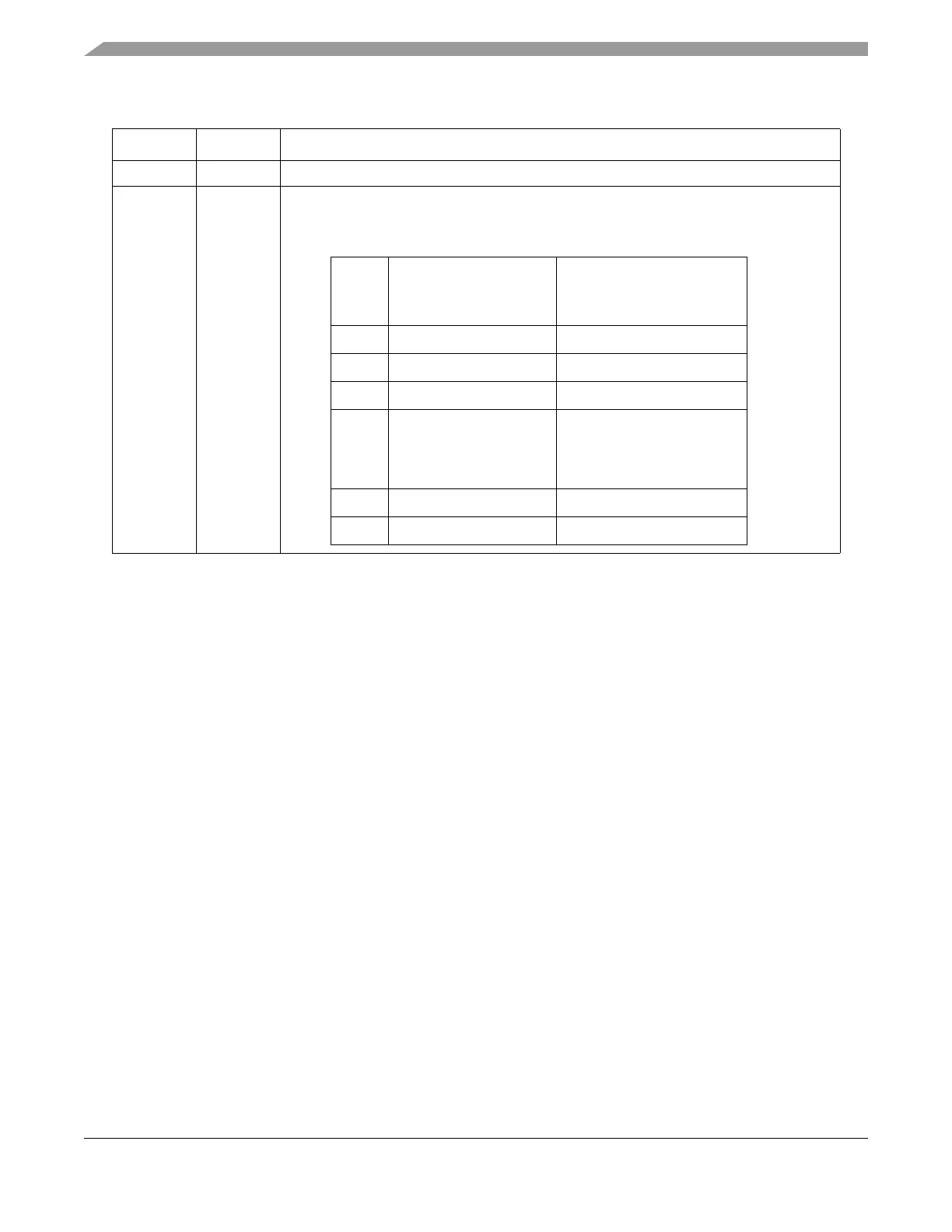

Table 18-11. ETPU_ECR Field Descriptions (Continued)

Bits Name Description

ETB

Entry Table Base

Address for CPU Host

Address (byte format)

Entry Table Base Address

for Microcode Address

(word format)

00000 0x0_0000 0x0_0000

00001 0x0_0800 0x0_0200

00010 0x0_1000 0x0_400

.

.

.

.

.

.

.

.

.

.

.

.

11110 0x0_F000 0x0_3C00

11111 0x0_F800 0x0_3E00

Loading...

Loading...