MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-28 Freescale Semiconductor

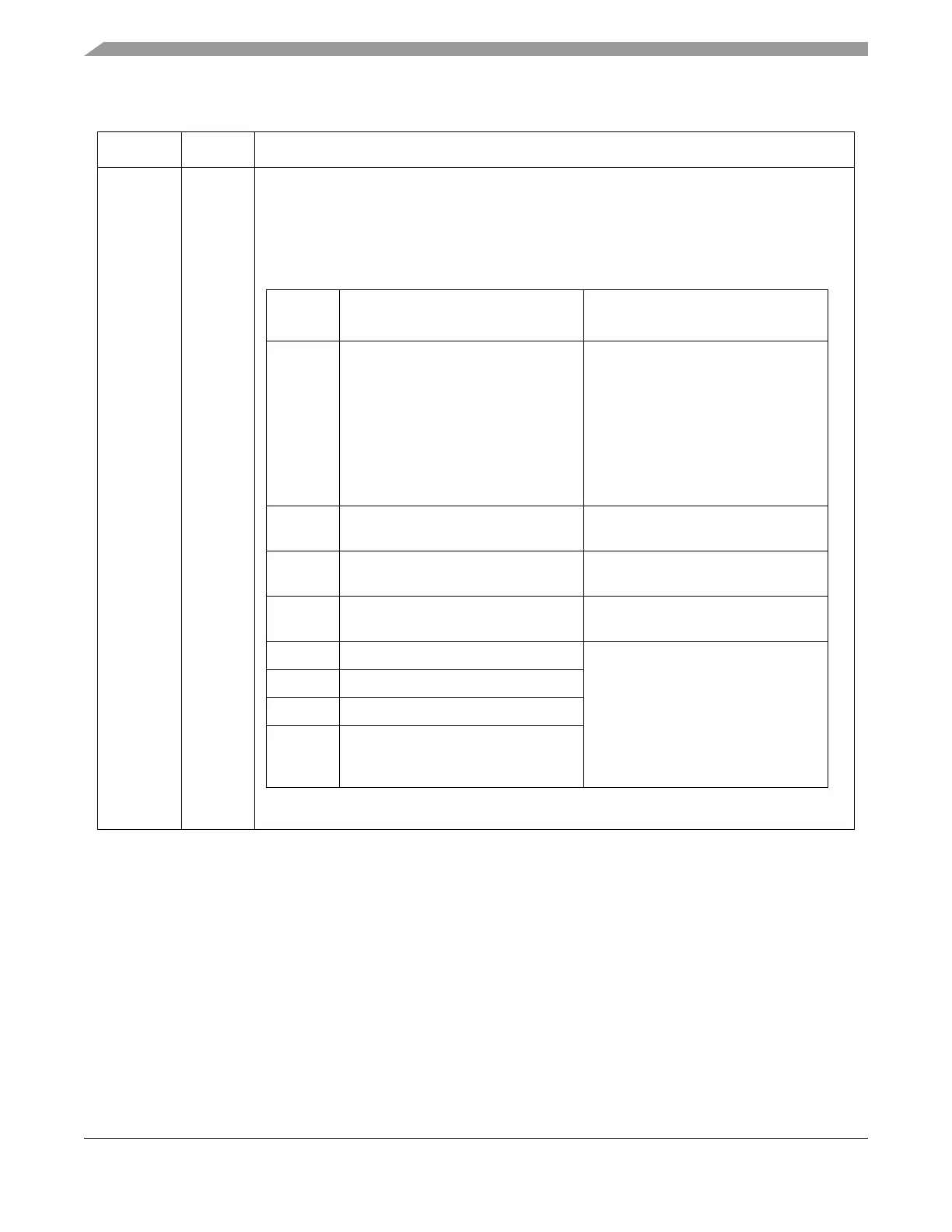

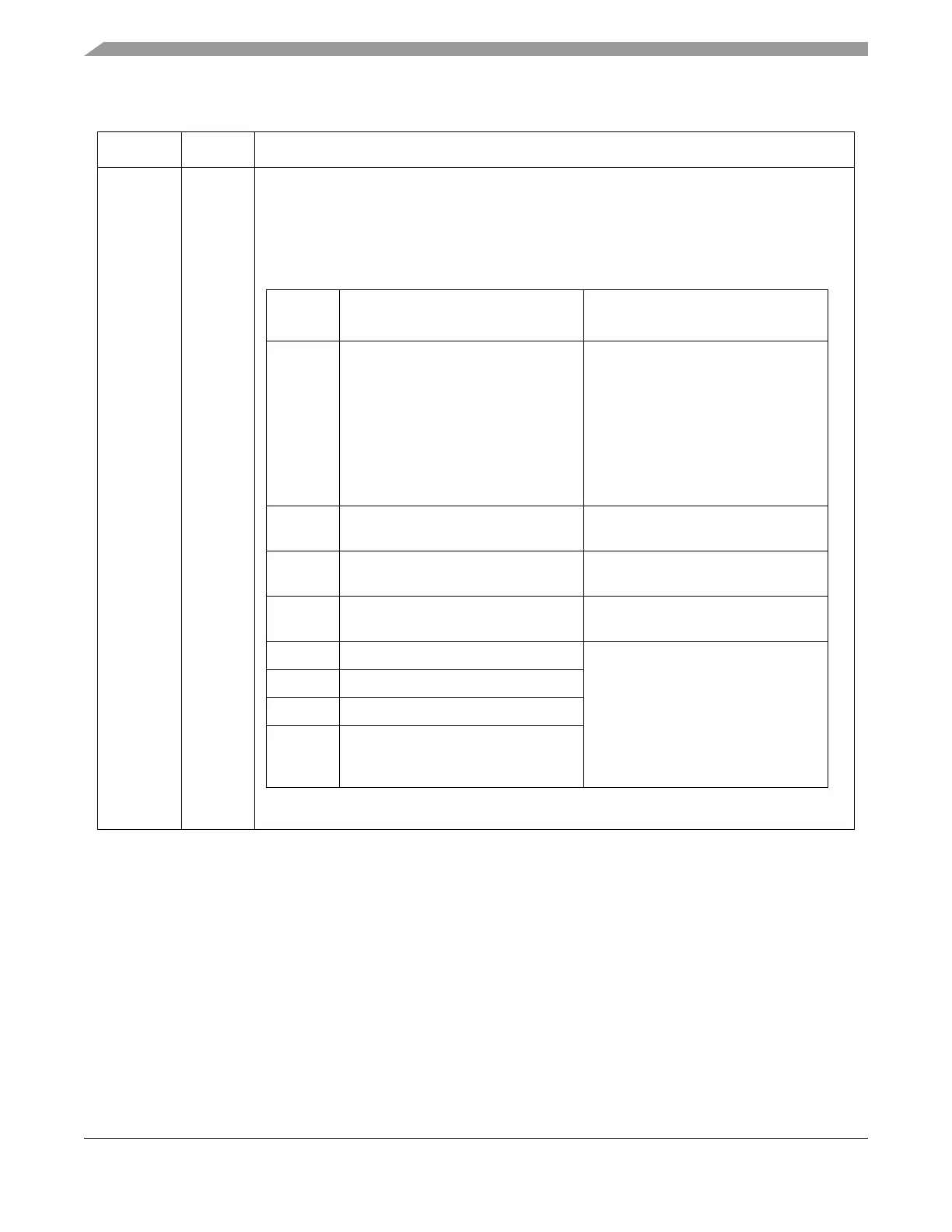

Table 18-12. ETPU_TBCR Field Descriptions

Bits Name Description

0–2 TCR2CTL TCR2 clock/gate control. Part of the TCR2 clocking system. These bits determine the clock

source for TCR2 before the prescaler. TCR2 can count on any detected edge of the TCRCLK

signal or use it for gating the system clock divided by 8. After reset, the TCRCLK signal rising

edge is selected. TCR2 can also be clocked by the system clock divided by 8. TCR2CTL also

determines the TCRCLK edge selected for angle tooth detection in angle mode. Refer to the

eTPU User’s Manual for more information. TCR2 clock sources are listed in the following table.

TCR2CTL

AM=0

(TCR2 Clock)

AM=1

(Angle Tooth Detection)

000 Gated DIV8 clock (system clock / 8).

When the external TCRCLK signal is

low, the DIV8 clock is blocked,

preventing it from incrementing the

TCR2 prescaler. When the external

TCRCLK signal is high, TCR2

prescaler is incremented at the

frequency of the system clock divided

by 8.

See Note

1

001 Rise transition on TCRCLK signal

increments TCR2 prescaler.

Rising Edge

010 Fall transition on TCRCLK signal

increments TCR2 prescaler.

Falling Edge

011 Rise or fall transition on TCRCLK

signal increments TCR2 prescaler.

Rising or Falling Edge

100 DIV8 clock (system clock / 8) See Note

1

101 Reserved

110 Reserved

111 TCR2CTL shuts down TCR2 clocking,

except on Angle Mode. TCR2 can also

change as STAC client.

1

These selections must not be used with AM=1 (Angle Mode).

Loading...

Loading...