MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-30 Freescale Semiconductor

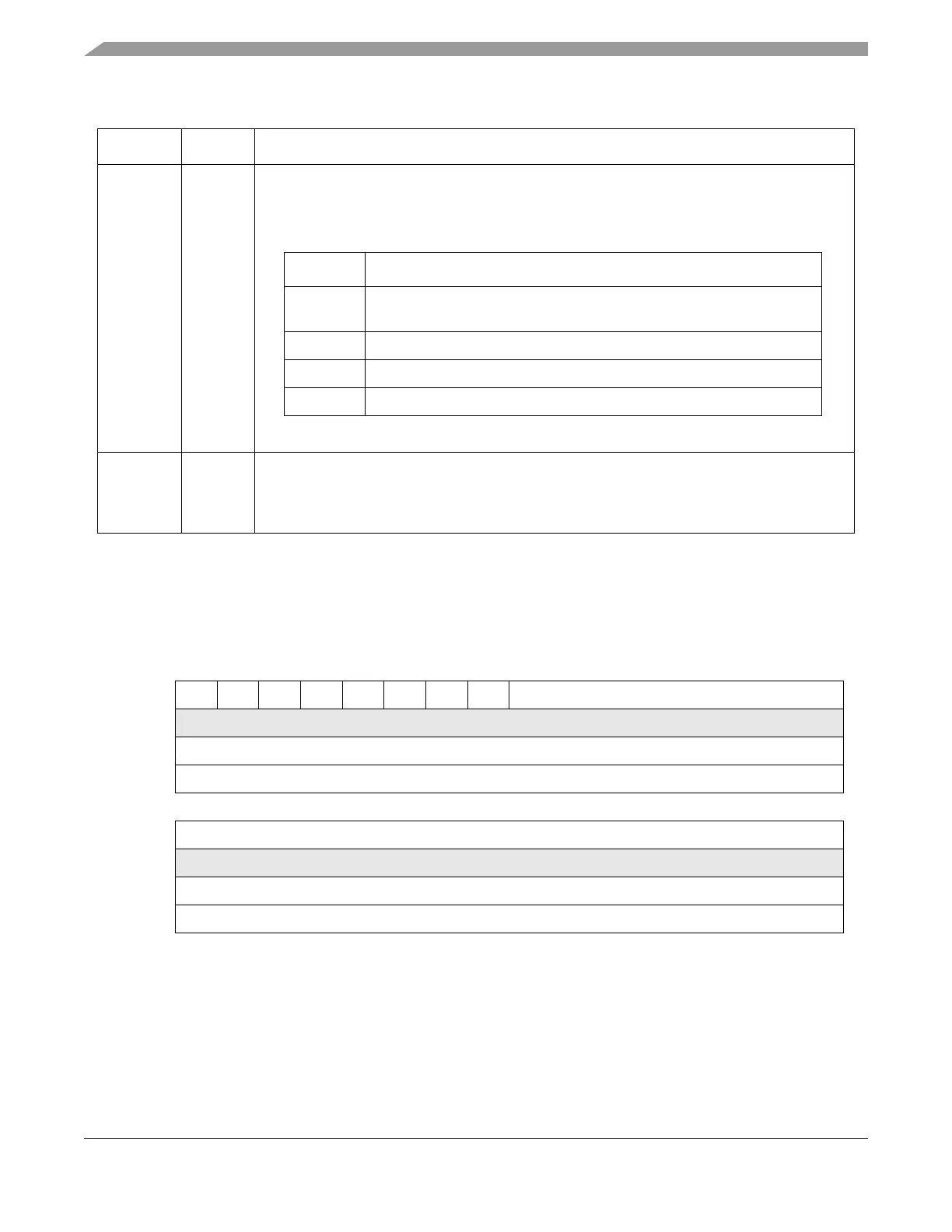

18.4.2.2.2 eTPU Time Base 1 (TCR1) Visibility Register (ETPU_TB1R)

This register provides visibility of the TCR1 time base for core host read access. This register is read-only.

The value of the TCR1 time base shown can be driven by the TCR1 counter or imported, depending on

the configuration set in ETPU_REDCR. For more information, refer to the eTPU reference manual.

16–23 TCR1CTL TCR1 clock/gate control. Part of the TCR1 clocking system. It determines the clock source for

TCR1. TCR1 can count on detected rising edge of the TCRCLK signal or the system clock divided

by 2. After reset TCRCLK signal is selected. The following table shows the selection of the TCR1

clock source.

For more information on the TCR1 clocking system, refer to the eTPU User’s Manual.

24–31 TCR1P Timer count register 1 prescaler control. Clocked from the output of a prescaler. The input to the

prescaler is the internal eTPU system clock divided by 2 or the output of TCRCLK filter, or

Peripheral Timebase input. The prescaler divides this input by (TCR1P+1) allowing frequency

divisions from 1 up to 256.

0123456789101112131415

R00000000 TCR1

W

Reset0000000000000000

Reg Addr eTPU A: Base + 0x0_0024 / eTPU B: Base + 0x0_0044

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RTCR1

W

Reset0000000000000000

Reg Addr eTPU A: Base + 0x0_0024 / eTPU B: Base + 0x0_0044

Figure 18-11. eTPU Time Base 1 (TCR1) Visibility Register (ETPU_TB1R)

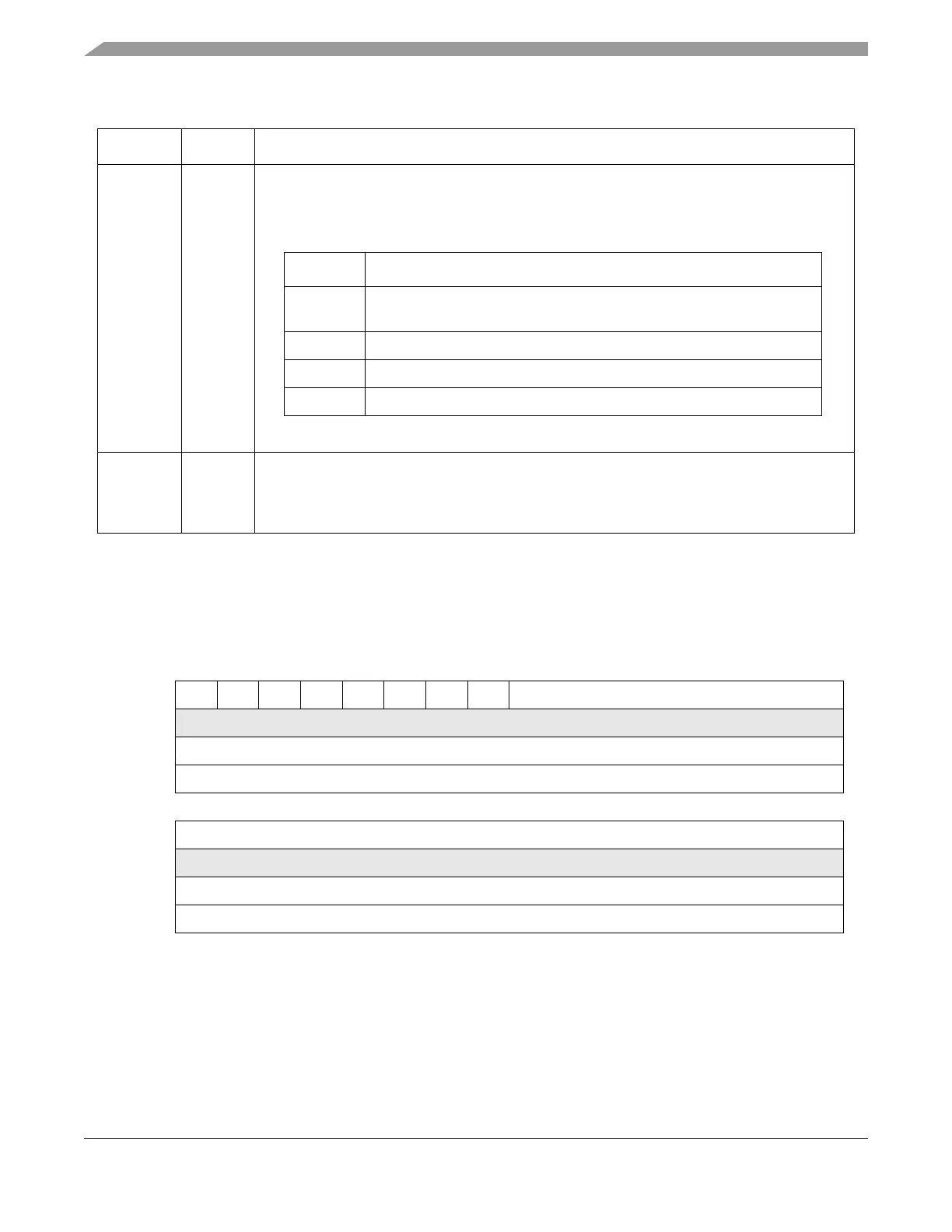

Table 18-12. ETPU_TBCR Field Descriptions (Continued)

Bits Name Description

TCR1CTL TCR1 Clock

00 selects TCRCLK as clock source for the TCR1 prescaler (must not be use

in Angle Mode)

01 reserved

10 selects system clock divided by 2 as clock source for the TCR1 prescaler

11 TCR1CTL shuts down TCR1 clock. TCR1 can still change if STAC client.

Loading...

Loading...