MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-41

There are 64 structures defined, one for each available channel in the eTPU System (32 for each engine).

The base address for the structure presented can be calculated by using the following equation:

Channel_Register_Structure_Base_Address =

ETPU_Engine_Channel_Base + (channel_number * 0x0_0010)

where:

ETPU_Engine_Channel_Base = ETPU_Base + (0x0_0400 for engine A or 0x0_0800 for

engine B).

18.4.2.4.2 eTPU Channel n Configuration Register (ETPU_CnCR)

The ETPU_CnCR is a collection of the configuration bits related to an individual channel. Some of these

bits are mirrored from the global channel registers.

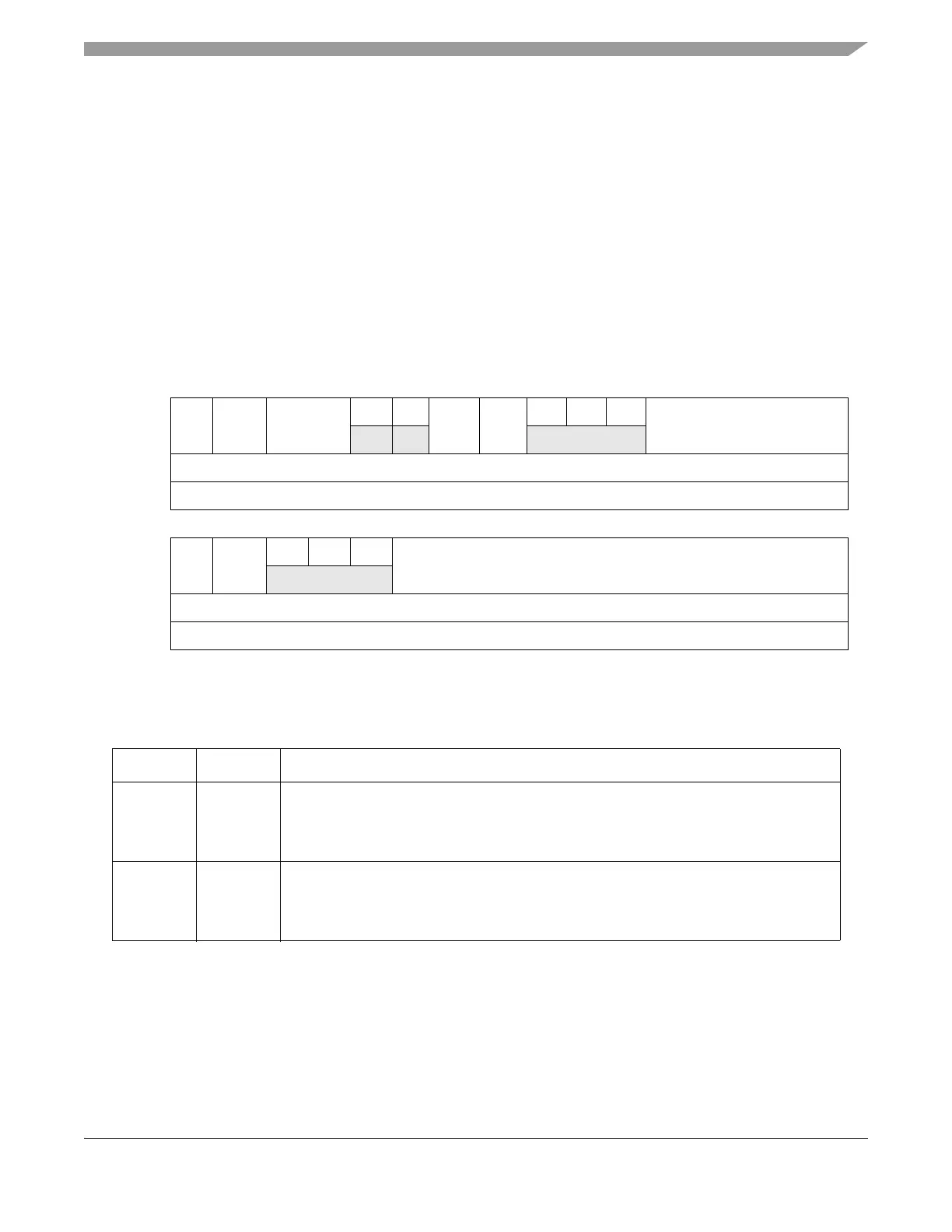

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R CIE DTRE CPR 0 0 ETPD

1

1

ETPD is only offered in the MPC5553.

ETCS 0 0 0 CFS

W

Reset0 0 0 000 0 0 00000000

Reg Addr Channel_Register_Base + 0x00

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R ODIS OPOL 0 0 0 CPBA

W

Reset0 0 0 000 0 0 00000000

Reg Addr Channel_Register_Base + 0x00

Figure 18-22. eTPU Channel n Configuration Register (ETPU_CnCR)

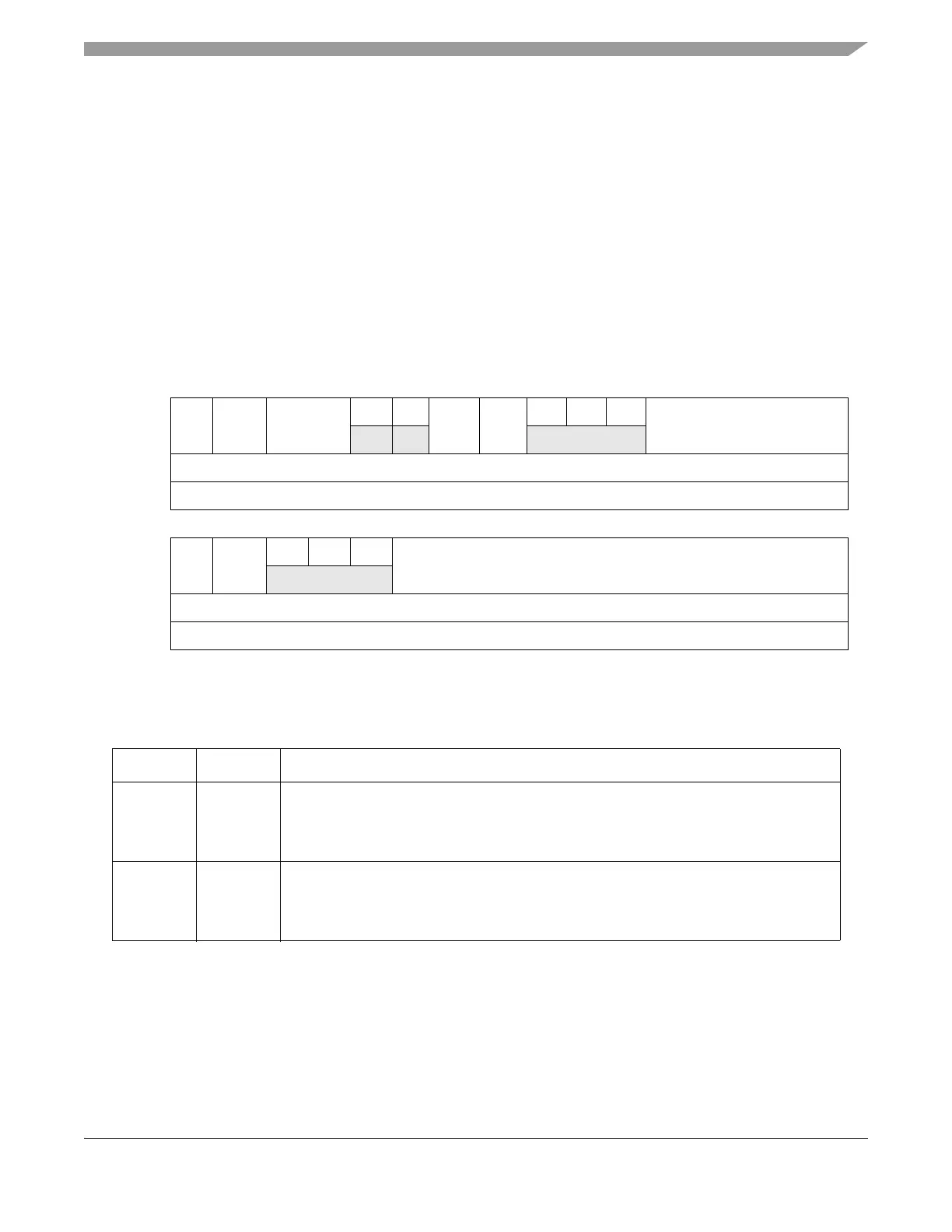

Table 18-26. ETPU_CnCR Field Descriptions

Bits Name Description

0 CIE Channel interrupt enable. This bit is mirrored from the ETPU_CIER

0 Disable interrupt for this channel.For more information, refer to the eTPU reference

manual.

1 Enable interrupt for this channel.

1 DTRE Channel data transfer request enable. This bit is mirrored from the ETPU_CDTRER.

0 Disable data transfer request for this channel.Refer to the eTPU reference manual for

more information.

1 Enable data transfer request for this channel.

Loading...

Loading...