MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-40 Freescale Semiconductor

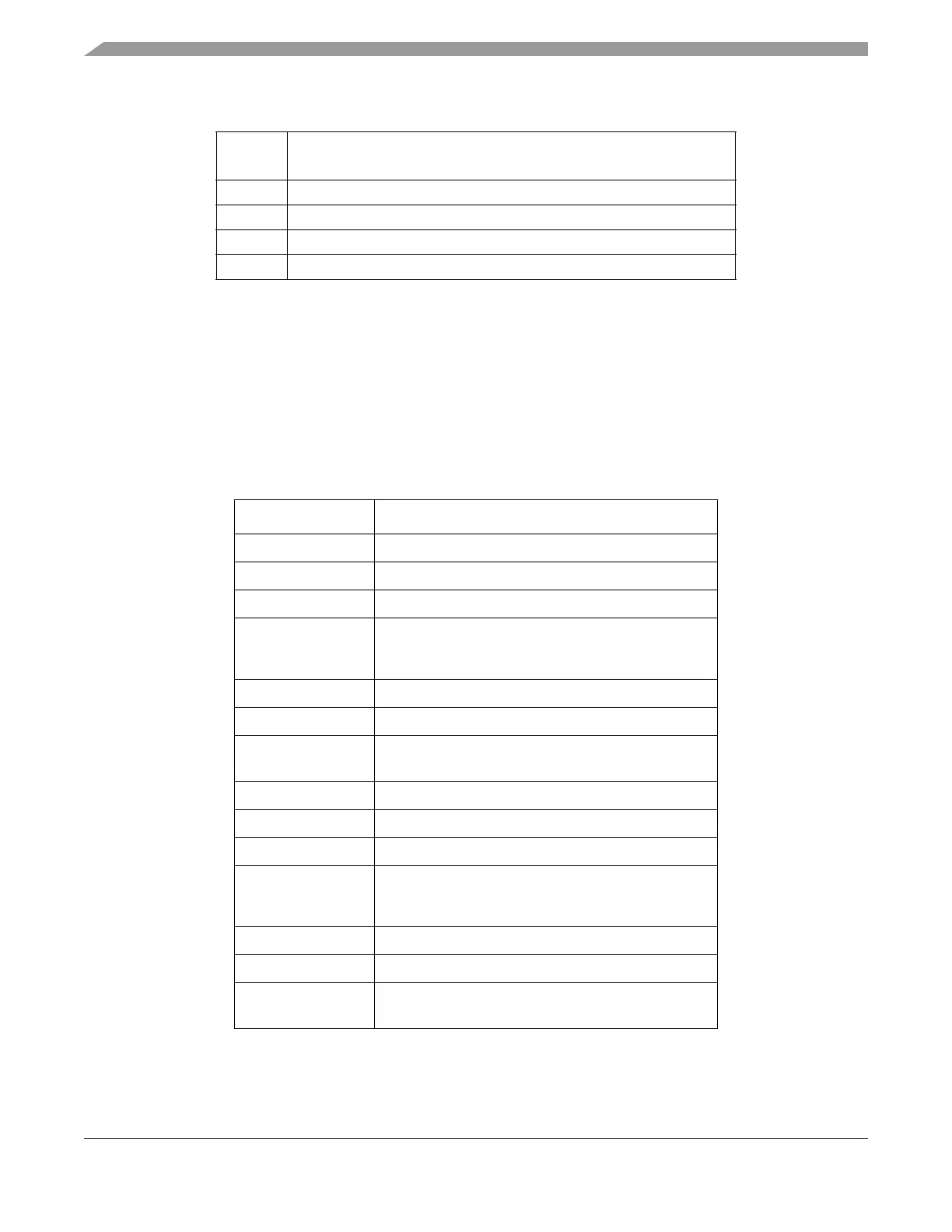

18.4.2.4.1 Channel Registers Layout

One contiguous area is used to map all channel registers of each eTPU engine as shown in Table 18-25.

Table 18-24. Channel Registers Structure

Channel

Offset

Register Name

0x00 eTPU channel configuration register (ETPU_CnCR)

0x04 eTPU channel status/control register

1

(ETPU_CnSCR)

1

In the MPC5554, eTPU A channels [0:2,12:15,28:29] and eTPU B channels

[0:3,12:15,28:31] are connected to the DMA; in the MPC5553, eTPU A channels

[0:2, 14:15] are connected. The data transfer request lines that are not connected

to the DMA controller are left disconnected and do not generate interrupt requests,

even if their request status bits assert in registers ETPU_CDTRSR and

ETPU_CnSCR

0x08 eTPU channel host service request register (ETPU_CnHSRR)

0x0C Reserved

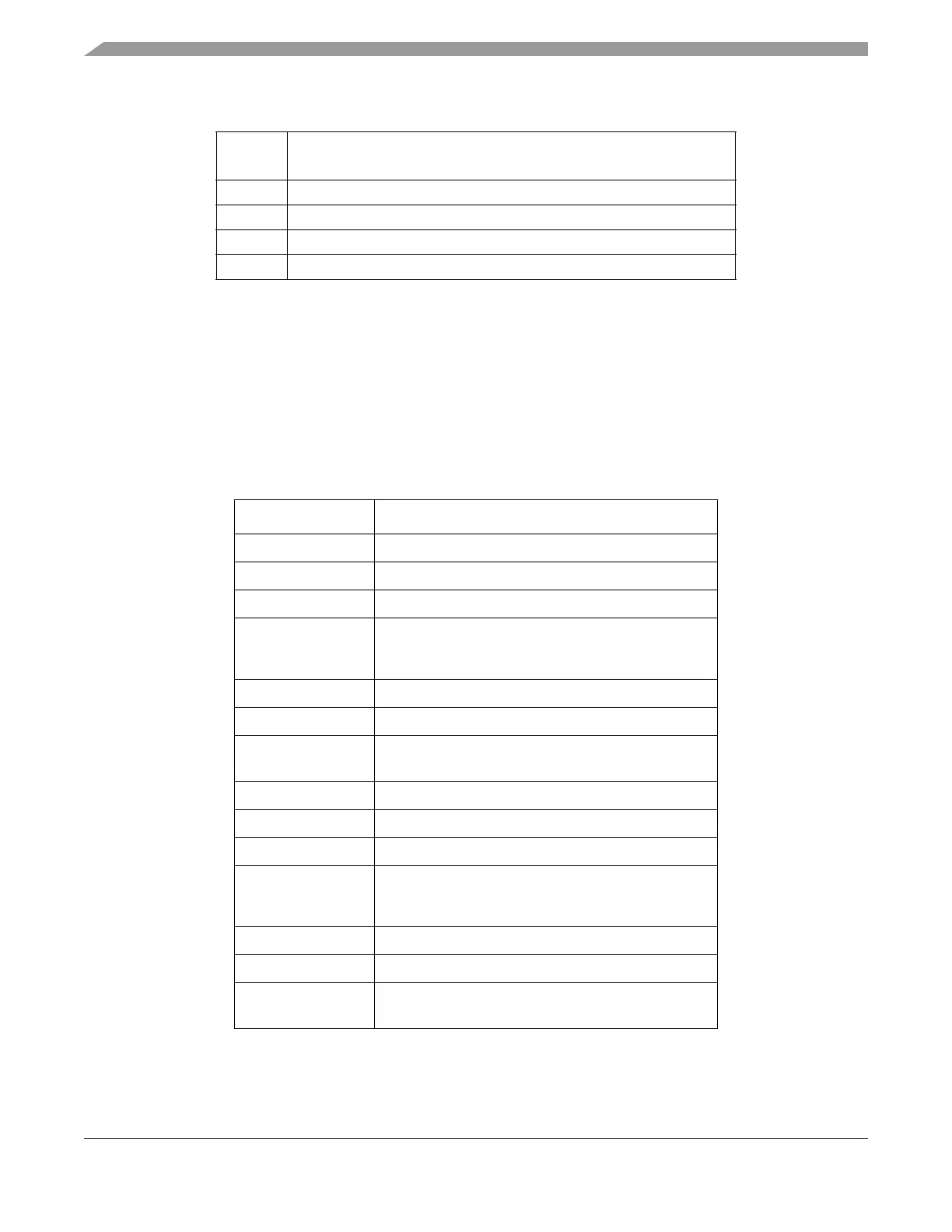

Table 18-25. eTPU Channel Register Map

Address Registers Structure

Base + 0x0_0400 eTPU A channel 0 register structure

Base + 0x0_0410 eTPU A channel 1 register structure

Base + 0x0_0420 eTPU A channel 2 register structure

Base + 0x0_0430–

Base + 0x0_05D0

.

.

.

Base + 0x0_05E0 eTPU A channel 30 register structure

Base + 0x0_05F0 eTPU A channel 31 register structure

Base + 0x0_0600–

Base + 0x0_07FF

Reserved

Base + 0x0_0800 eTPU B channel 0 register structure

Base + 0x0_0810 eTPU B channel 1 register structure

Base + 0x0_0820 eTPU B channel 2 register structure

Base + 0x0_0430–

Base + 0x0_05D0

.

.

.

Base + 0x0_09E0 eTPU B channel 30 register structure

Base + 0x0_09F0 eTPU B channel 31 register structure

Base + 0x0_0A0 –

Base + 0x0_0BFF

Reserved

Loading...

Loading...