MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-43

18.4.2.4.3 eTPU Channel n Status Control Register (ETPU_CnSCR)

ETPU_CnSCR is a collection of the interrupt status bits of the channel, and also the function mode

definition (read-write). Bits CIS, CIOS, DTRS, and DTROS for each channel can also be accessed from

ETPU_CISR, ETPU_CIOSR, ETPU_CDTRSR, and ETPU_CDTROSR respectively. For more

information on the three previously mentioned registers, refer to the eTPU reference manual.

NOTE

The MPC5553/MPC5554 core must write 1 to clear a status bit.

NOTE

In the MPC5554, eTPU A channels [0:2,12:15,28:29] and eTPU B channels

[0:3,12:15,28:31] are connected to the DMA; in the MPC5553, eTPU A

channels [0:2, 14:15] are DMA connected. The data transfer request lines

that are not connected to the DMA controller are left disconnected and do

not generate transfer requests, even if their request status bits assert in

registers ETPU_CDTRSR and ETPU_CnSCR

18–20 — Reserved.

21–31 CPBA

[0:10]

Channel n parameter base address. The value of this field multiplied by 8 specifies the

SDM parameter base host (byte) address for channel n (2-parameter granularity).

The formula for calculating the absolute channel parameter base (byte) address, as seen

by the host, is eTPU_Base + 0x8000 + CPBA*8. The SDM is mirrored in the parameter

sign extension (PSE) area. The formula to calculate the absolute channel parameter base

(byte) address in the PSE area is eTPU_Base + 0xC000 + CPBA*8.

For more information on SDM addresses, refer to the eTPU reference manual.

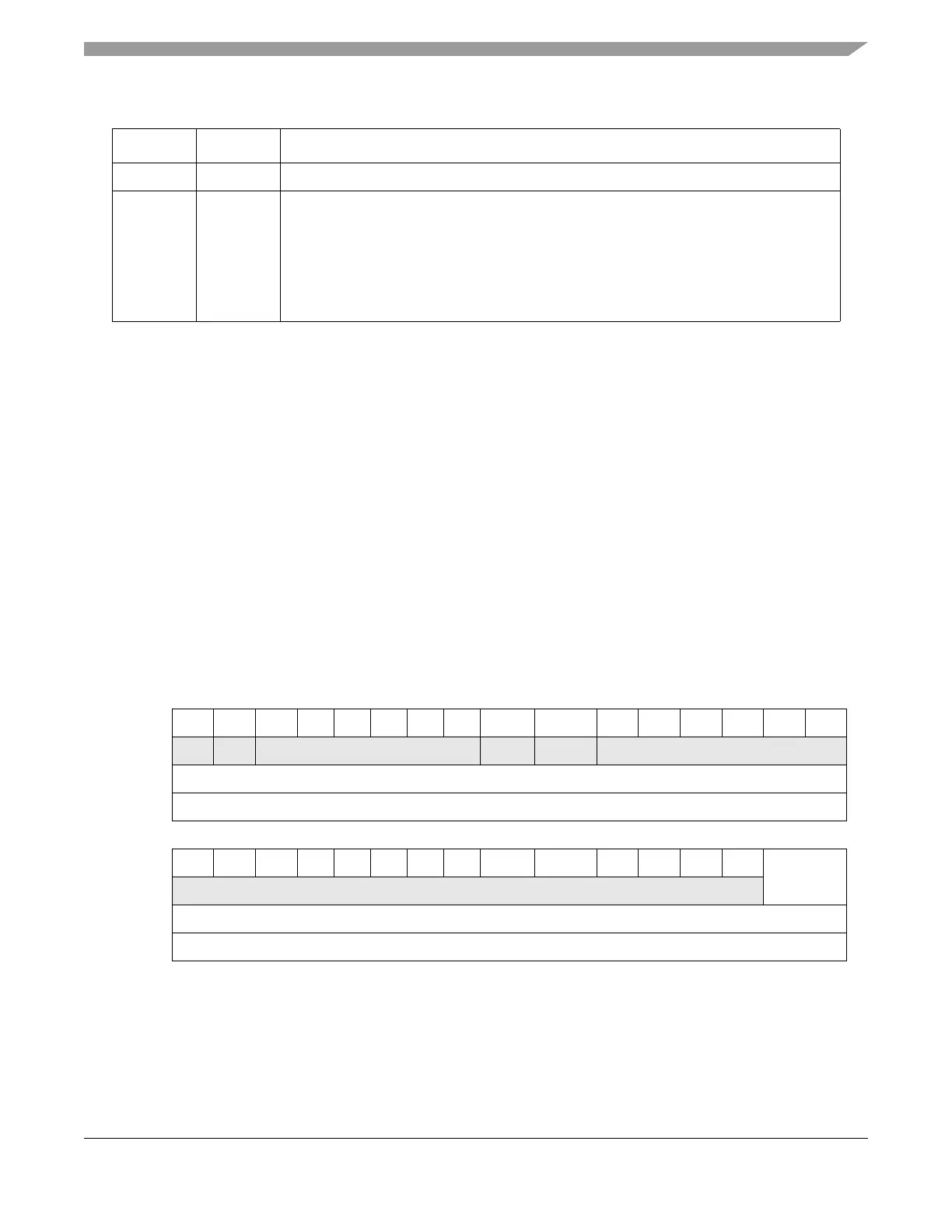

0 1 2 34567 8 9 101112131415

RCISCIOS0 00000DTRSDTROS0 0 0 0 0 0

W w1c w1c w1c w1c

Reset0 0 0 00000 0 0 0 0 0 0 0 0

Reg Addr Channel_Register_Base + 0x04

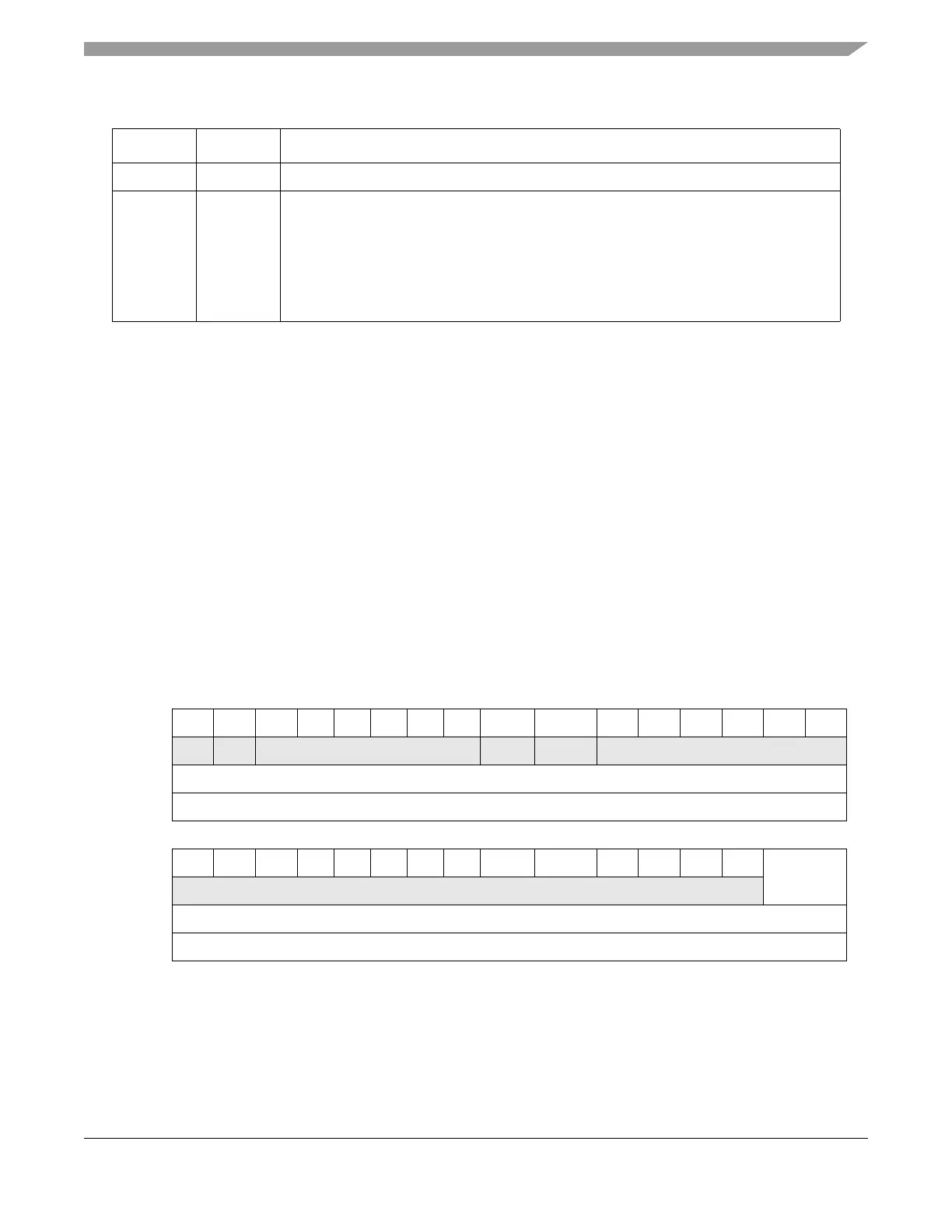

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RIPSOPS0 00000 0 0 0 0 0 0 FM

W

Reset0 0 0 00000 0 0 0 0 0 0 0 0

Reg Addr Channel_Register_Base + 0x04

Figure 18-23. eTPU Channel n Status Control Register (ETPU_CnSCR)

Table 18-26. ETPU_CnCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...