MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-44 Freescale Semiconductor

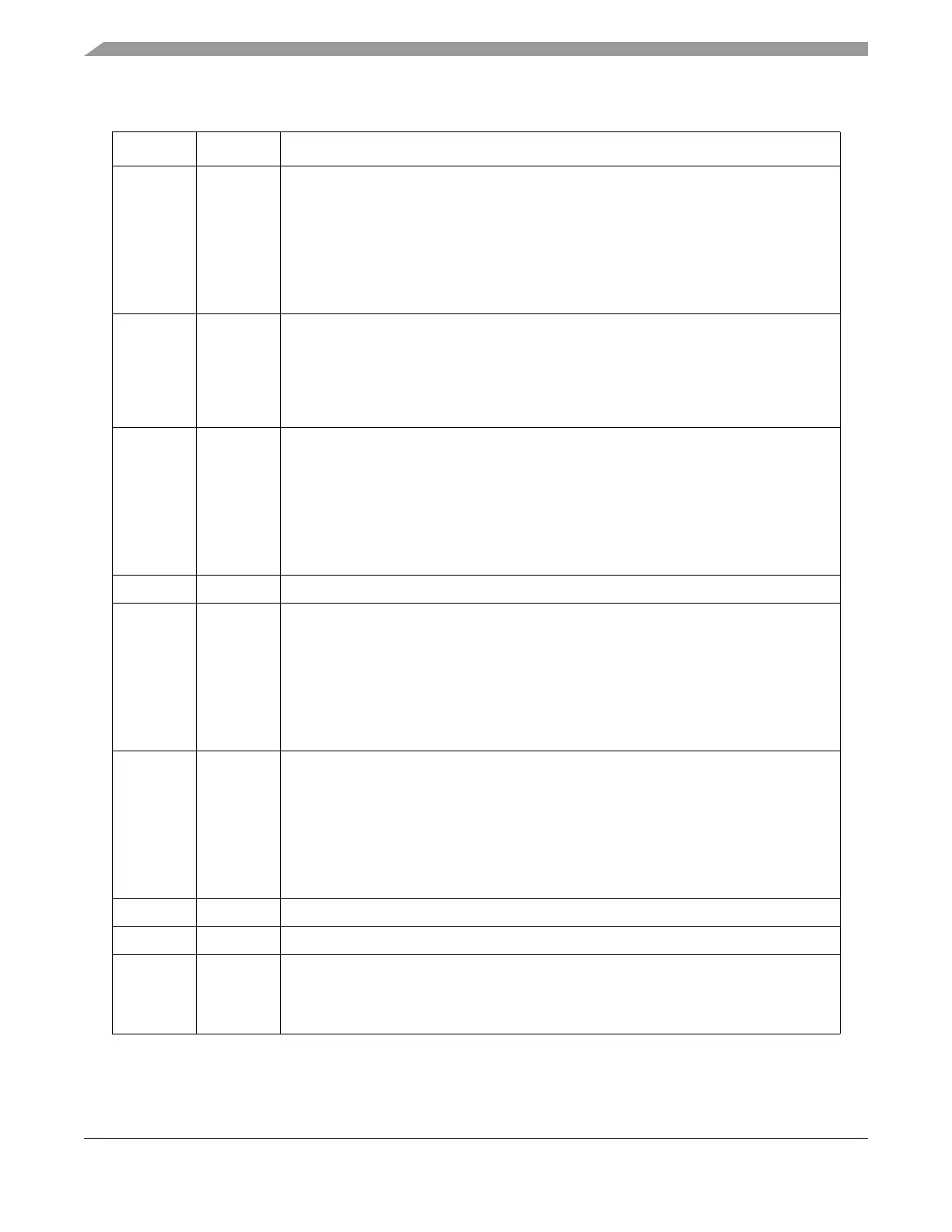

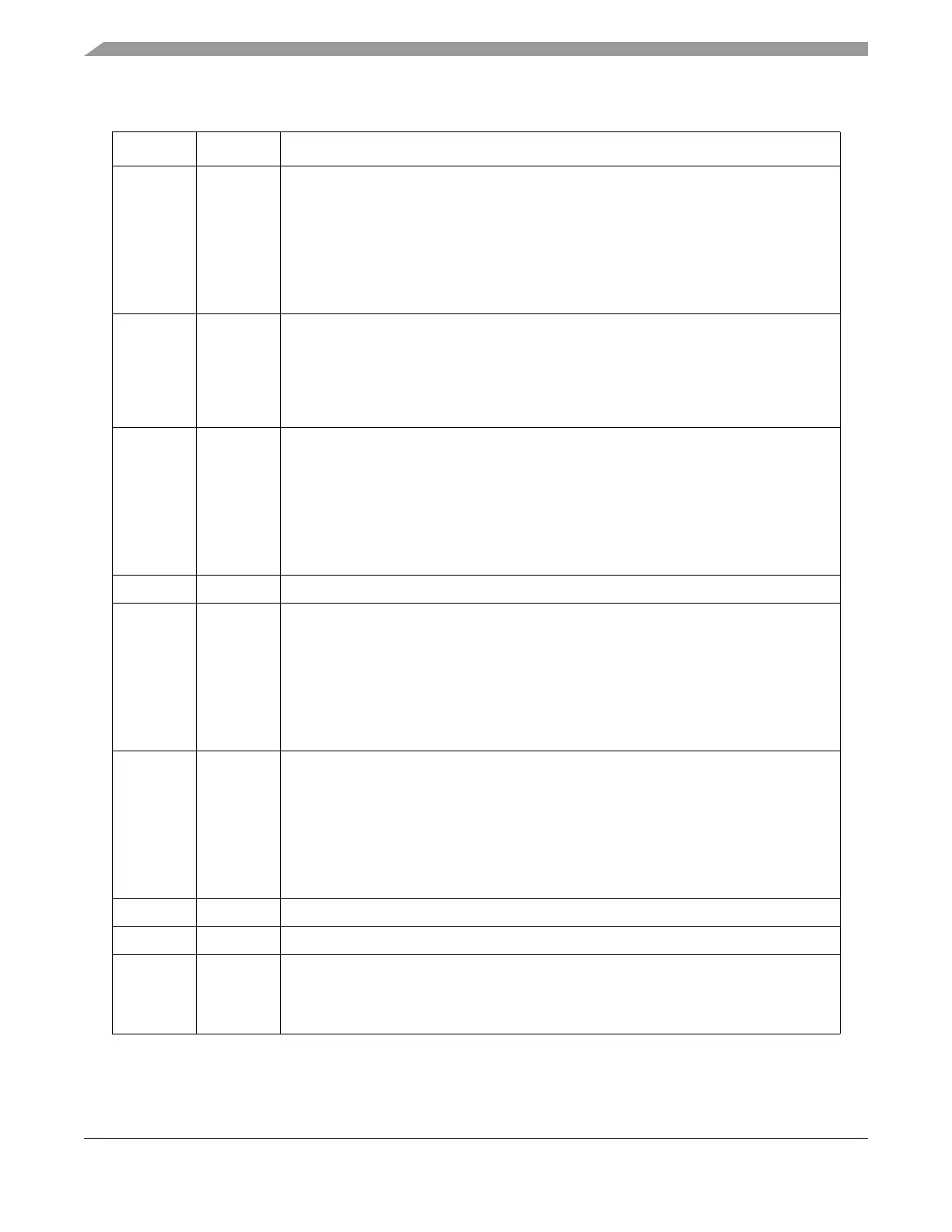

Table 18-27. ETPU_CnSCR Field Descriptions

Bits Name Description

0 CIS Channel interrupt status.

0 Channel has no pending interrupt to the MPC5553

/MPC5554 core.

1 Channel has a pending interrupt to the MPC5553

/MPC5554 core.

CIS is mirrored in the ETPU_CISR. For more information on ETPU_CISR and interrupts,

see Section 18.4.2.3.1, “eTPU Channel Interrupt Status Register (ETPU_CISR),” and the

eTPU reference manual.

The core must write 1 to clear CIS.

0 CIC Channel interrupt clear.

0 Keep interrupt status bit unaltered.

1 Clear interrupt status bit.

CIS and CIC are mirrored in the ETPU_CISR. For more information on ETPU_CISR and

interrupts, see Section 18.4.2.3.1, “eTPU Channel Interrupt Status Register

(ETPU_CISR),” and eTPU reference manual.

1 CIOS Channel interrupt overflow status.

0 Interrupt overflow negated for this channel

1 Interrupt overflow asserted for this channel

CIOS is mirrored in the ETPU_CIOSR. For more information on the ETPU_CIOSR and

interrupt overflow, see Section 18.4.2.3.3, “eTPU Channel Interrupt Overflow Status

Register (ETPU_CIOSR).” and the eTPU reference manual.

The core must write 1 to clear CIOS.

2–7 — Reserved.

8 DTRS Data transfer request status.

0 Channel has no pending data transfer request.

1 Channel has a pending data transfer request.

DTRS is mirrored in the ETPU_CISR. For more information on the ETPU_CISR and data

transfer, see Section 18.4.2.3.2, “eTPU Channel Data Transfer Request Status Register

(ETPU_CDTRSR).” and the eTPU reference manual.

The core must write 1 to clear DTRS.

9 DTROS Data transfer request overflow status.

0 Data transfer request overflow negated for this channel.

1 Data transfer request overflow asserted for this channel.

DTROS is mirrored in the ETPU_CDTROSR. See Section 18.4.2.3.4, “eTPU Channel

Data Transfer Request Overflow Status Register (ETPU_CDTROSR).” and the eTPU

reference manual for more information on ETPU_CDTROSR and data transfer overflows.

The core must write 1 to clear DTROS.

10–15 — Reserved.

16 IPS Channel input pin state. Shows the current value of the filtered channel input signal state

17 OPS Channel output pin state. Shows the current value driven in the channel output signal,

including the effect of the external output disable feature. If the channel input and output

signals are connected to the same pad, OPS reflects the value driven to the pad. This is

not necessarily the actual pad value, which drives the value in the IPS bit.

Loading...

Loading...