MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-35

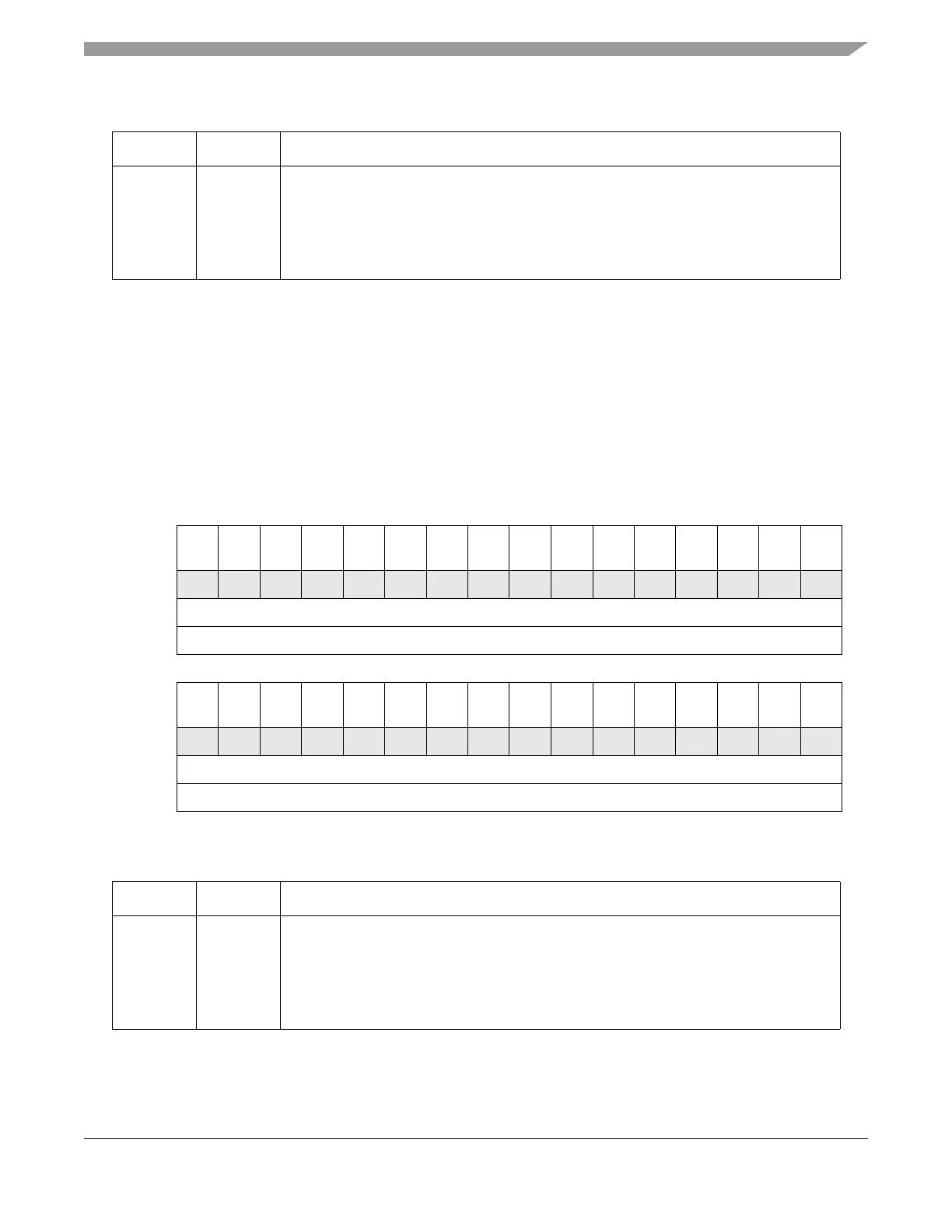

18.4.2.3.3 eTPU Channel Interrupt Overflow Status Register (ETPU_CIOSR)

An interrupt overflow occurs when an interrupt is issued for a channel when the previous interrupt status

bit for the same channel has not been cleared. Interrupt overflow status from all channels are grouped in

ETPU_CIOSR. The bits are mirrored by the channels’ status/control registers. For information about

channel status registers and overflow, refer to Section 18.4.2.4.3, “eTPU Channel n Status Control

Register (ETPU_CnSCR),” and the eTPU reference manual.

NOTE

The host must write 1 to clear an interrupt overflow status bit.

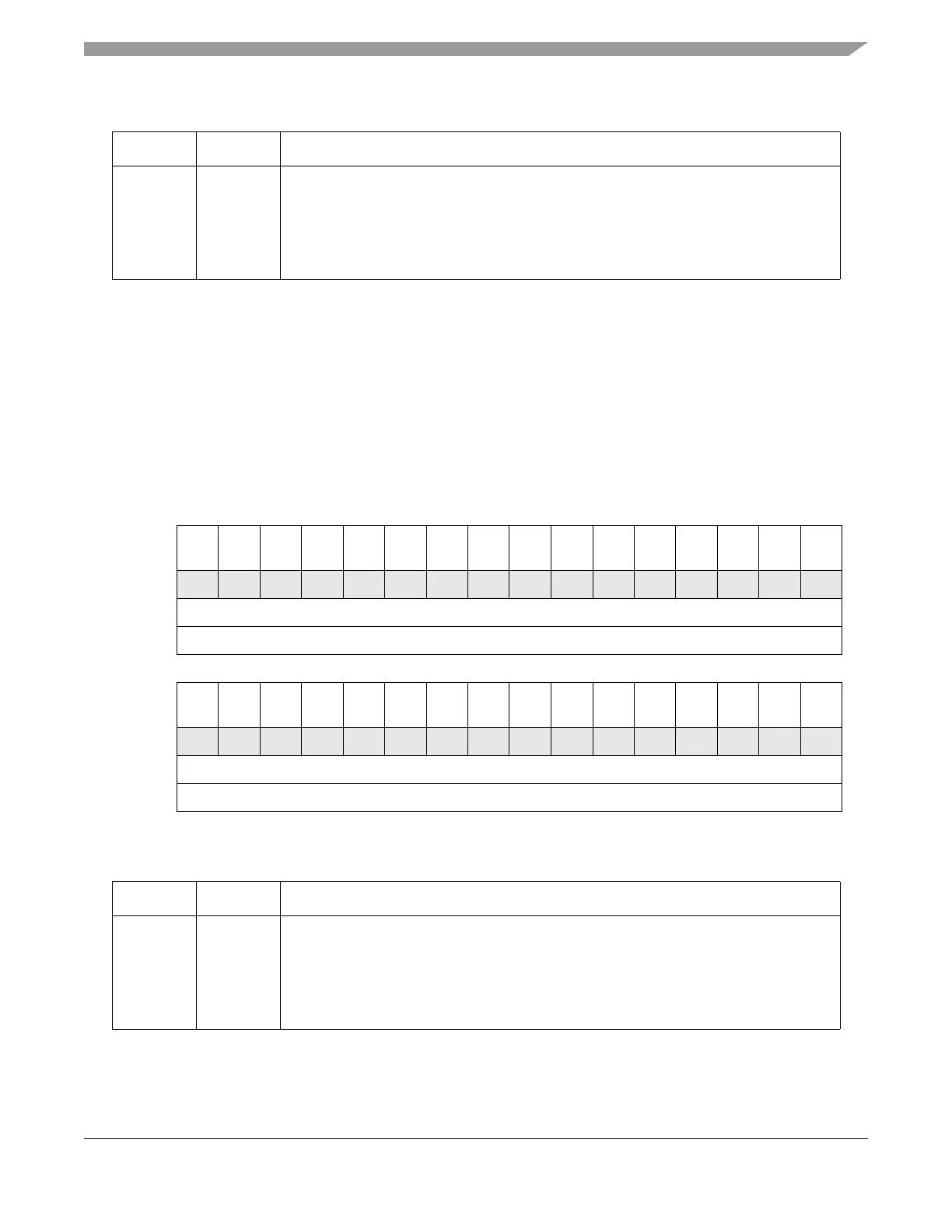

Table 18-17. ETPU_CDTRSR Field Descriptions

Bits Name Description

0–31 DTRSn Channel n data transfer request status.

0 Indicates that channel n has no pending data transfer request.

1 Indicates that channel n has a pending data transfer request.

To clear a status bit, the host must write 1 to it.

For details about data transfer requests refer to the eTPU reference manual.

0123456789101112131415

R CIOS

31

CIOS

30

CIOS

29

CIOS

28

CIOS

27

CIOS

26

CIOS

25

CIOS

24

CIOS

23

CIOS

22

CIOS

21

CIOS

20

CIOS

19

CIOS

18

CIOS

17

CIOS

16

W w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr eTPU A: Base + 0x0_0220 / eTPU B: Base + 0x0_0224

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R CIOS

15

CIOS

14

CIOS

13

CIOS

12

CIOS

11

CIOS

10

CIOS

9

CIOS

8

CIOS

7

CIOS

6

CIOS

5

CIOS

4

CIOS

3

CIOS

2

CIOS

1

CIOS

0

W w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr eTPU A: Base + 0x0_0220 / eTPU B: Base + 0x0_0224

Figure 18-16. eTPU Channel Interrupt Overflow Status Register (ETPU_CIOSR)

Table 18-18. ETPU_CIOSR Field Descriptions

Bits Name Description

0–31 CIOSn Channel n interrupt overflow status.

0 indicates that no interrupt overflow occurred in the channel.

1 indicates that an interrupt overflow occurred in the channel.

To clear a status bit, the host must write 1 to it.

For details about interrupts refer to the eTPU reference manual.

Loading...

Loading...