MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-33

18.4.2.3 Global Channel Registers

The registers in this section group, by type, the interrupt status and enable bits from all the channels. This

organization eases management of all channels or groups of channels by a single interrupt handler routine.

These bits are mirrored by the individual channel registers.

18.4.2.3.1 eTPU Channel Interrupt Status Register (ETPU_CISR)

Host interrupt status from all channels are grouped in ETPU_CISR. The bits are mirrored by the channels’

status/control registers. For more information, refer to Section 18.4.2.4.3, “eTPU Channel n Status Control

Register (ETPU_CnSCR),” and the eTPU reference manual.

NOTE

The host core must write 1 to clear an interrupt status bit.

20–23 SERVER_ID

2

STAC bus address for TCR2 as a server.

For more information on the STAC interface, see Section Table 17-13., “STAC Client

Submodule Server Slot Assignment.

24–27 — Reserved.

28–31 SRV2

[0:3]

TCR2 resource server. Selects the address of the specific STAC server the local TCR2

listens to when configured as a STAC Client. For more information on the STAC interface,

refer to the eTPU reference manual.

1

Resource identifies any parameter that changes in time and can be exported / imported from other device. For the

eTPU, a resource can be TCR1 or TCR2 (either time or angle values).

2

When TCR2 is configured as a STAC bus client (REN2 = 1, RSC2 = 0) the angle clock hardware must be disabled

(ETPU_TBCR[AM] = 0).

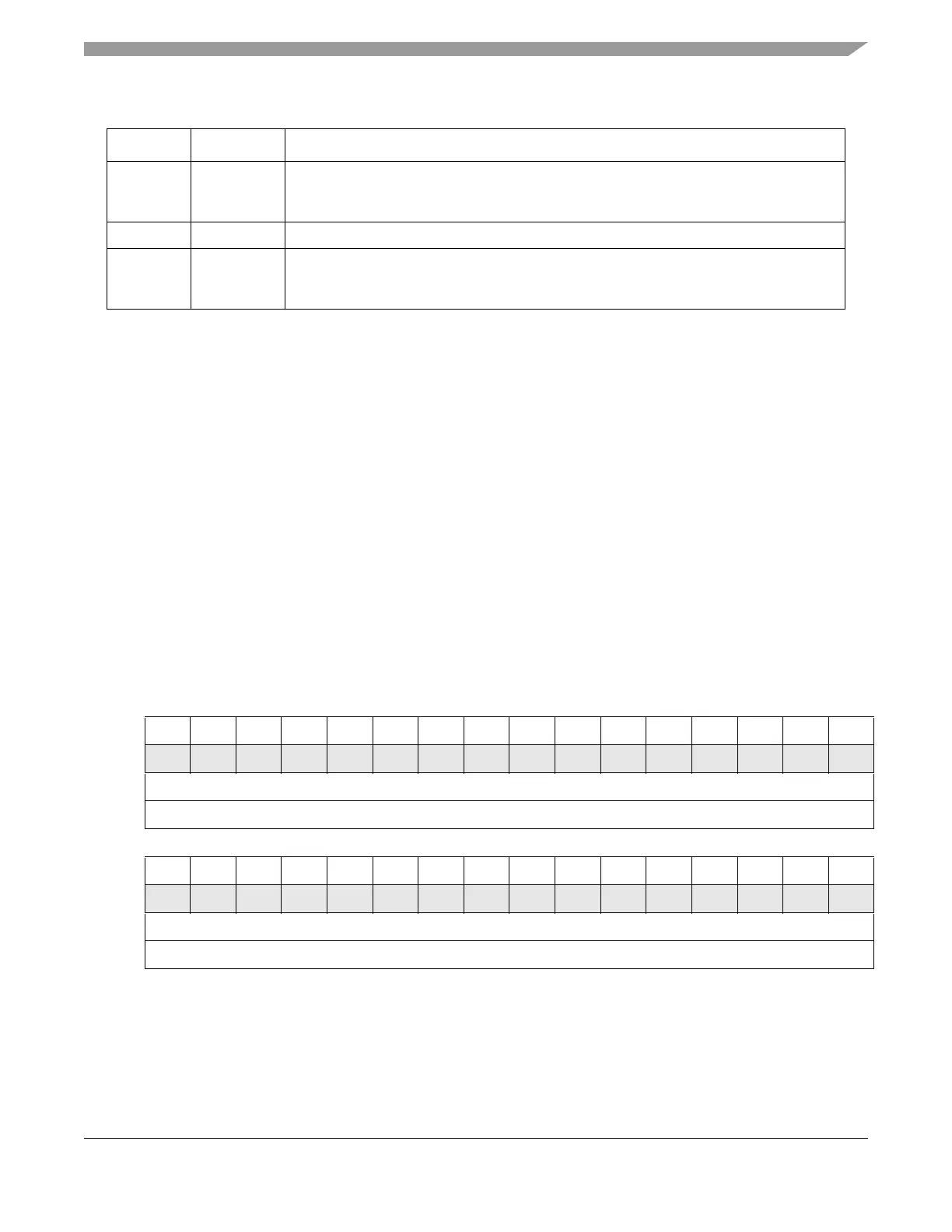

0 1 2 3 4 5 6 7 8 9 101112131415

R CIS31 CIS30 CIS29 CIS28 CIS27 CIS26 CIS25 CIS24 CIS23 CIS22 CIS21 CIS20 CIS19 CIS18 CIS17 CIS16

W w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr eTPU A: Base + 0x0_0200 / eTPU B: Base + 0x0_0204

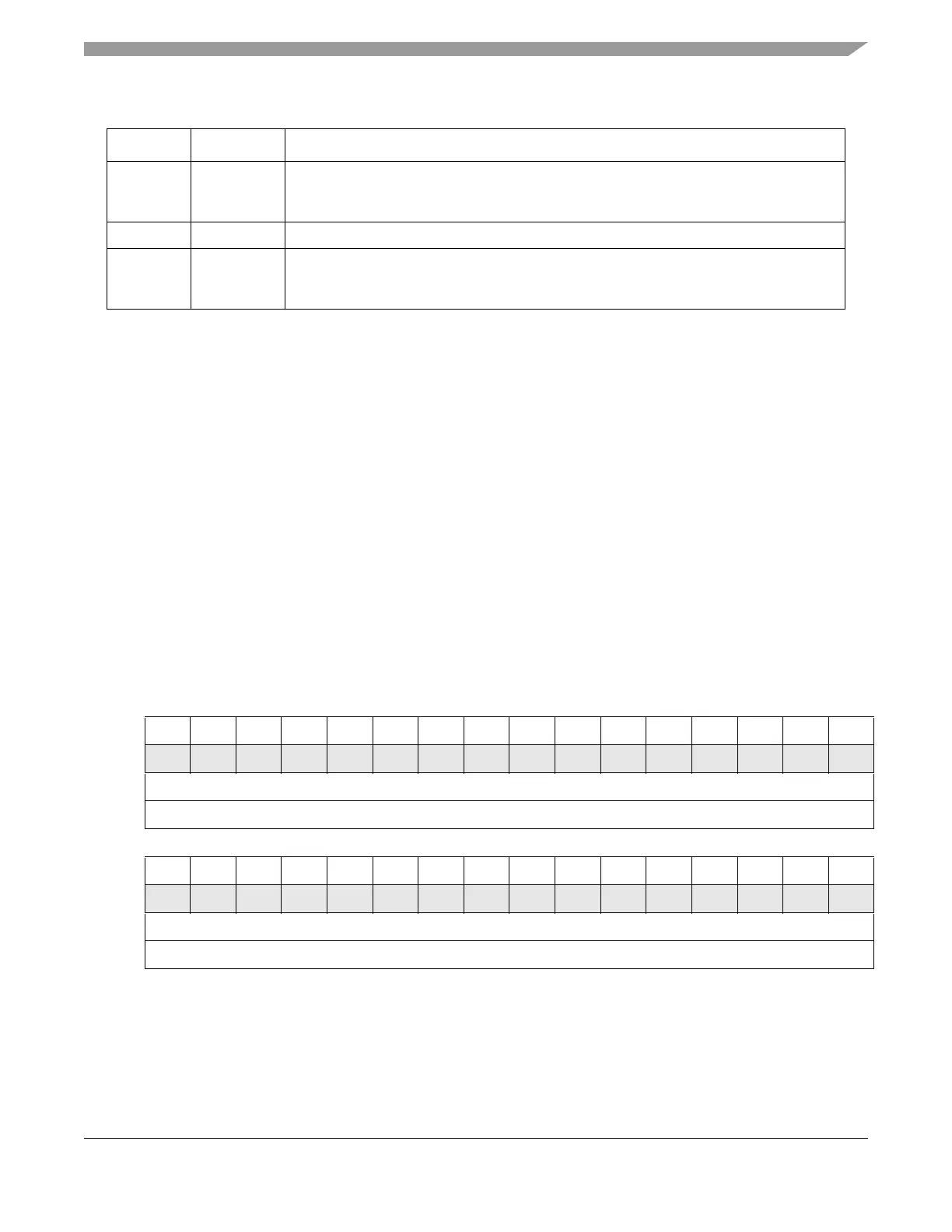

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R CIS15 CIS14 CIS13 CIS12 CIS11 CIS10 CIS9 CIS8 CIS7 CIS6 CIS5 CIS4 CIS3 CIS2 CIS1 CIS0

W w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0000000000000000

Reg Addr eTPU A: Base + 0x0_0200 / eTPU B: Base + 0x0_0204

Figure 18-14. eTPU Channel Interrupt Status Register (ETPU_CISR)

Table 18-15. ETPU_REDCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...