MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-18 Freescale Semiconductor

19.3.2.6 eQADC CFIFO Control Registers 0–5 (EQADC_CFCRn)

The eQADC_CFCRs contain bits that affect CFIFOs. These bits specify the CFIFO operation mode and

can invalidate all of the CFIFO contents.

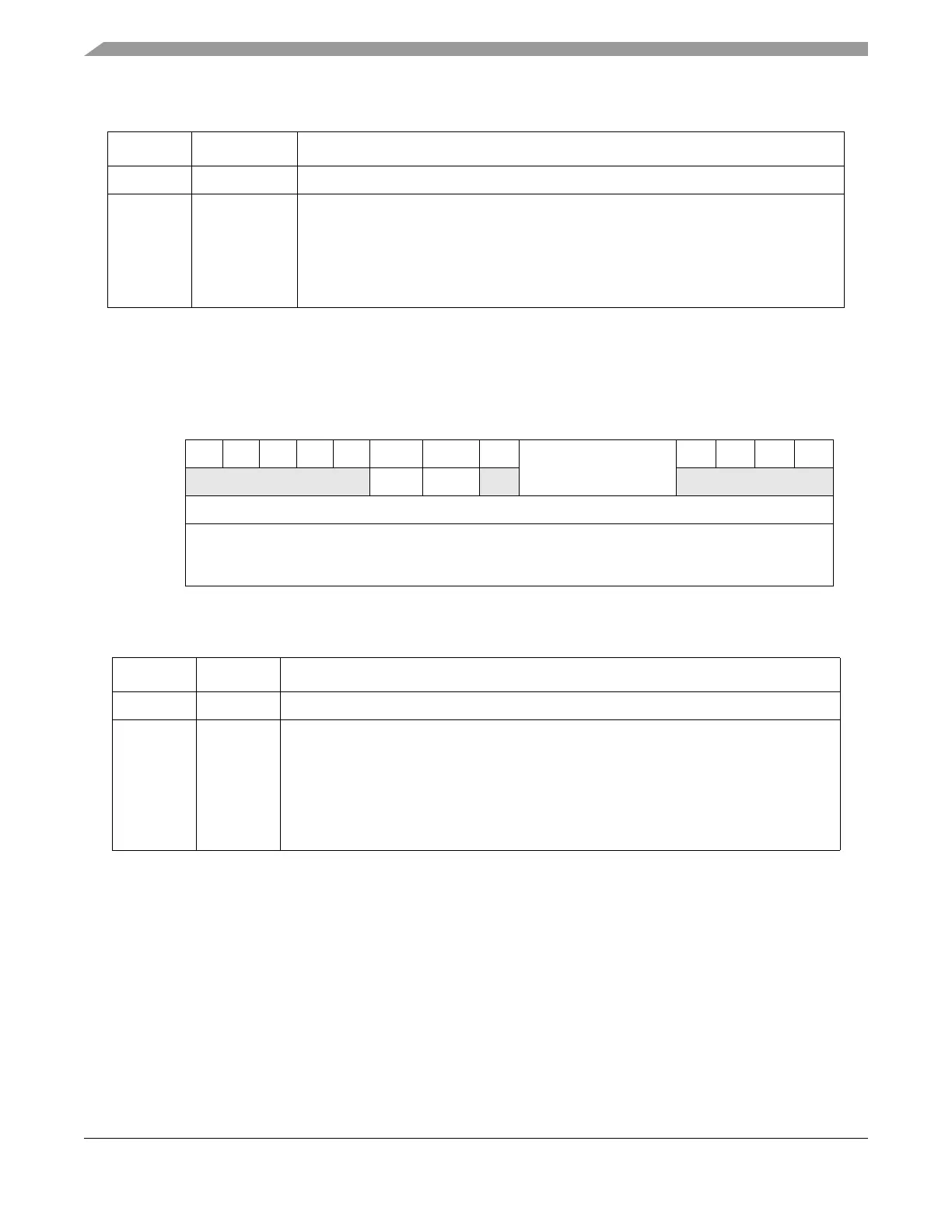

Table 19-8. EQADC_RFPRn Field Description

Bits Name Description

0–15 — Reserved.

16–31 RF_POPn

[0:15]

Result FIFO pop data n. When RFIFOn is not empty, the RF_POPn contains the next

unread entry value of RFIFOn.

Reading the whole word, a halfword, or any bytes of

EQADC_RFPRn will pop one entry from RFIFOn, and the corresponding RFCTRn value

will be decremented by 1 (See Section 19.3.2.8). When the RFIFOn is empty, any read

on EQADC_RFPRn returns undefined data value and does not decrement the RFCTRn

value. Writing to EQADC_RFPRn has no effect.

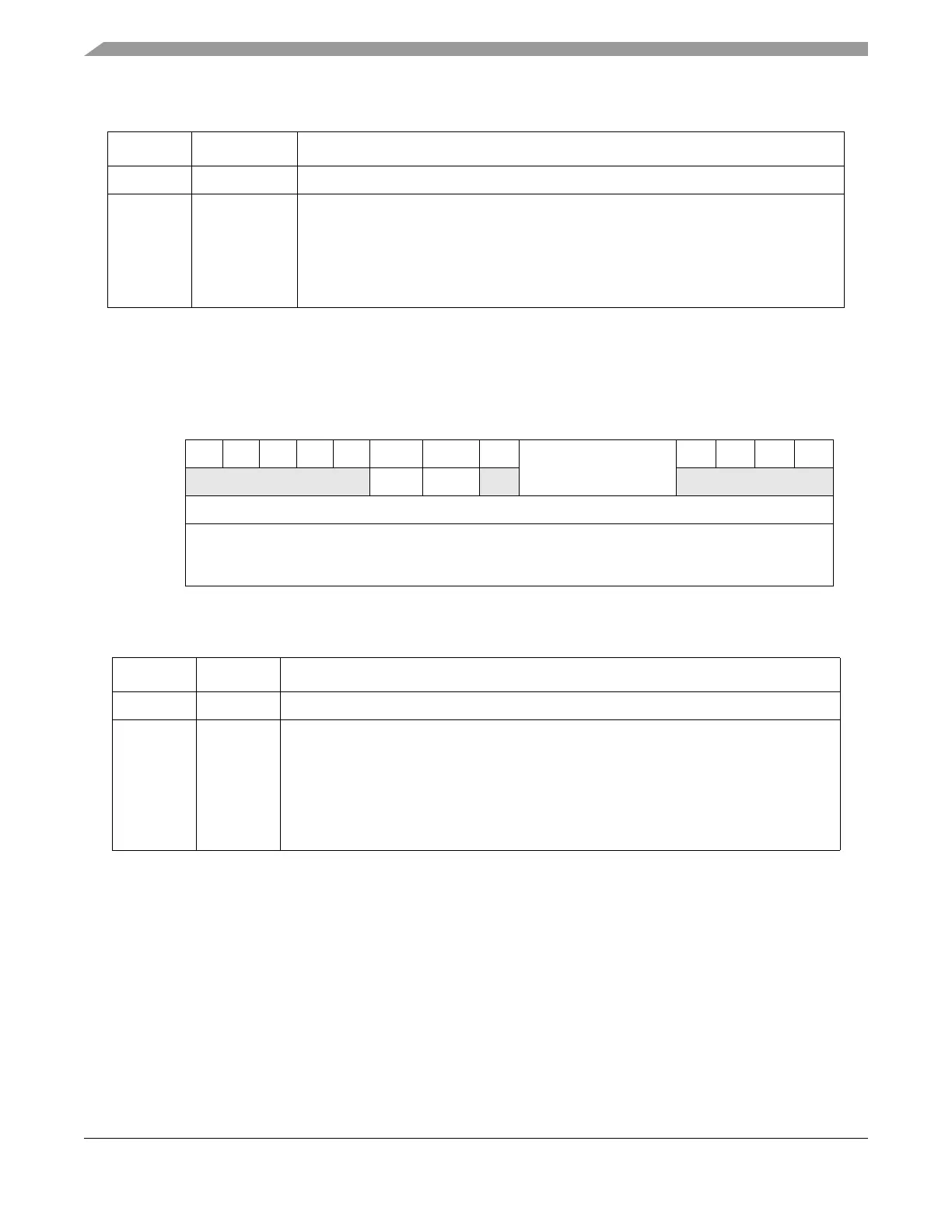

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R00000 0 0 0 MODEn 0000

W SSEn CFINVn

Reset00000 0 0 0 0 0 000000

Reg

Addr

EQADC_BASE+0x0050 (EQADC_CFCR0); EQADC_BASE+0x0052 (EQADC_CFCR1);

EQADC_BASE+0x0054 (EQADC_CFCR2) EQADC_BASE+0x0056 (EQADC_CFCR3);

EQADC_BASE+0x0058 (EQADC_CFCR4); EQADC_BASE+0x005A (EQADC_CFCR5)

Figure 19-7. eQADC CFIFO Control Registers (EQADC_CFCRn)

Table 19-9. EQADC_CFCRn Field Descriptions

Bits Name Description

0–4 — Reserved.

5 SSEn CFIFO single-scan enable bit n. Used to set the SSSn bit, as described in Section 19.3.2.8.

Writing a 1 to SSEn will set the SSSn if the CFIFO is in single-scan mode. When SSSn is

already asserted, writing a 1 to SSEn has no effect. If the CFIFO is in continuous-scan

mode or is disabled, writing a 1 to SSEn will not set SSSn. Writing a 0 to SSEn has no

effect. SSEn always is read as 0.

0 No effect.

1 Set the SSSn bit.

Loading...

Loading...