MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-17

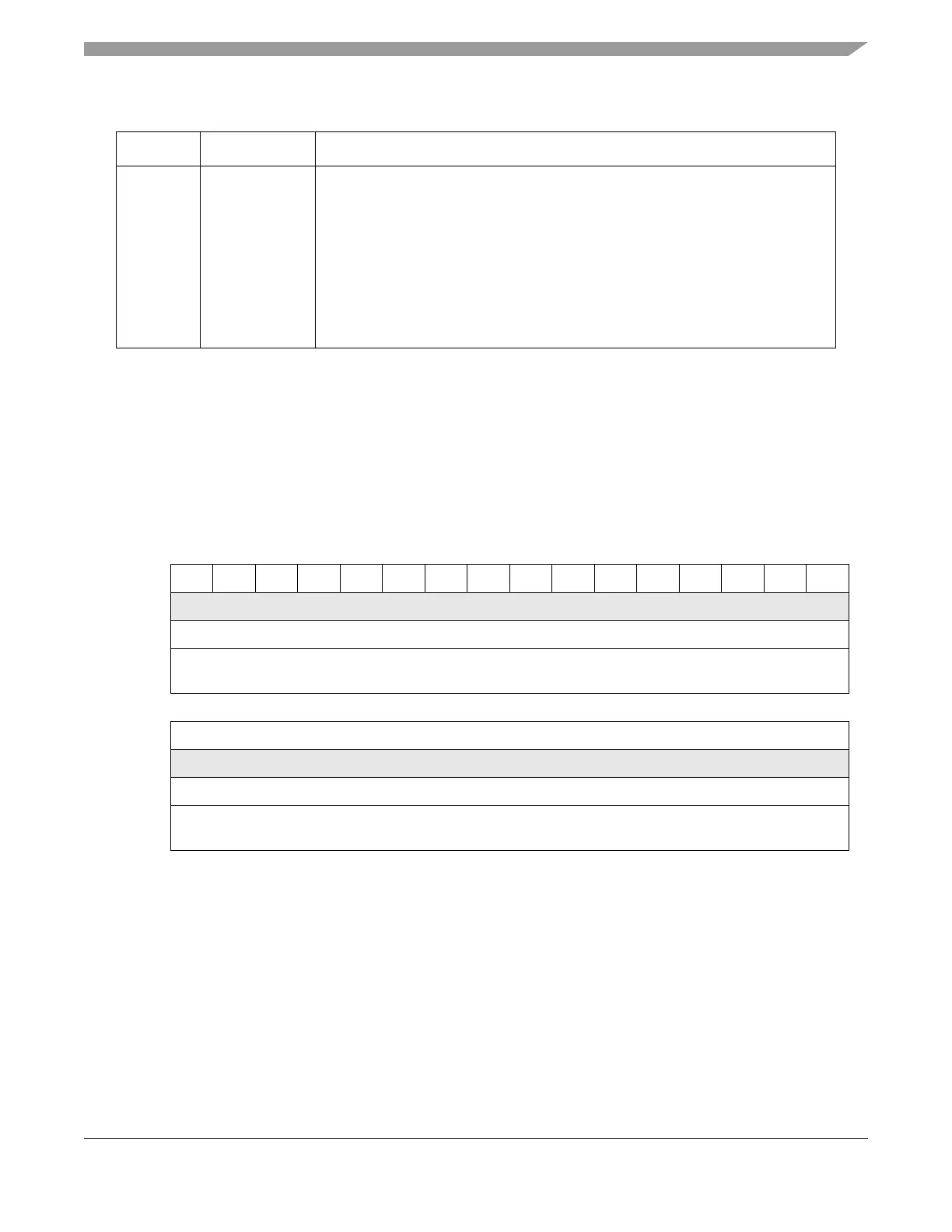

19.3.2.5 eQADC Result FIFO Pop Registers 0–5 (EQADC_RFPRn)

The eQADC_RFPRs provide a mechanism to retrieve data from RFIFOs.

NOTE

The EQADC_RFPRn must not be read speculatively. For future

compatibility, the TLB entry covering the EQADC_RFPRn must be

configured to be guarded.

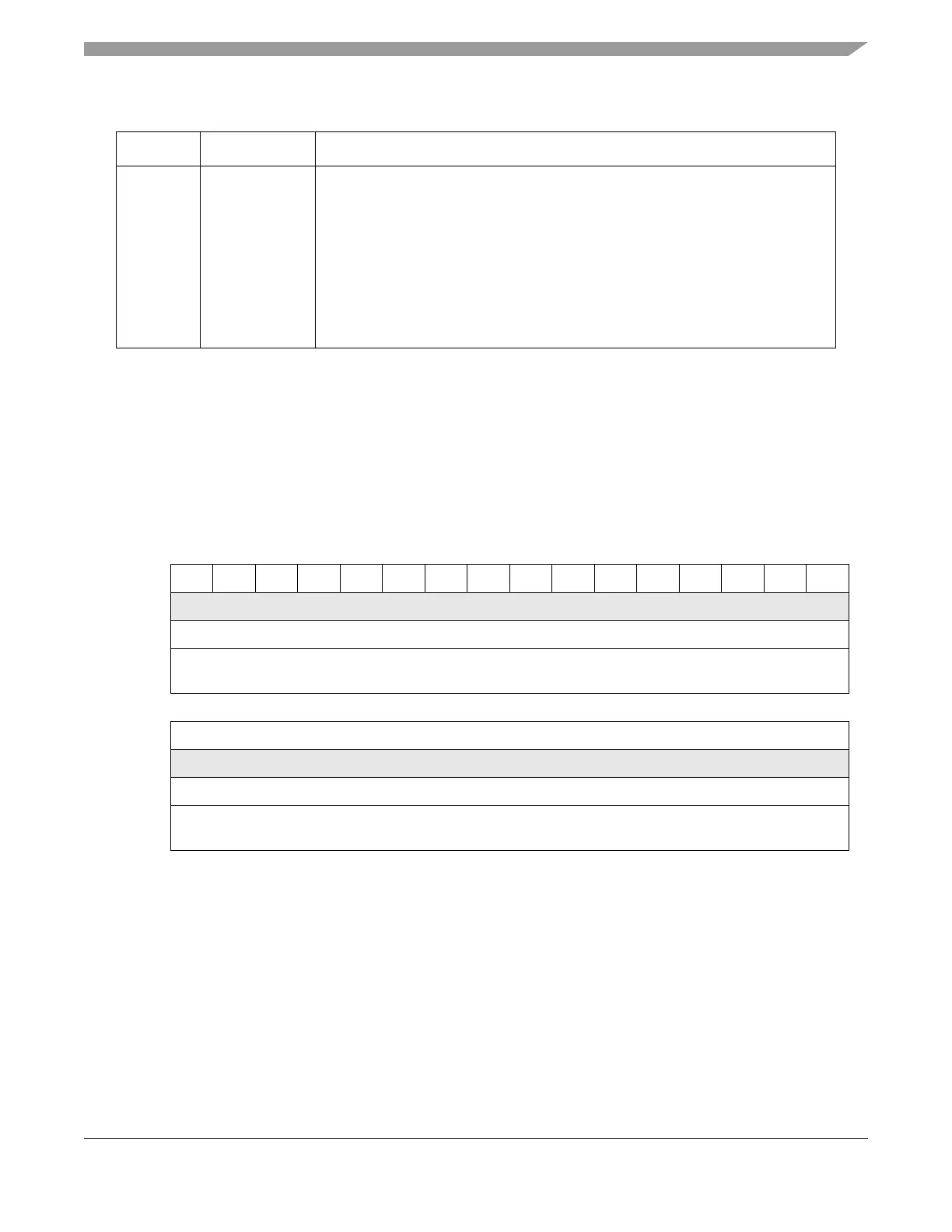

Table 19-7. EQADC_CFPRn Field Description

Bits Name Description

0–31 CF_PUSHn CFIFO push data n. When CFIFOn is not full, writing to the whole word or any bytes

of EQADC_CFPRn will push the 32-bit CF_PUSHn value into CFIFOn. Writing to

the CF_PUSHn field also increments the corresponding CFCTRn value by one in

Section 19.3.2.8, “eQADC FIFO and Interrupt Status Registers 0–5

(EQADC_FISRn).” When the CFIFOn is full, the eQADC ignores any write to the

CF_PUSHn. Reading the EQADC_CFPRn always returns 0.

Note: Only whole words must be written to EQADC_CFPR. Writing halfwords or

bytes to EQADC_CFPR will still push the whole 32-bit CF_PUSH field into the

corresponding CFIFO, but undefined data will fill the areas of CF_PUSH that were

not specifically designated as target locations for the write.

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

Reg

Addr

Base + 0x0030 (EQADC_RFPR0); Base + 0x0034 (EQADC_RFPR1); Base + 0x0038 (EQADC_RFPR2);

Base + 0x003C (EQADC_RFPR3); Base + 0x0040 (EQADC_RFPR4); Base + 0x0044 (EQADC_RFPR5)

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RRF_POPn

W

Reset0000000000000000

Reg

Addr

Base + 0x0030 (EQADC_RFPR0); Base + 0x0034 (EQADC_RFPR1); Base + 0x0038 (EQADC_RFPR2);

Base + 0x003C (EQADC_RFPR3); Base + 0x0040 (EQADC_RFPR4); Base + 0x0044 (EQADC_RFPR5)

Figure 19-6. eQADC RFIFO Pop Registers (EQADC_RFPRn)

Loading...

Loading...