MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-16 Freescale Semiconductor

19.3.2.4 eQADC CFIFO Push Registers 0–5 (EQADC_CFPRn)

The EQADC_CFPRs provide a mechanism to fill the CFIFOs with command messages from the command

queues. Refer to Section 19.4.3, “eQADC Command FIFOs,” for more information on the CFIFOs and to

Section 19.4.1.2, “Message Format in eQADC,” for a description on command message formats.

0b0111 129 1075.00

0b1000 257 2141.67

0b1001 513 4275.00

0b1010 1025 8541.67

0b1011 2049 17075.00

0b1100 4097 34141.67

0b1101 8193 68275.00

0b1110 16385 136541.67

0b1111 32769 273075.00

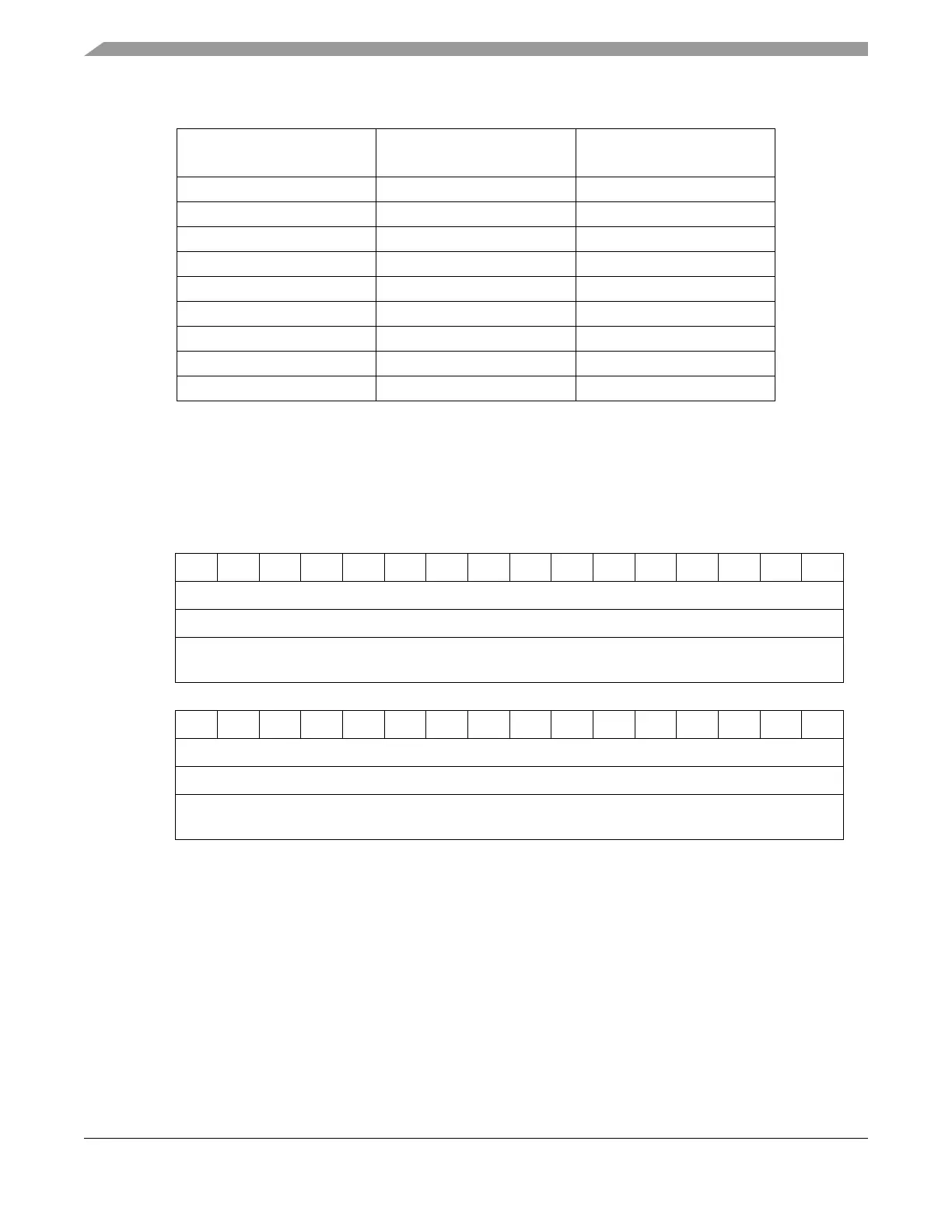

0123456789101112131415

R0000000000000000

W CF_PUSHn

Reset0000000000000000

Reg

Addr

Base + 0x0010 (EQADC_CFPR0); Base + 0x0014 (EQADC_CFPR1); Base + 0x0018 (EQADC_CFPR2);

Base + 0x001C (EQADC_CFPR3); Base + 0x0020 (EQADC_CFPR4); Base + 0x0024 (EQADC_CFPR5)

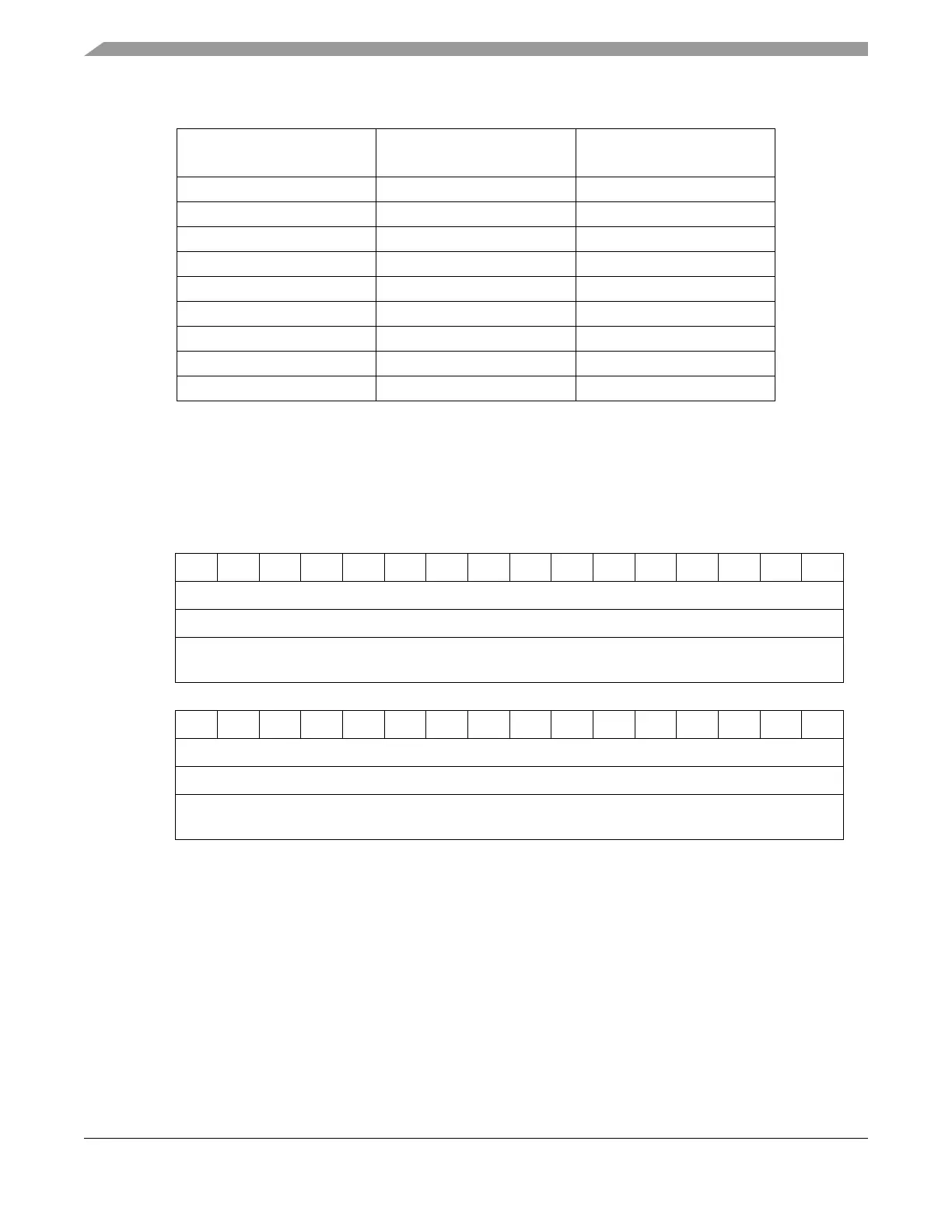

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000000000000000

W CF_PUSHn

Reset0000000000000000

Reg

Addr

Base + 0x0010 (EQADC_CFPR0); Base + 0x0014 (EQADC_CFPR1); Base + 0x0018 (EQADC_CFPR2);

Base + 0x001C (EQADC_CFPR3); Base + 0x0020 (EQADC_CFPR4); Base + 0x0024 (EQADC_CFPR5)

Figure 19-5. eQADC CFIFO Push Registers (EQADC_CFPRn)

Table 19-6. Minimum Required Time to Valid ETRIG (Continued)

DFL[0:3] Minimum Clock Count

Minimum Time (ns)

(System Clock = 120MHz)

Loading...

Loading...