MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-22 Freescale Semiconductor

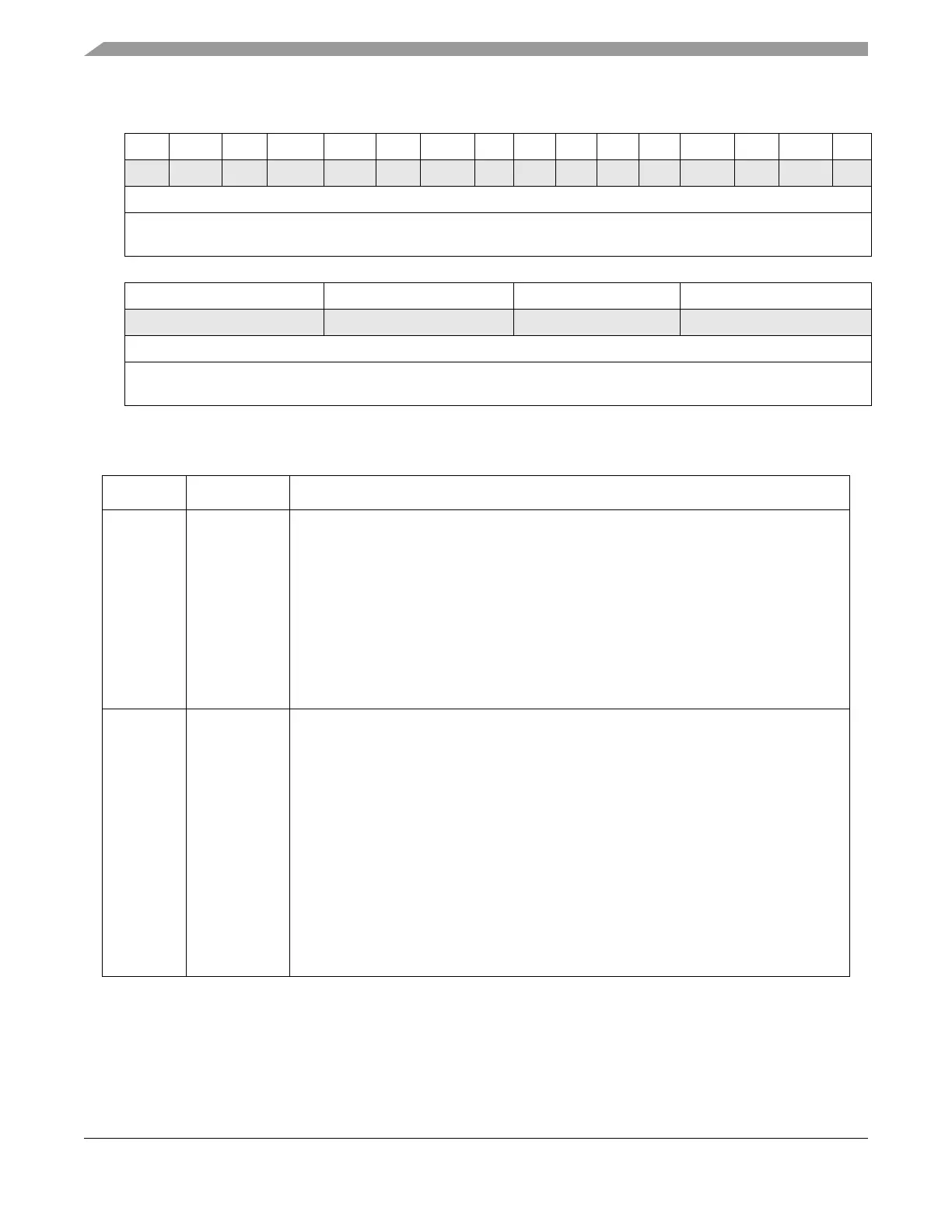

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R NCFn TORFn PFn EOQFn CFUFn SSSn CFFFn 00000RFOFn 0RFDFn 0

W

w1c w1c w1c w1c w1c w1c w1c w1c

Reset0 0 0 0 0 0 1 00000 0 0 0 0

Reg

Addr

Base + 0x0070 (EQADC_FISR0); Base + 0x0074 (EQADC_FISR1); Base + 0x0078 (EQADC_FISR2);

Base + 0x007C (EQADC_FISR3); Base + 0x0080 (EQADC_FISR4); Base + 0x0084 (EQADC_FISR5)

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RCFCTRn TNXTPTRn RFCTRn POPNXTPTRn

W

Reset0 0 0 0 0 0 0 00000 0 0 0 0

Reg

Addr

Base + 0x0070 (EQADC_FISR0); Base + 0x0074 (EQADC_FISR1); Base + 0x0078 (EQADC_FISR2);

Base + 0x007C (EQADC_FISR3); Base + 0x0080 (EQADC_FISR4); Base + 0x0084 (EQADC_FISR5)

Figure 19-9. eQADC FIFO and Interrupt Status Registers (EQADC_FISRn)

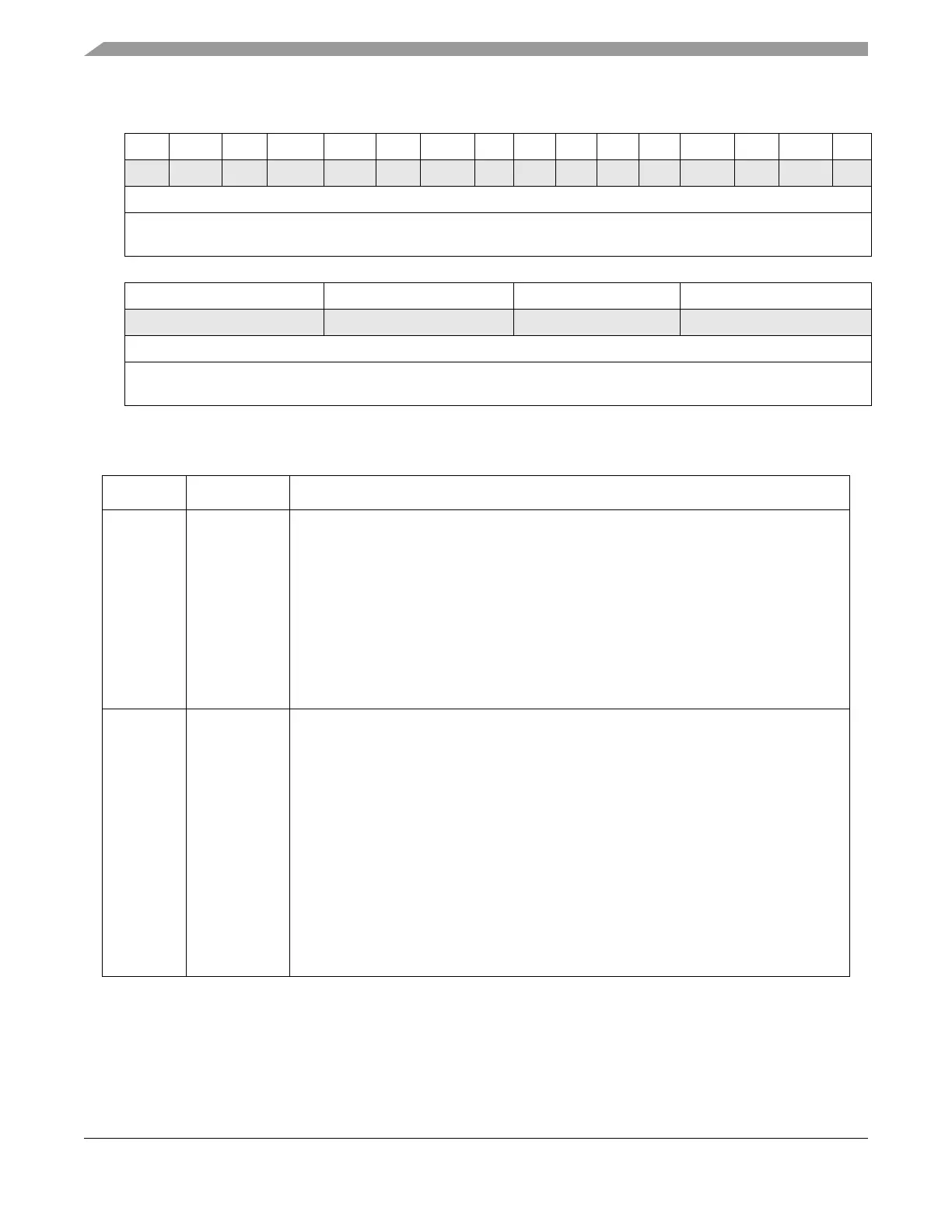

Table 19-12. EQADC_FISRn Field Descriptions

Bits Name Description

0NCFn Non-coherency flag n. NCFn is set whenever a command sequence being transferred

through CFIFOn becomes non-coherent. If NCIEn in EQADC_IDCRn (See Section

19.3.2.7) and NCFn are asserted, an interrupt request will be generated. Writing a 1 clears

NCFn. Writing a 0 has no effect. More for information on non-coherency refer to

Section 19.4.3.6.5, “Command Sequence Non-Coherency Detection.”

0 Command sequence being transferred by CFIFOn is coherent

1 Command sequence being transferred by CFIFOn became non-coherent

Note: Non-coherency means that a command in the command FIFO was not immediately

executed, but delayed. This may occur if the command is pre-empted, where a higher

priority queue is triggered and has a competing conversion command for the same

converter.

1TORFn Trigger overrun flag for CFIFO n. TORFn is set when trigger overrun occurs for the

specified CFIFO in edge or level trigger mode. Trigger overrun occurs when an already

triggered CFIFO receives an additional trigger. When EQADC_IDCRn[TORIEn] is set (See

Section 19.3.2.7) and TORFn are asserted, an interrupt request will be generated.

Apart from generating an independent interrupt request for a CFIFOn trigger overrun

event, the eQADC also provides a combined interrupt at which the result FIFO overflow

interrupt, the command FIFO underflow interrupt, and the command FIFO trigger overrun

Interrupt requests of all CFIFOs are ORed. When RFOIEn, CFUIEn, and TORIEn are all

asserted, this combined interrupt request is asserted whenever one of the following 18

flags becomes asserted: RFOFn, CFUFn, and TORFn (assuming that all interrupts are

enabled). See Section 19.4.7, “eQADC eDMA/Interrupt Request,” for details.

Write 1 to clear the TORFn bit. Writing 0 has no effect.

0 No trigger overrun occurred

1 Trigger overrun occurred

Note: The trigger overrun flag will not set for CFIFOs configured for software trigger mode.

Loading...

Loading...