MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-40 Freescale Semiconductor

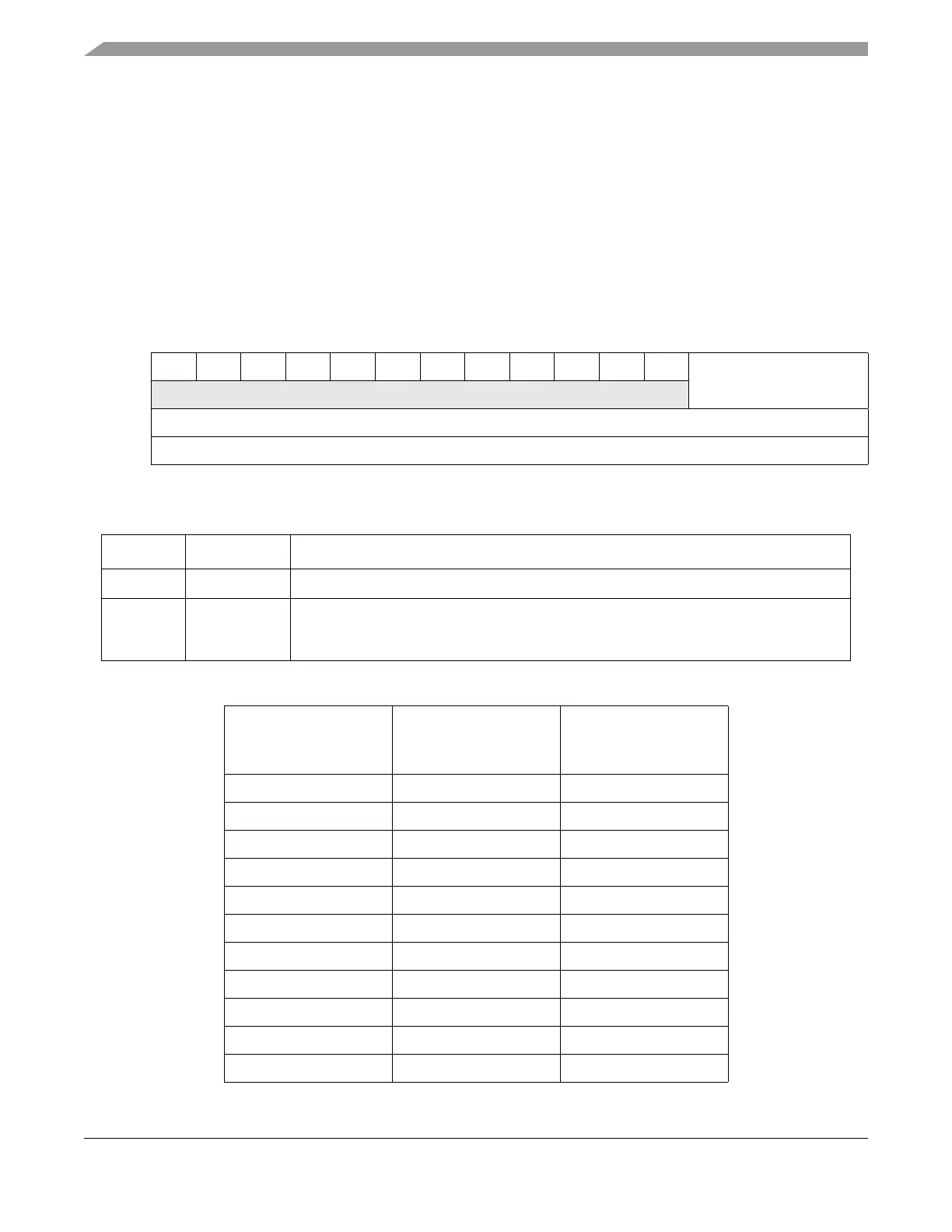

19.3.3.2 ADC Time Stamp Control Register (ADC_TSCR)

The ADC_TSCR contains a system clock divide factor used in the making of the time base counter clock.

It determines at what frequency the time base counter will run. ADC_TSCR can be accessed by

configuration commands sent to ADC0 or to ADC1. A data write to ADC_TSCR through a configuration

command sent to ADC0 will write the same memory location as when writing to it through a configuration

command sent to ADC1.

NOTE

Simultaneous write accesses from ADC0 and ADC1 to ADC_TSCR are not

allowed.

0123456789101112131415

R000000000000 TBC_CLK_PS

W

Reset0000000000000000

Reg Addr 0x02

Figure 19-20. ADC Time Stamp Control Register (ADC_TSCR)

Table 19-29. ADC_TSCR Field Descriptions

Bits Name Description

0–11 —

Reserved.

12–15 TBC_CLK_PS

[0:3]

Time base counter clock prescaler. Contains the system clock divide factor for the time

base counter. It controls the accuracy of the time stamp. The prescaler is disabled when

TBC_CLK_PS is set to 0b0000.

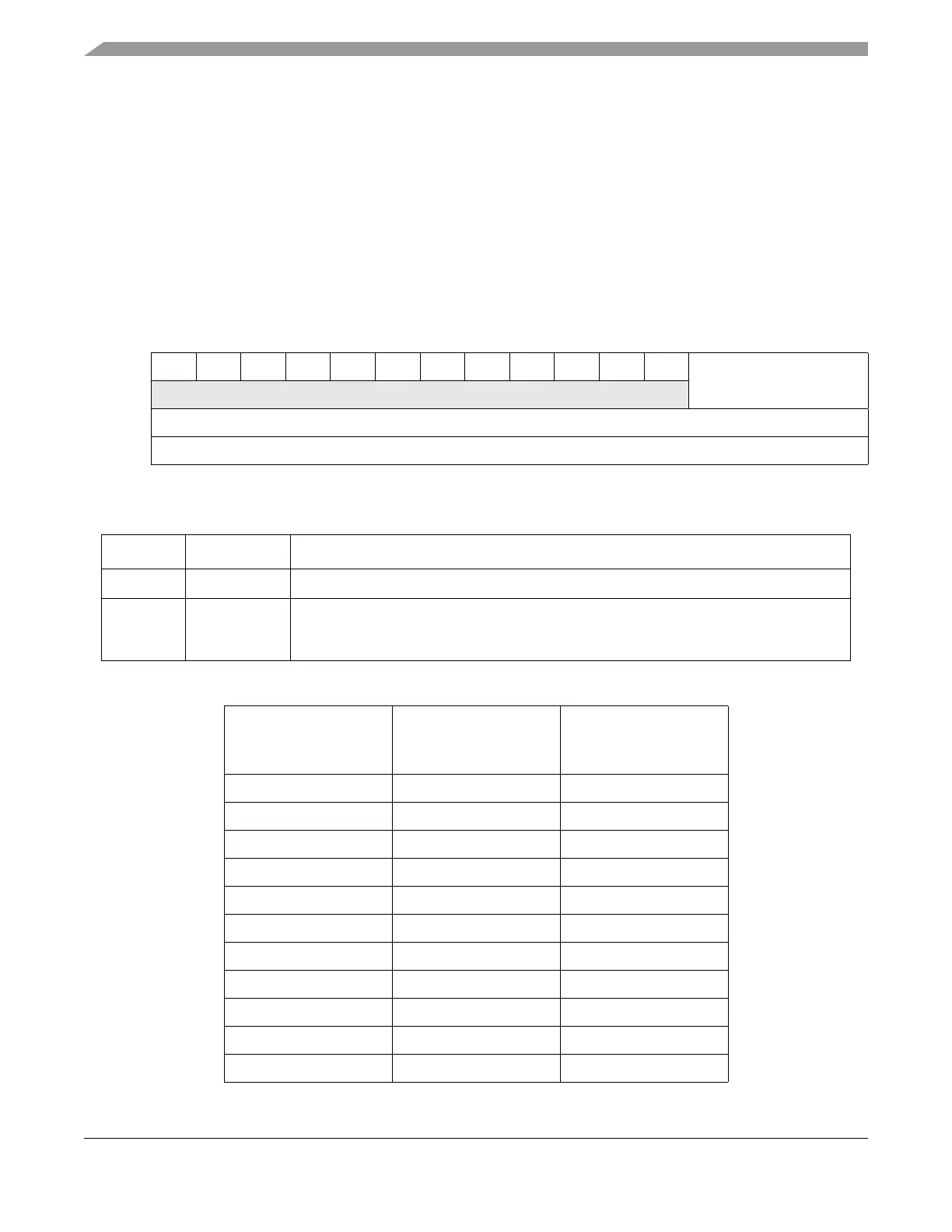

Table 19-30. Clock Divide Factor for Time Stamp

TBC_CLK_PS[0:3]

System Clock Divide

Factor

Clock to Time Stamp

Counter for a 120 MHz

System Clock (MHz)

0b0000 Disabled Disabled

0b0001 1 120

0b0010 2 60

0b0011 4 30

0b0100 6 20

0b0101 8 15

0b0110 10 12

0b0111 12 10

0b1000 16 7.5

0b1001 32 3.75

0b1010 64 1.88

Loading...

Loading...