MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-51

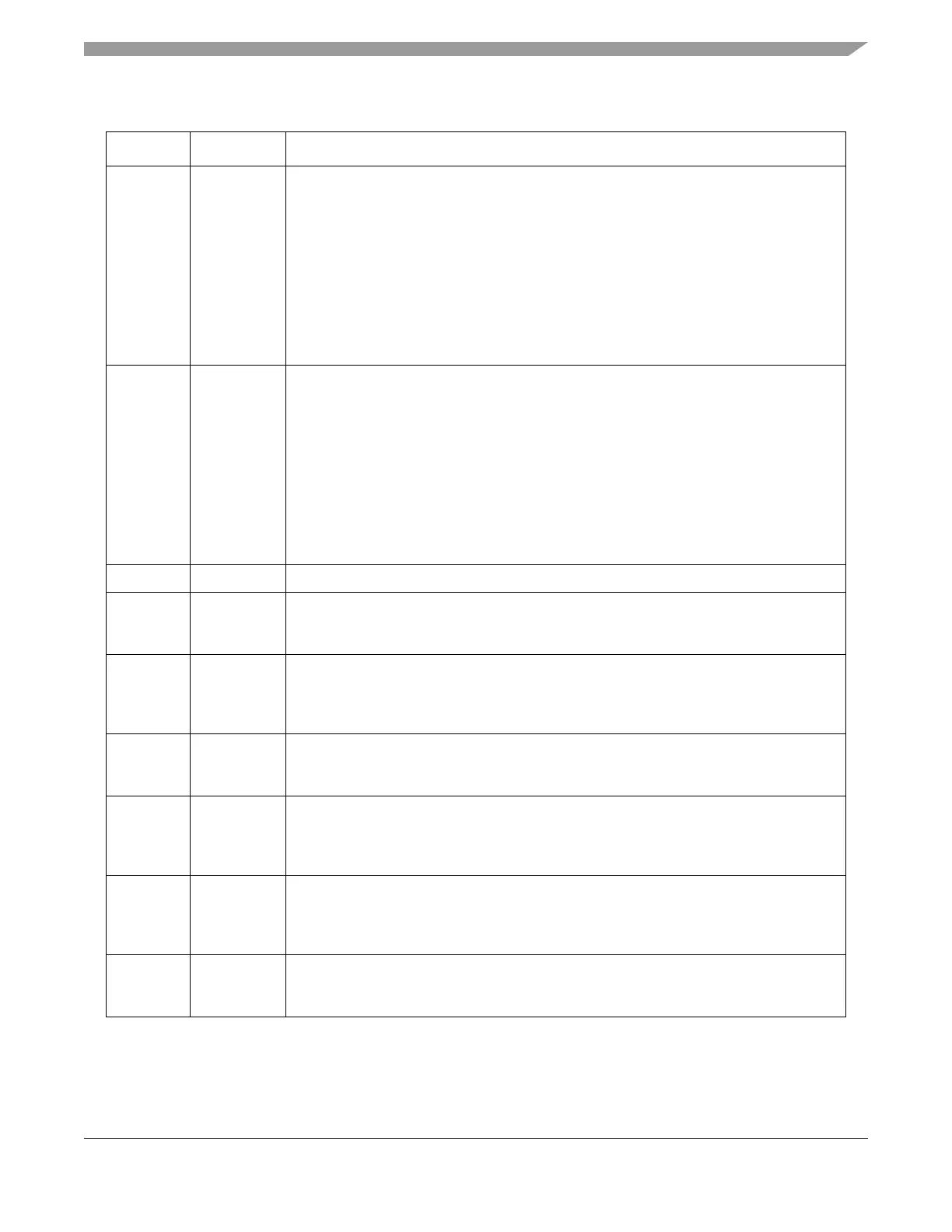

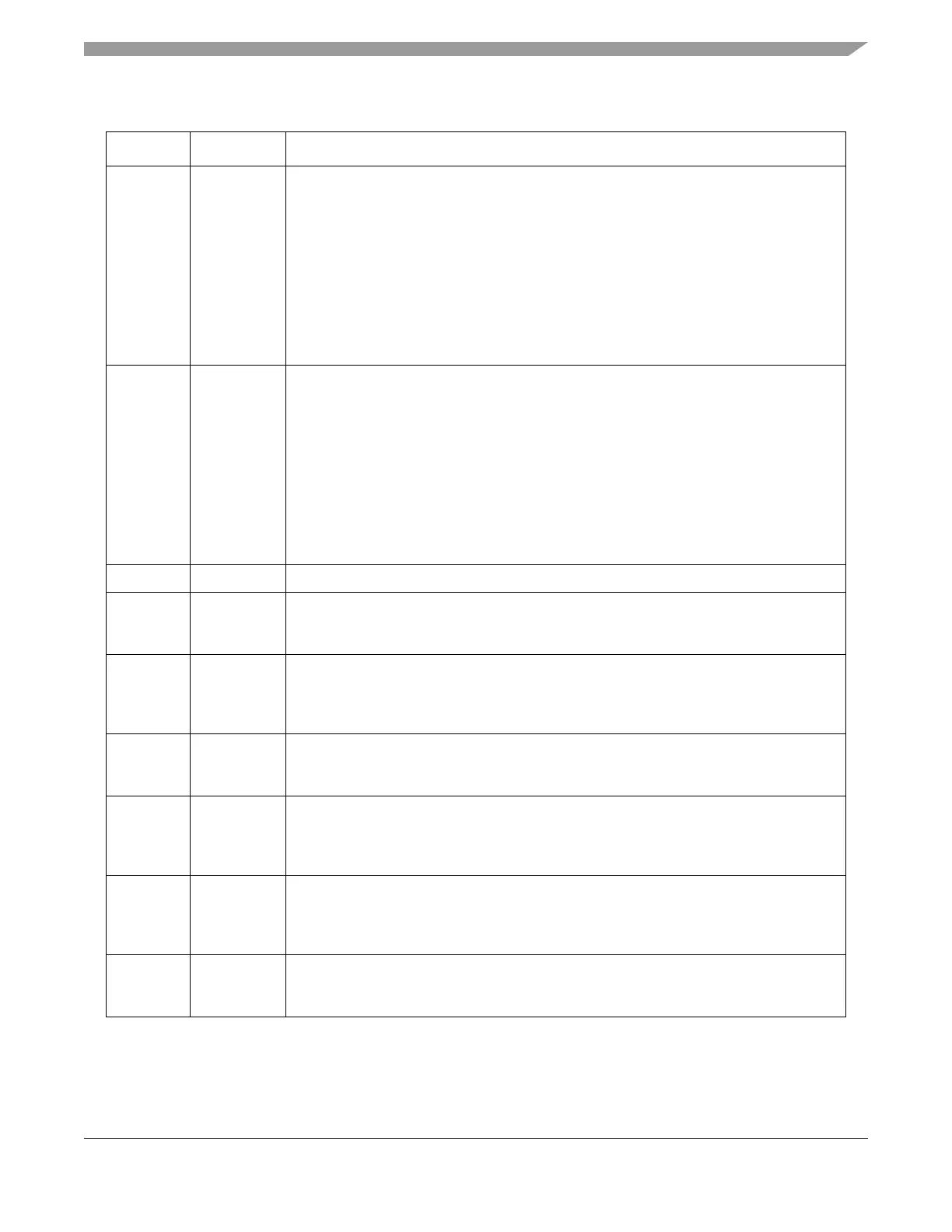

Read Configuration Command Message Format for On-Chip ADC Operation

Table 19-35. On-Chip ADC Field Descriptions: Write Configuration

Bits Name Description

0 EOQ End-of-queue. Asserted in the last command of a command queue to indicate to the

eQADC that a scan of the queue is completed. EOQ instructs the eQADC to reset its

current CFIFO transfer counter value (TC_CF) to 0. Depending on the CFIFO mode of

operation, the CFIFO status will also change upon the detection of an asserted EOQ bit on

the last transferred command. See Section 19.4.3.5, “CFIFO Scan Trigger Modes,” for

details.

0 Not the last entry of the command queue.

1 Last entry of the command queue.

Note: If both the pause and EOQ bits are asserted in the same command message the

respective flags are set, but the CFIFO status changes as if only the EOQ bit were

asserted.

1 PAUSE Pause bit. Allows software to create sub-queues within a command queue. When the

eQADC completes the transfer of a command with an asserted pause bit, the CFIFO

enters the WAITING FOR TRIGGER state. Refer to Section 19.4.3.6.1, “CFIFO Operation

Status,” for a description of the state transitions. The pause bit is only valid when CFIFO

operation mode is configured to single or continuous-scan edge trigger mode.

0 Do not enter WAITING FOR TRIGGER state after transfer of the current command

message.

1 Enter WAITING FOR TRIGGER state after transfer of the current command message.

Note: If both the pause and EOQ bits are asserted in the same command message, the

respective flags are set, but the CFIFO status changes as if only the EOQ bit were

asserted.

2–4 — Reserved.

5 EB External buffer bit. This bit should always be cleared for messages sent to an on-chip ADC.

0 Command is sent to an internal command buffer.

1 Command is sent to an external command buffer.

6 BN Buffer number. Indicates which buffer the message will be stored in. Buffers 1 and 0 can

either be internal or external depending on the EB bit setting.

0 Message stored in buffer 0.

1 Message stored in buffer 1.

7 R/W Read/write. A negated R/W indicates a write configuration command.

0Write

1 Read

8–15 ADC_

REGISTER_

HIGH_BYTE

[0:7]

ADC register high byte. The value to be written into the most significant 8 bits of

control/configuration register when the R/W bit is negated.

16–23 ADC_

REGISTER_

LOW_BYTE

[0:7]

ADC register low byte. The value to be written into the least significant 8 bits of a

control/configuration register when the R/W bit is negated.

24–31 ADC_REG_

ADDRESS

[0:7]

ADC register address. Selects a register on the ADC register set to be written or read. Only

halfword addresses can be used. See Ta bl e 1 9- 25 .

Loading...

Loading...