MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-71

19.4.3.6 CFIFO and Trigger Status

19.4.3.6.1 CFIFO Operation Status

Each CFIFO has its own CFIFO status field. CFIFO status (CFS) can be read from EQADC_CFSSR (see

Section 19.3.2.11, “eQADC CFIFO Status Register (EQADC_CFSR).” Figure 19-39 and Table 19-45

indicate the CFIFO status switching condition. Refer to Table 19-18 for the meaning of each CFIFO

operation status. The last CFIFO to transfer a command to an on-chip ADC can be read from the LCFTn

(n=0,1) fields (see Section 19.3.2.10, “eQADC CFIFO Status Snapshot Registers 0–2

(EQADC_CFSSRn).” The last CFIFO to transfer a command to a specific external command buffer can

be identified by reading the EQADC_CFSSRn[LCFTSSI] and EQADC_CFSSRn[ENI] fields (see

Section 19.3.2.10, “eQADC CFIFO Status Snapshot Registers 0–2 (EQADC_CFSSRn).”

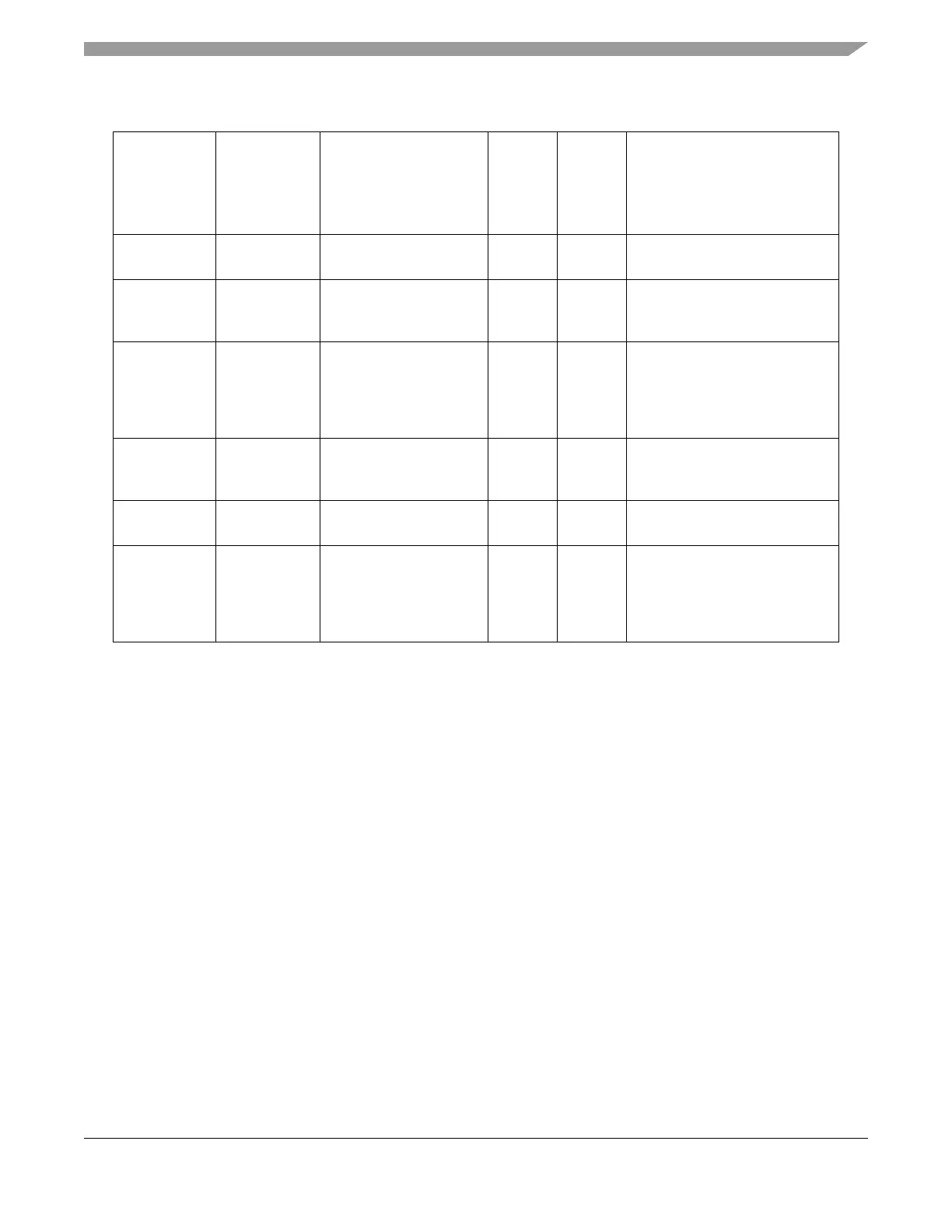

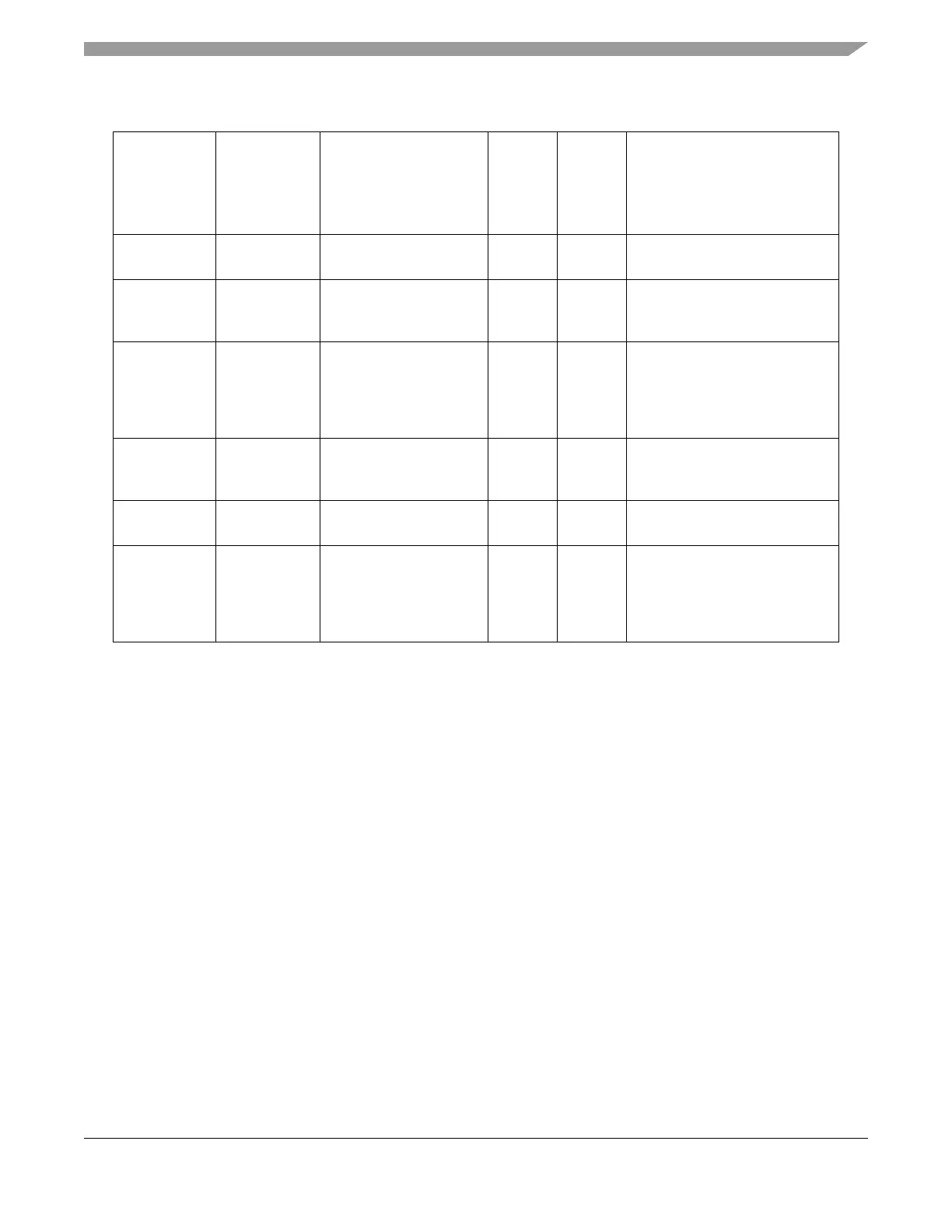

Table 19-44. CFIFO Scan Trigger Mode—Command Transfer Start/Stop Summary

Trigger Mode

Requires

Asserted SSS

to Recognize

Trigger

Events?

Command Transfer

Start/Restart Condition

Stop on

asserted

EOQ

bit

1

?

1

Refer to Section 19.4.3.6.2, “Command Queue Completion Status,” for more information on EOQ.

Stop on

asserted

Pause

bit

2

?

2

Refer to Section 19.4.3.6.3, “Pause Status,” for more information on pause.

Other Command Transfer Stop

Condition

3

4

3

The eQADC always stops command transfers from a CFIFO when the CFIFO operation mode is disabled.

4

The eQADC always stops command transfers from a CFIFO when a higher priority CFIFO is triggered. Refer to

Section 19.4.3.2, “CFIFO Prioritization and Command Transfer,” for information on CFIFO priority.

Single Scan

Software

Not Applicable Asserted SSS bit. Yes No None.

Single Scan

Edge

Yes A corresponding edge

occurs when the SSS bit

is asserted.

Yes Yes None.

Single Scan

Level

Yes Gate is opened when the

SSS bit is asserted.

Yes No The eQADC also stops transfers

from the CFIFO when CFIFO

status changes from triggered

due to the detection of a closed

gate.

5

5

If a closed gate is detected while no command transfers are taking place, it will have immediate effect on the CFIFO

status. If a closed gate is detected during the serial transmission of a command to the external device, it will have no

effect on the CFIFO status until the transmission completes.

Continuous

Scan Software

No CFIFO starts

automatically after being

configured into this mode.

No No None.

Continuous

Scan Edge

No A corresponding edge

occurs.

Yes Yes None.

Continuous

Scan Level

No Gate is opened. No No The eQADC also stops transfers

from the CFIFO when CFIFO

status changes from triggered

due to the detection of a closed

gate.

5

Loading...

Loading...