MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-27

19.3.2.10 eQADC CFIFO Status Snapshot Registers 0–2 (EQADC_CFSSRn)

The eQADC_CFSSRs contain status fields to track the operation status of each CFIFO and the transfer

counter of the last CFIFO to initiate a command transfer to the internal ADCs and the external command

buffers. EQADC_CFSSR0–1 are related to the on-chip ADC command buffers (buffers 0 and 1) while

EQADC_CFSSR2 is related to the external command buffers (buffers 2 and 3). All fields of a particular

EQADC_CFSSR are captured at the beginning of a command transfer to the buffer associated with that

register.

Note that captured status register values are associated with a previous command transfer. This means that

the eQADC_CFSSR registers capture the status registers before the status registers change, because of the

transfer of the current command that is about to be popped from the CFIFO. The EQADC_CFSSRs are

read only. Writing to the EQADC_CFSSRs has no effect.

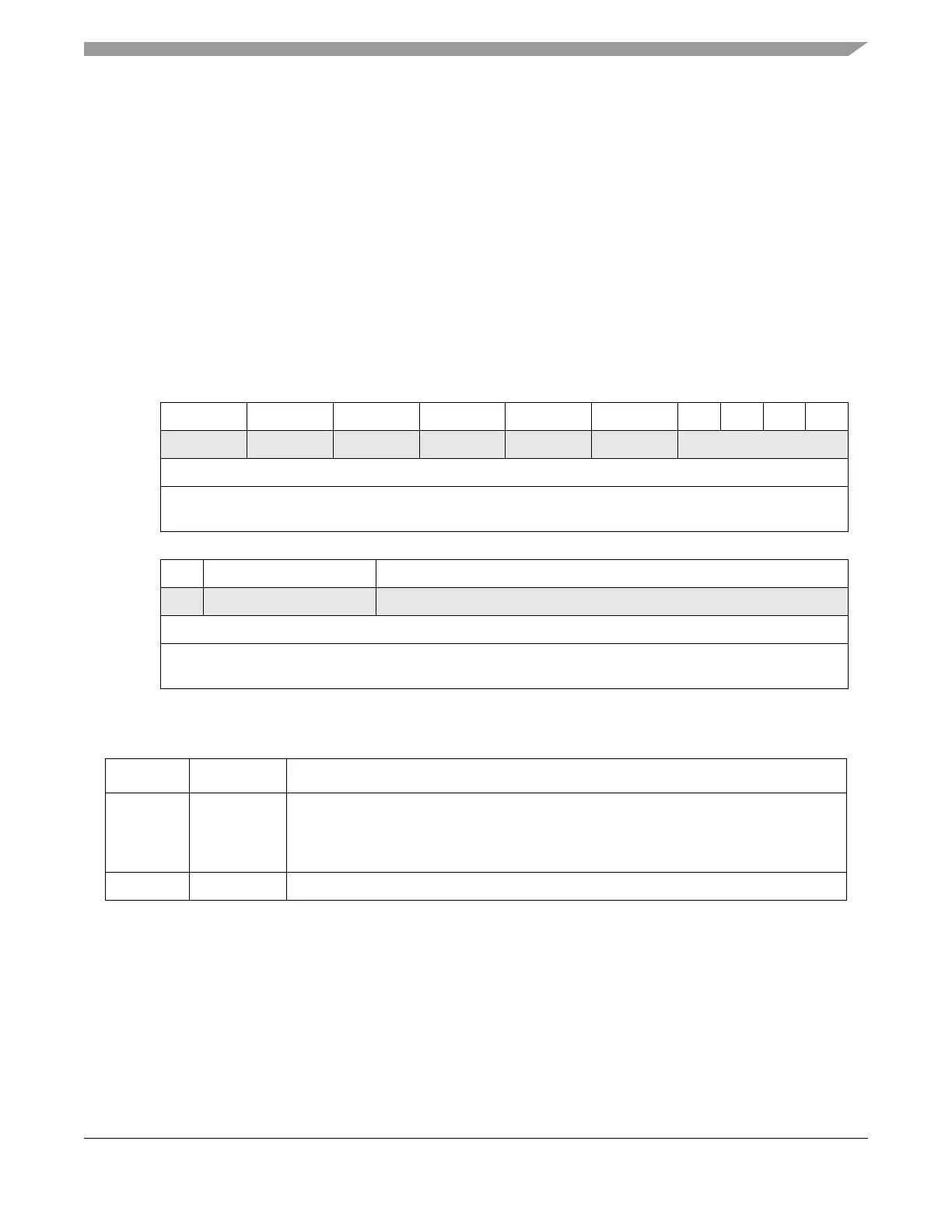

0123456789101112131415

R CFS0_T0 CFS1_T0 CFS2_T0 CFS3_T0 CFS4_T0 CFS5_T0 0 0 0 0

W

Reset0000000000000000

Reg

Addr

Base + 0x00A0 (EQADC_CFSSR0)

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R 0 LCFT0 TC_LCFT0

W

Reset0111100000000000

Reg

Addr

Base + 0x00A0 (EQADC_CFSSR0)

Figure 19-11. eQADC CFIFO Status Snapshot Register 0 (EQADC_CFSSR0)

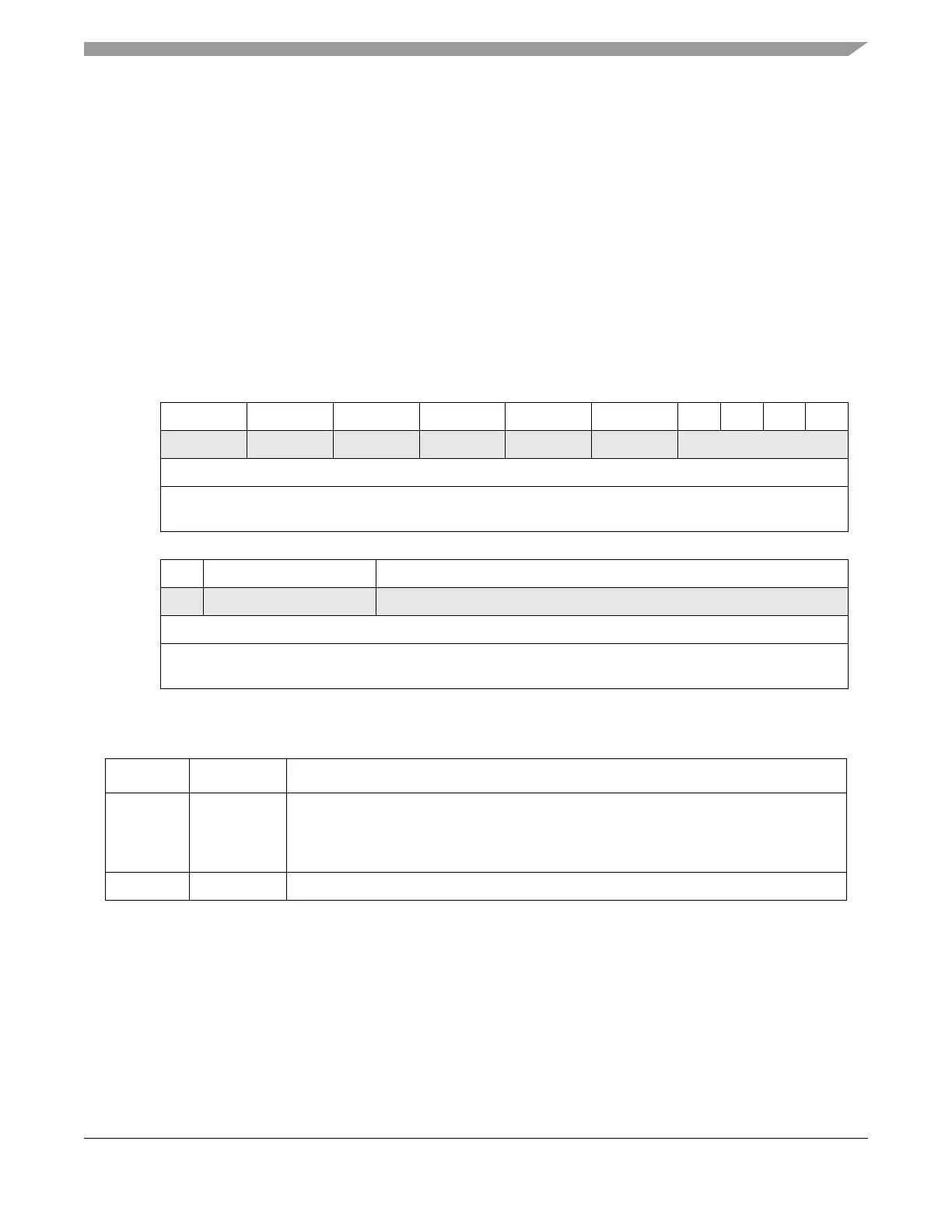

Table 19-14. EQADC_CFSSR0 Field Descriptions

Bits Name Description

0–11 CFSn_T0

[0:1]

CFIFO status at transfer to ADCn command buffer. Indicates the CFIFOn status at the time

a command transfer to ADCn command buffer is initiated. CFSn_T0 is a copy of the

corresponding CFSn in EQADC_CFSR (see Section 19.3.2.11) captured at the time a

command transfer to buffern is initiated.

12–16 — Reserved.

Loading...

Loading...