MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-32 Freescale Semiconductor

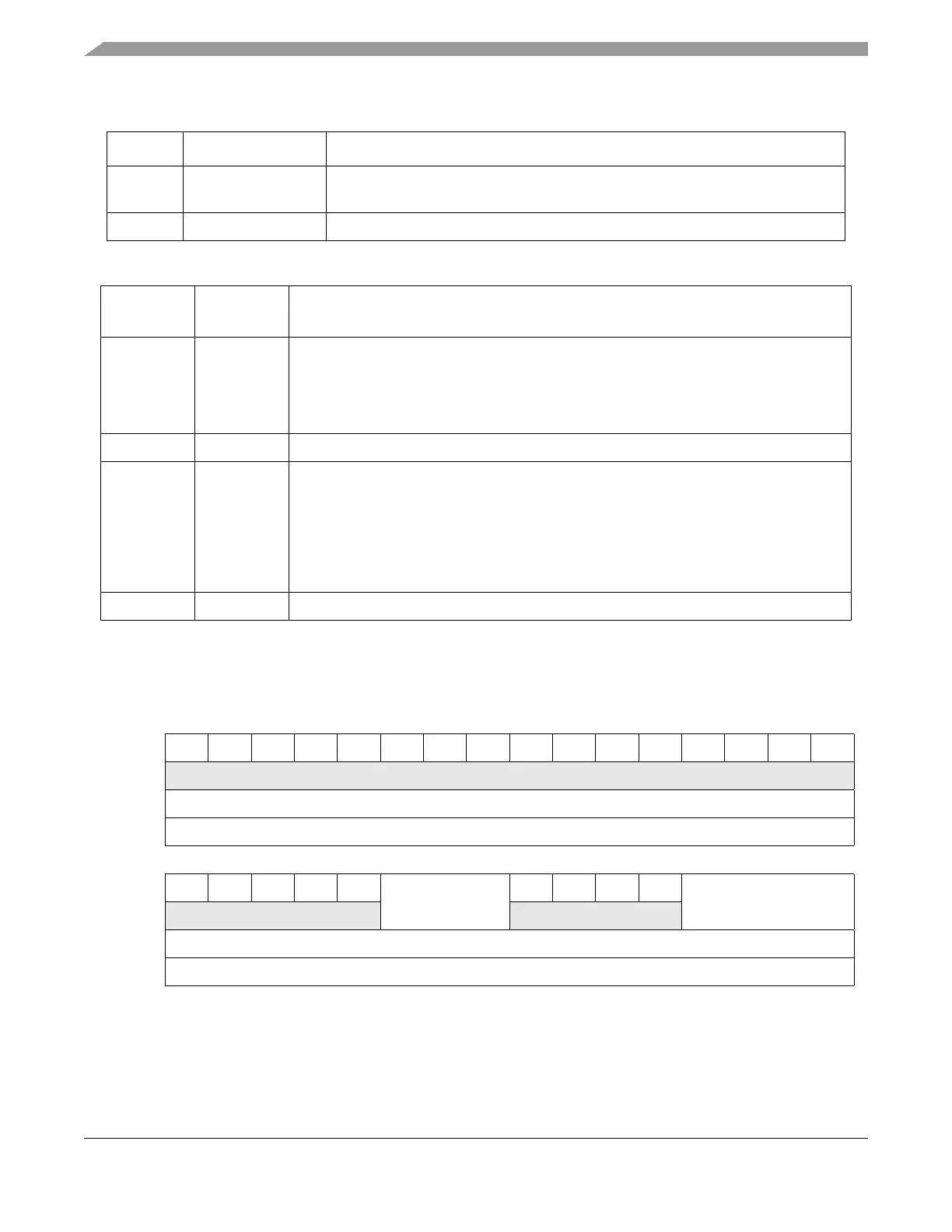

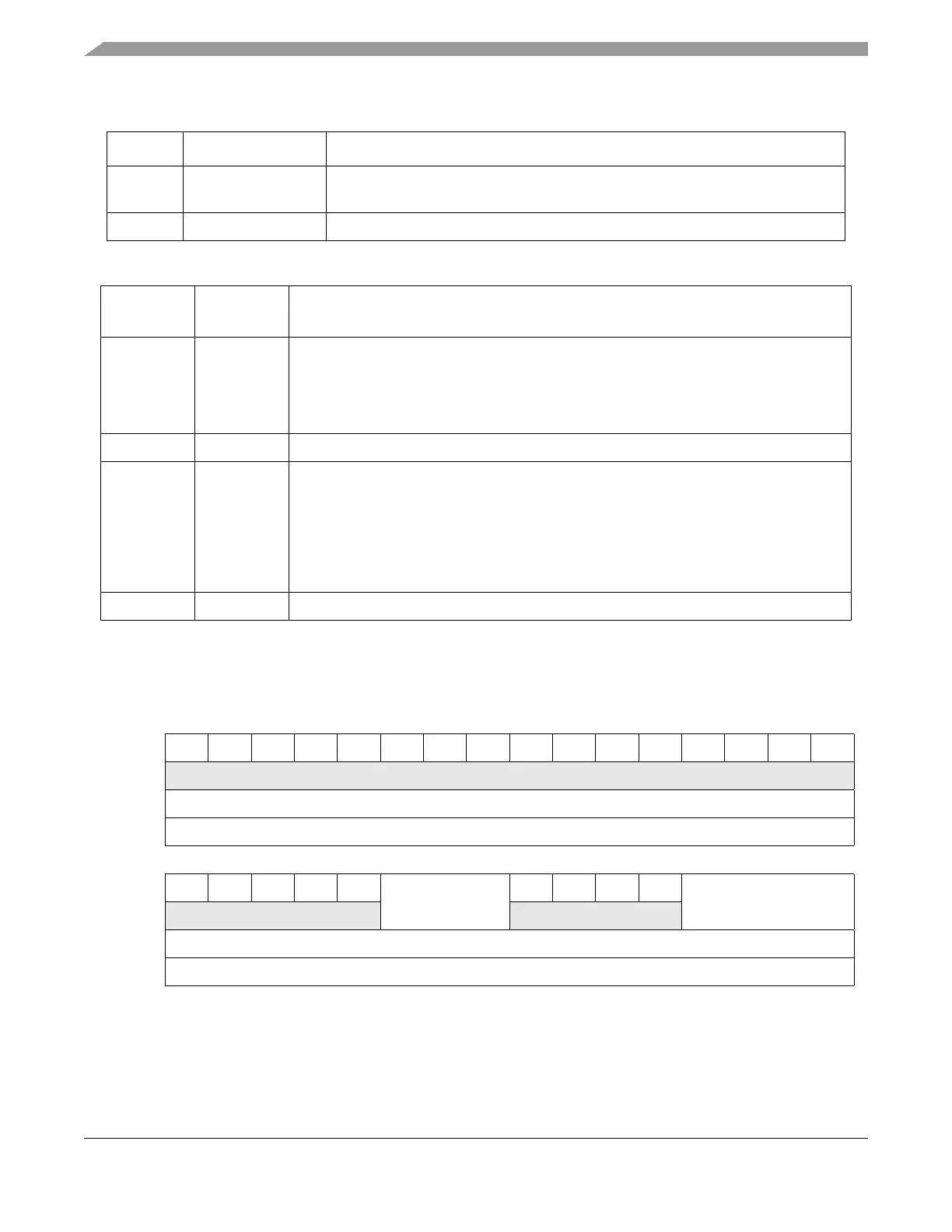

19.3.2.12 eQADC SSI Control Register (EQADC_SSICR)

The EQADC_SSICR configures the SSI submodule.

Table 19-17. EQADC_CFSR Field Descriptions

Bits Name Description

0–11 CFSn

[0:1]

CFIFO status. Indicates the current status of CFIFOn. Refer to Table 19-18 for more

information on CFIFO status.

12–31 — Reserved.

Table 19-18. Current CFIFO Status

CFIFO

Status

Field Value Explanation

IDLE 0b00 • CFIFO is disabled.

• CFIFO is in single-scan edge or level trigger mode and does not have

EQADC_FISRn[SSS] asserted.

• eQADC completed the transfer of the last entry of the user defined command queue in

single-scan mode.

Reserved 0b01 Not applicable.

WAITING

FOR

TRIGGER

0b10 • CFIFO mode is modified to continuous-scan edge or level trigger mode.

• CFIFO mode is modified to single-scan edge or level trigger mode and

EQADC_FISRn[SSS] is asserted.

• CFIFO mode is modified to single-scan software trigger mode and EQADC_FISRn[SSS]

is negated.

• CFIFO is paused.

• eQADC transferred the last entry of the queue in continuous-scan edge trigger mode.

TRIGGERED 0b11 CFIFO is triggered

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x00B4

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R00000 MDT 0000 BR

W

Reset0000011100001111

Reg Addr Base + 0x00B4

Figure 19-15. eQADC SSI Control Register (EQADC_SSICR)

Loading...

Loading...