MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-33

Table 19-19. EQADC_SSICR Field Descriptions

Bits Name Description

0–20 — Reserved.

21–23 MDT

[0:2]

Minimum delay after transmission. Defines the minimum delay after transmission time

(t

MDT

) expressed in serial clock (FCK) periods. t

MDT

is the minimum time SDS should be

kept negated between two consecutive serial transmissions. Table 19-20 lists the minimum

delay after transfer time according to how MDT is set.

The MDT field must only be written when the serial transmissions from the eQADC SSI are

disabled - See EQADC_MCR[ESSIE] field in Section 19.3.2.1.

24–27 — Reserved.

28–31 BR

[0:3]

Baud rate. Selects system clock divide factor as shown in Table 19-21. The baud clock is

calculated by dividing the system clock by the clock divide factor specified with the BR field.

Note: The BR field must only be written when the eQADC SSI is disabled - See

EQADC_MCR[ESSIE] field in Section 19.3.2.1.

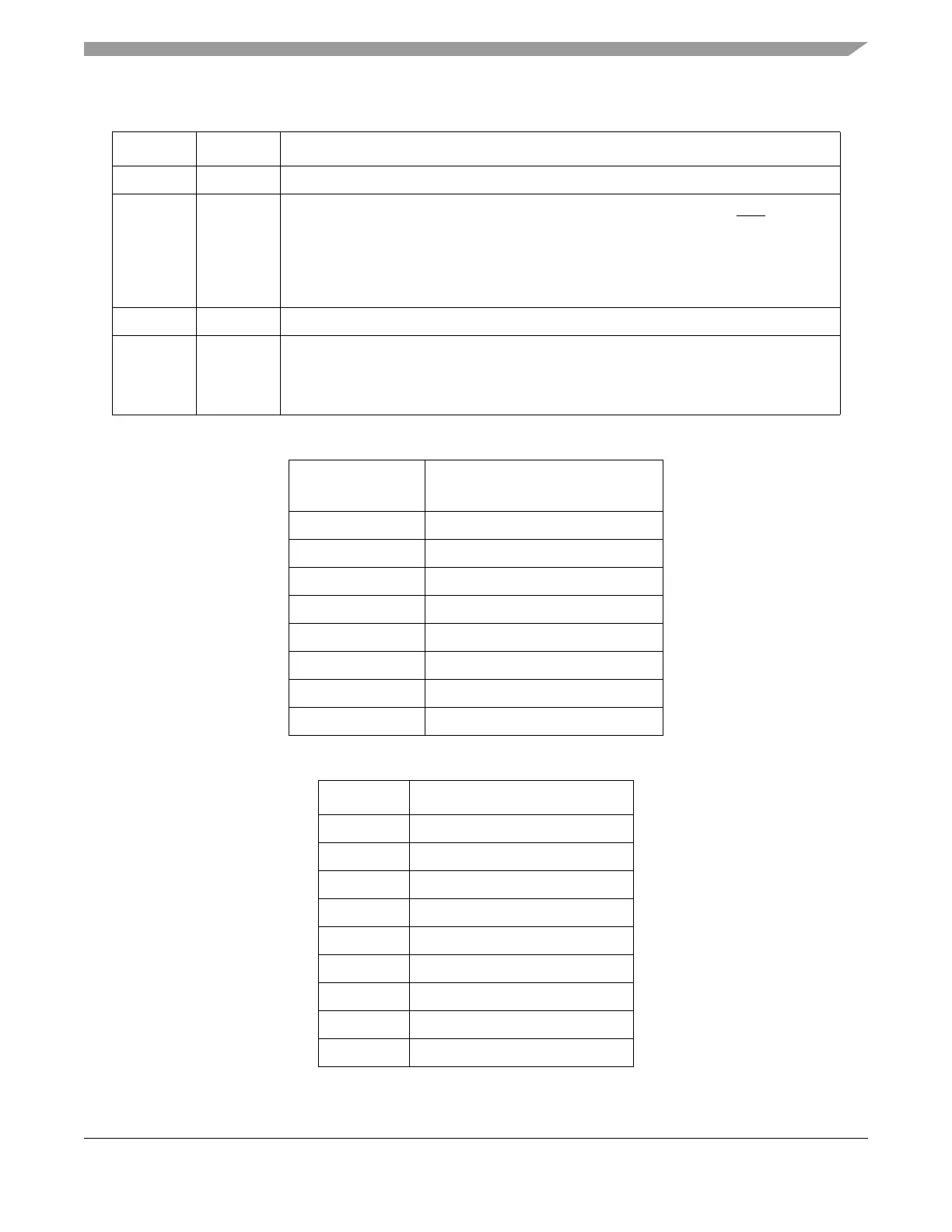

Table 19-20. Minimum Delay After Transmission (t

MDT

) Time

MDT

t

MDT

(FCK period)

0b000 1

0b001 2

0b010 3

0b011 4

0b100 5

0b101 6

0b110 7

0b111 8

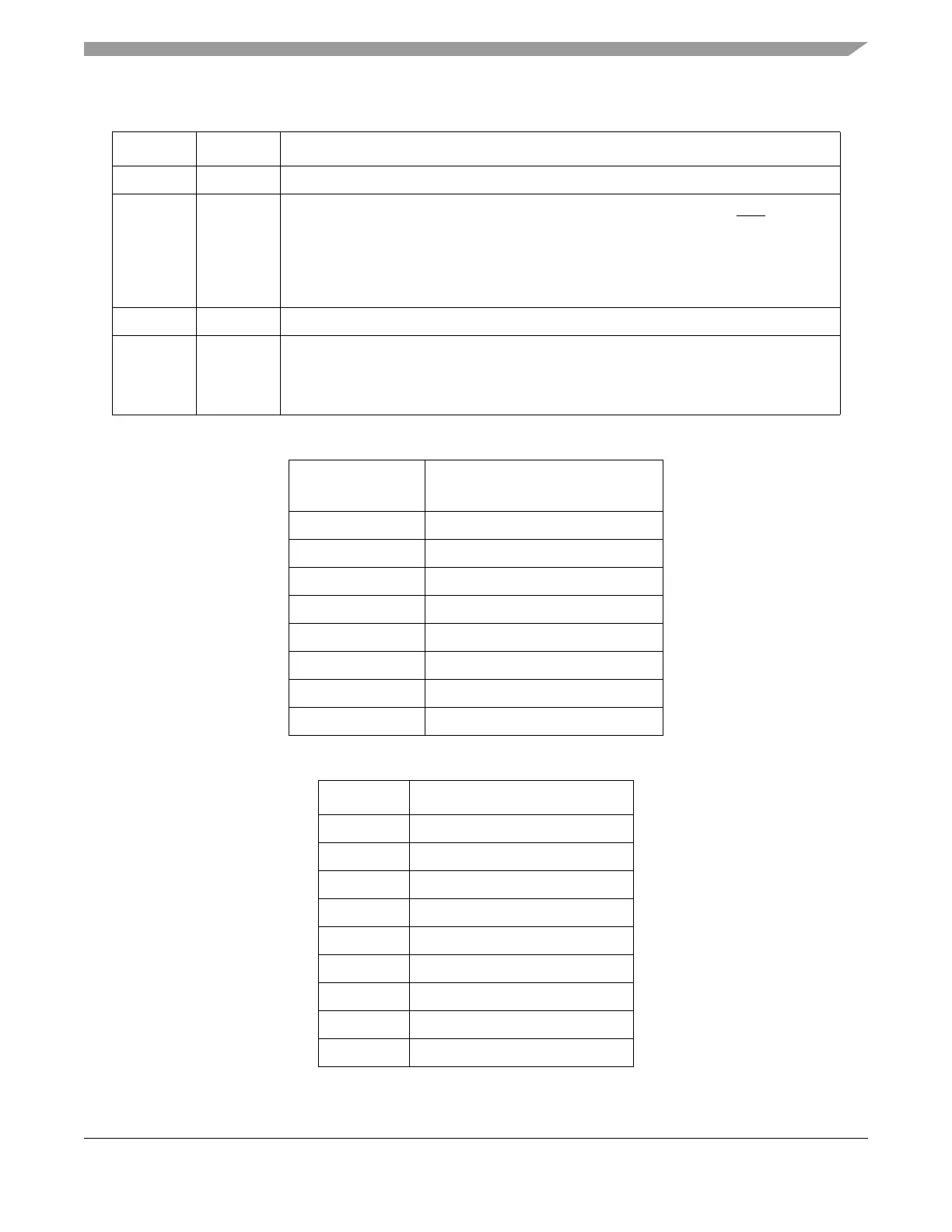

Table 19-21. System Clock Divide Factor for Baud Clock

BR[0:3] System Clock Divide Factor

1

0b0000 2

0b0001 3

0b0010 4

0b0011 5

0b0100 6

0b0101 7

0b0110 8

0b0111 9

0b1000 10

Loading...

Loading...