MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-34 Freescale Semiconductor

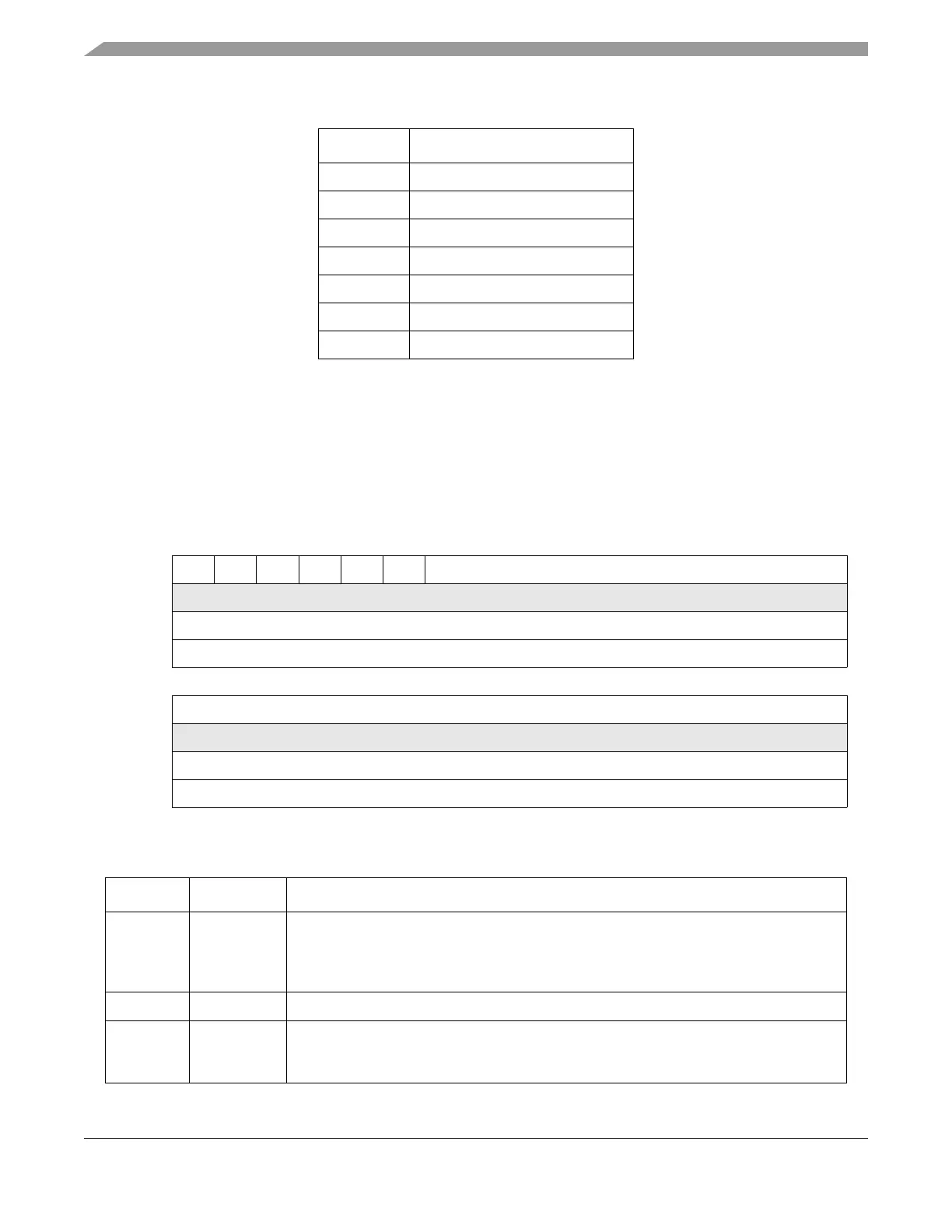

19.3.2.13 eQADC SSI Receive Data Register (EQADC_SSIRDR)

The eQADC SSI receive data register (EQADC_SSIRDR) records the last message received from the

external device.

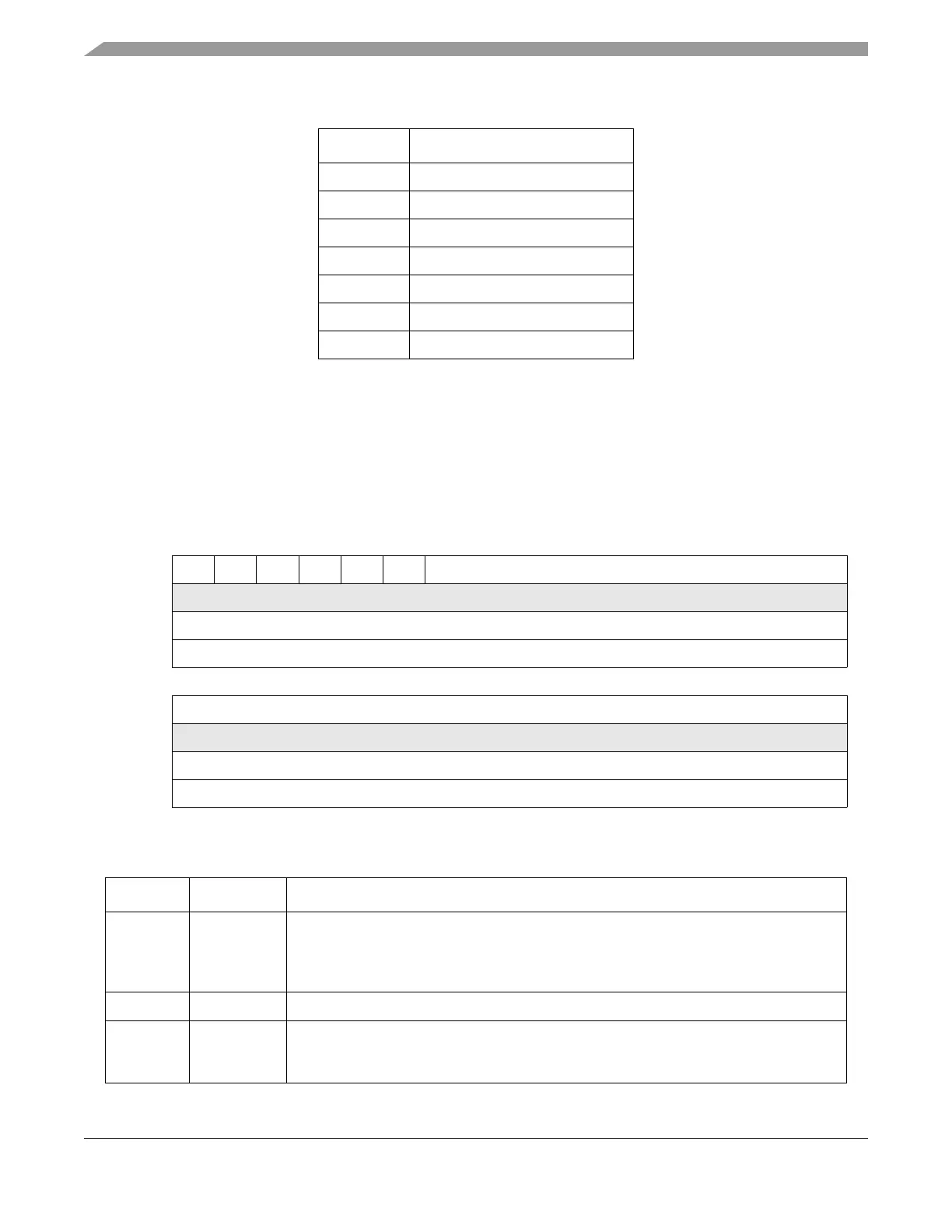

0b1001 11

0b1010 12

0b1011 13

0b1100 14

0b1101 15

0b1110 16

0b1111 17

1

If the system clock is divided by a odd number

then the serial clock will have a duty cycle

different from 50%.

0123456789101112131415

RRDV00000 R_DATA

W

Reset0000000000001111

Reg Addr Base + 0x00B8

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RR_DATA

W

Reset0000000000000000

Reg Addr Base + 0x00B8

Figure 19-16. eQADC SSI Receive Data Register (EQADC_SSIRDR)

Table 19-22. EQADC_SSIRDR Field Descriptions

Bits Name Description

0RDV

Receive data valid. Indicates if the last received data is valid. This bit is cleared

automatically whenever the EQADC_SSIRDR is read. Writes have no effect.

0 Receive data is not valid.

1 Receive data is valid.

1–5 — Reserved.

6–31 R_DATA

[0:25]

eQADC receive DATA. Contains the last result message that was shifted in. Writes to the

R_DATA have no effect. Messages that were not completely received due to a transmission

abort will not be copied into EQADC_SSIRDR.

Table 19-21. System Clock Divide Factor for Baud Clock (Continued)

BR[0:3] System Clock Divide Factor

1

Loading...

Loading...