MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

19-56 Freescale Semiconductor

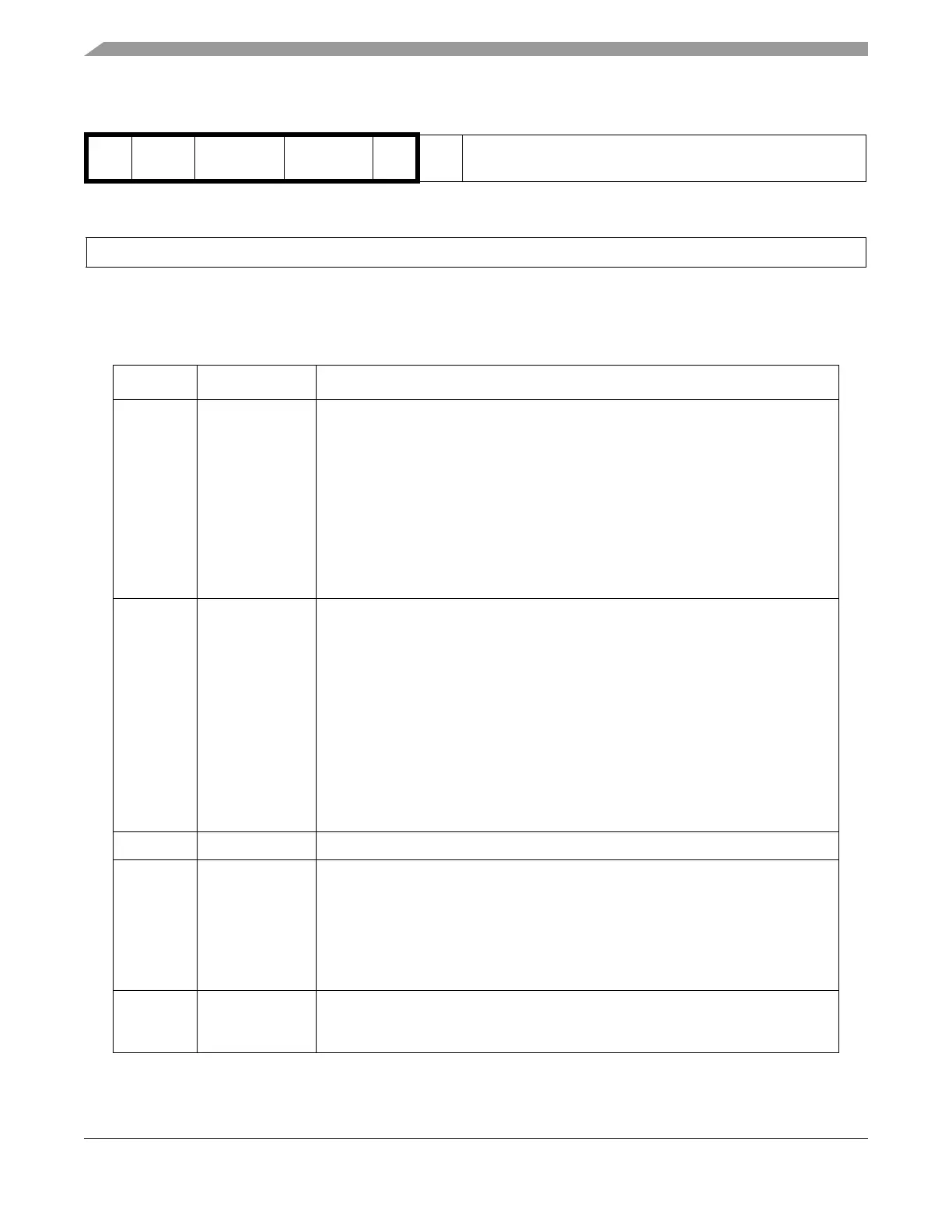

0 1 23 4 56789101112131415

EOQ PAUSE Reserved ABORT_ST EB

(0b1)

BN OFF_CHIP_COMMAND

CFIFO Header ADC Command

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

OFF_CHIP_COMMAND

ADC Command

Figure 19-31. Command Message Format for External Device Operation

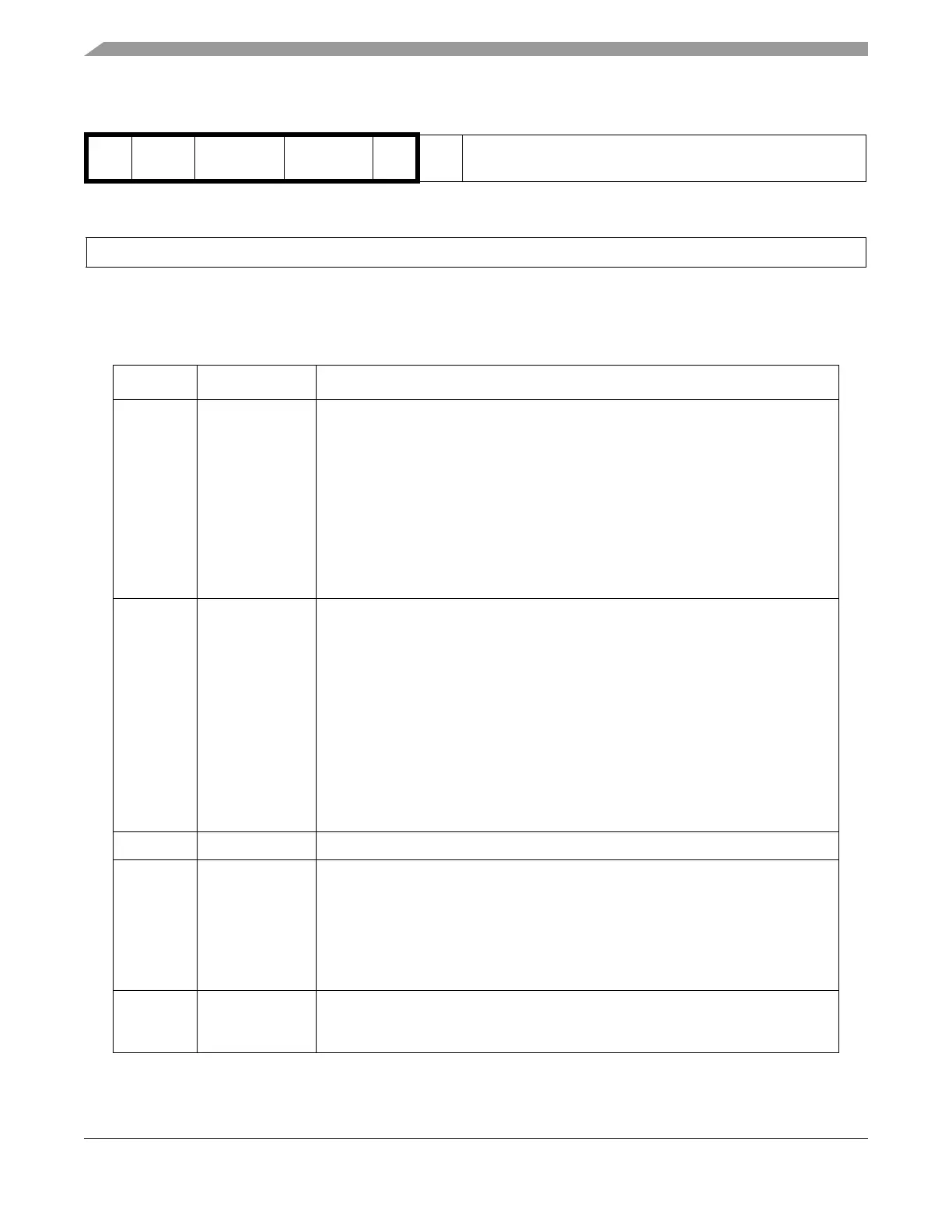

Table 19-40. On-Chip ADC Field Descriptions: External Device Operation

Bits Name Description

0 EOQ End-of-queue. Asserted in the last command of a command queue to indicate to the

eQADC that a scan of the queue is completed. EOQ instructs the eQADC to reset

its current CFIFO transfer counter value (TC_CF) to 0. Depending on the CFIFO

mode of operation, the CFIFO status will also change upon the detection of an

asserted EOQ bit on the last transferred command. See Section 19.4.3.5, “CFIFO

Scan Trigger Modes,” for details.

0 Not the last entry of the command queue.

1 Last entry of the command queue.

Note: If both the pause and EOQ bits are asserted in the same command message

the respective flags are set, but the CFIFO status changes as if only the EOQ bit

were asserted.

1 PAUSE Pause bit. Allows software to create sub-queues within a command queue. When the

eQADC completes the transfer of a command with an asserted pause bit, the CFIFO

enters the WAITING FOR TRIGGER state. Refer to Section 19.4.3.6.1, “CFIFO

Operation Status,” for a description of the state transitions. The pause bit is only valid

when CFIFO operation mode is configured to single or continuous-scan edge trigger

mode.

0 Do not enter WAITING FOR TRIGGER state after transfer of the current

command message.

1 Enter WAITING FOR TRIGGER state after transfer of the current command

message.

Note: If both the pause and EOQ bits are asserted in the same command message

the respective flags are set, but the CFIFO status changes as if only the EOQ bit

were asserted.

2–3 — Reserved.

4 ABORT_ST ABORT serial transmission. Indicates whether an on-going serial transmission

should be aborted or not. All CFIFOs can abort null message transmissions when

triggered but only CFIFO0 can abort command transmissions of lower priority

CFIFOs. For more on serial transmission aborts see Section 19.4.3.2, “CFIFO

Prioritization and Command Transfer.”

0 Do not abort current serial transmission.

1 Abort current serial transmission.

5 EB External buffer. This bit should always be set for messages sent to an external ADC.

0 Command is sent to an internal command buffer.

1 Command is sent to an external command buffer.

Loading...

Loading...