MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-29

20.3.2.11 DSPI DSI Serialization Data Register (DSPIx_SDR)

The DSPIx_SDR contains the signal states of the parallel input signals from the eTPU or the eMIOS. The

pin states of the parallel input signals are latched into the DSPIx_SDR on the rising edge of every system

clock. The DSPIx_SDR is read-only. When the TXSS bit in the DSPIx_DSICR is negated, the data in the

DSPIx_SDR is the source of the serialized data.

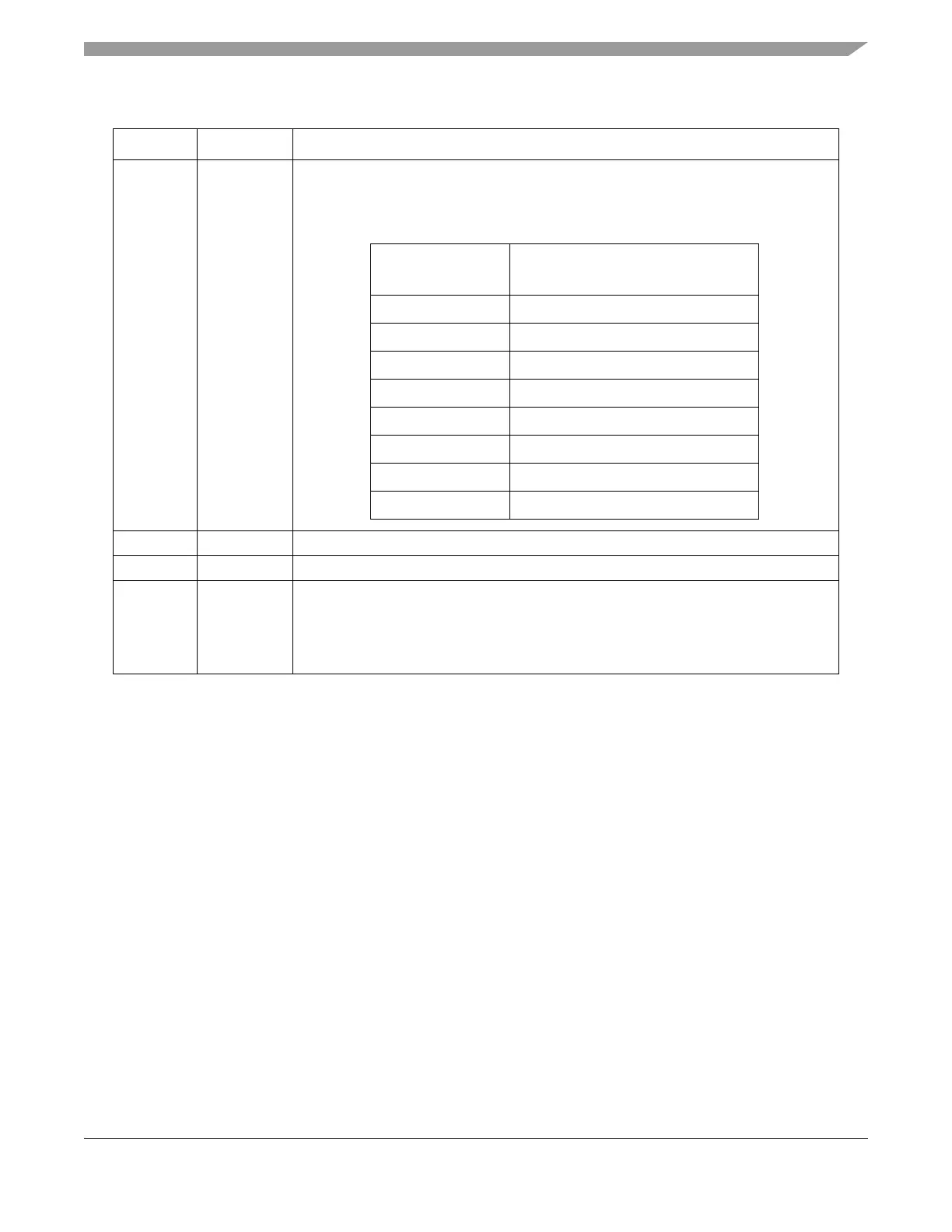

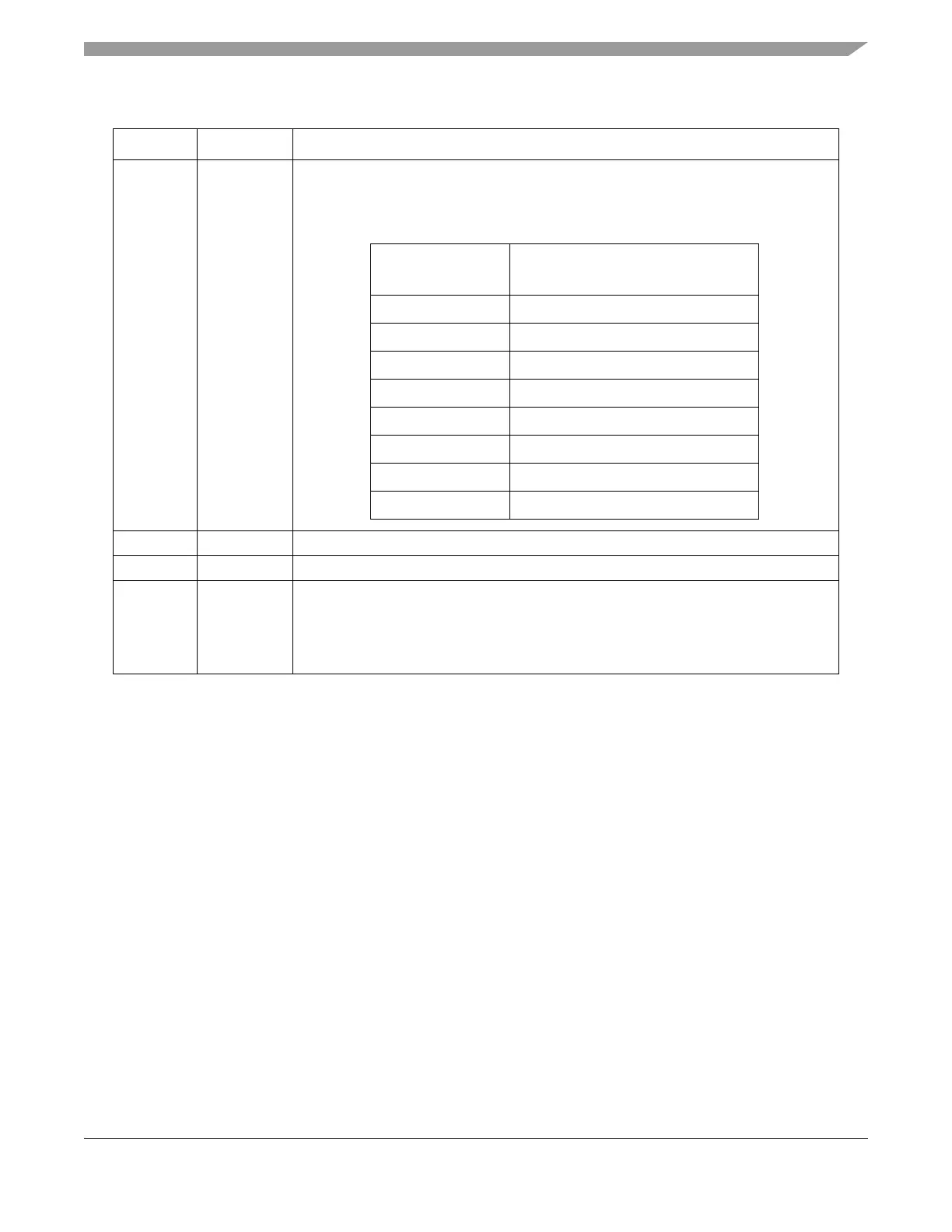

17–19 DSICTAS

[0:2]

DSI clock and transfer attributes select. The DSICTAS field selects which of the

DSPIx_CTARs is used to provide transfer attributes in DSI configuration. The DSICTAS

field is used in DSI master mode. In DSI slave mode, the DSPIx_CTAR1 is always

selected. The table below shows how the DSICTAS values map to the DSPIx_CTARs.

20–23 — Reserved.

24–25 — Reserved, but implemented. These bits are writable, but have no effect.

26–31 DPCSn DSI peripheral chip select n. The DPCS bits select which of the PCS signals to assert

during a DSI transfer. The DPCS bits only control the assertions of the PCS signals in

DSI master mode.

0 Negate PCSn

1 Assert PCSn

Table 20-12. DSPIx_DSICR Field Descriptions (Continued)

Bits Name Description

DSICTAS

DSI Clock and Transfer Attributes

Controlled by

000 DSPIx_CTAR0

001 DSPIx_CTAR1

010 DSPIx_CTAR2

011 DSPIx_CTAR3

100 DSPIx_CTAR4

101 DSPIx_CTAR5

110 DSPIx_CTAR6

111 DSPIx_CTAR7

Loading...

Loading...