MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

20-28 Freescale Semiconductor

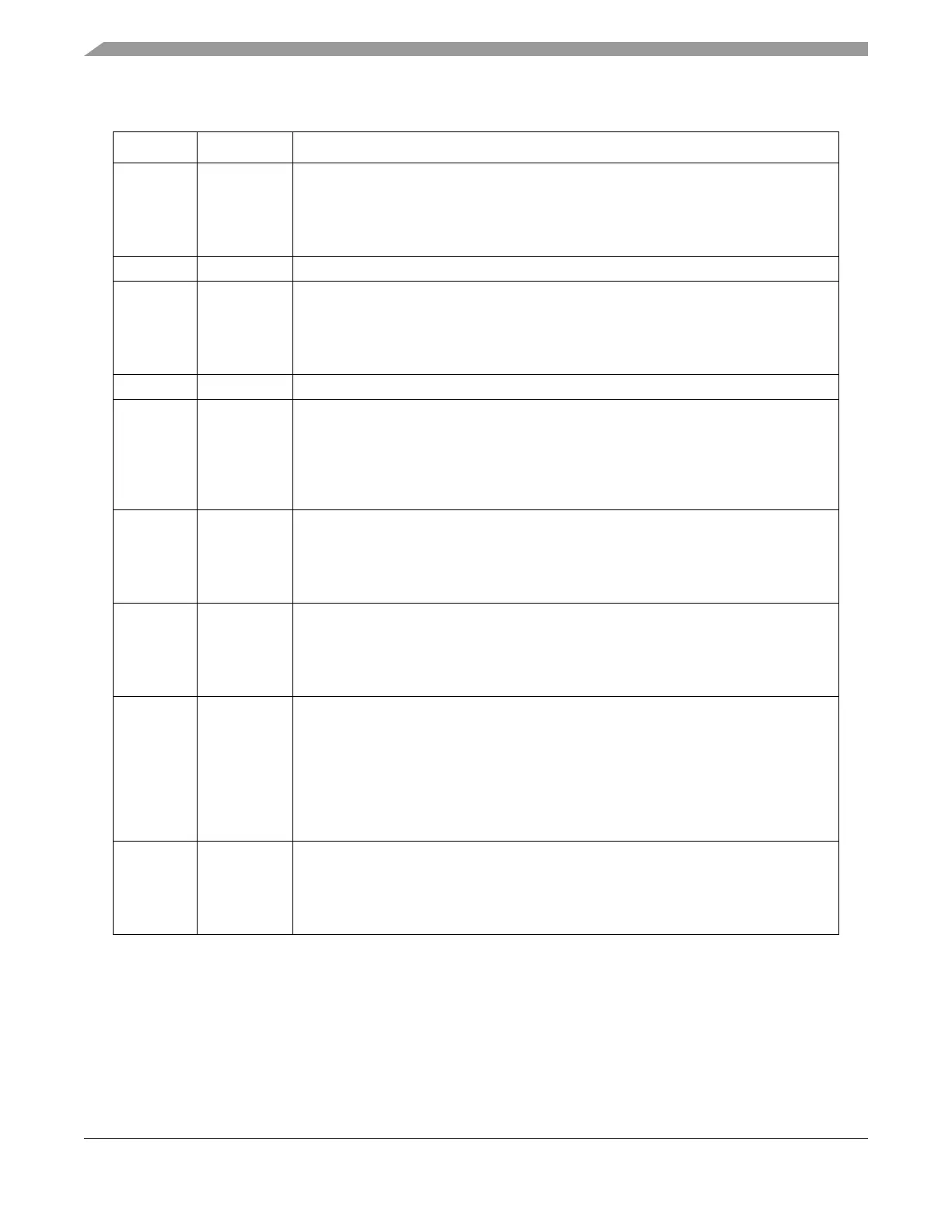

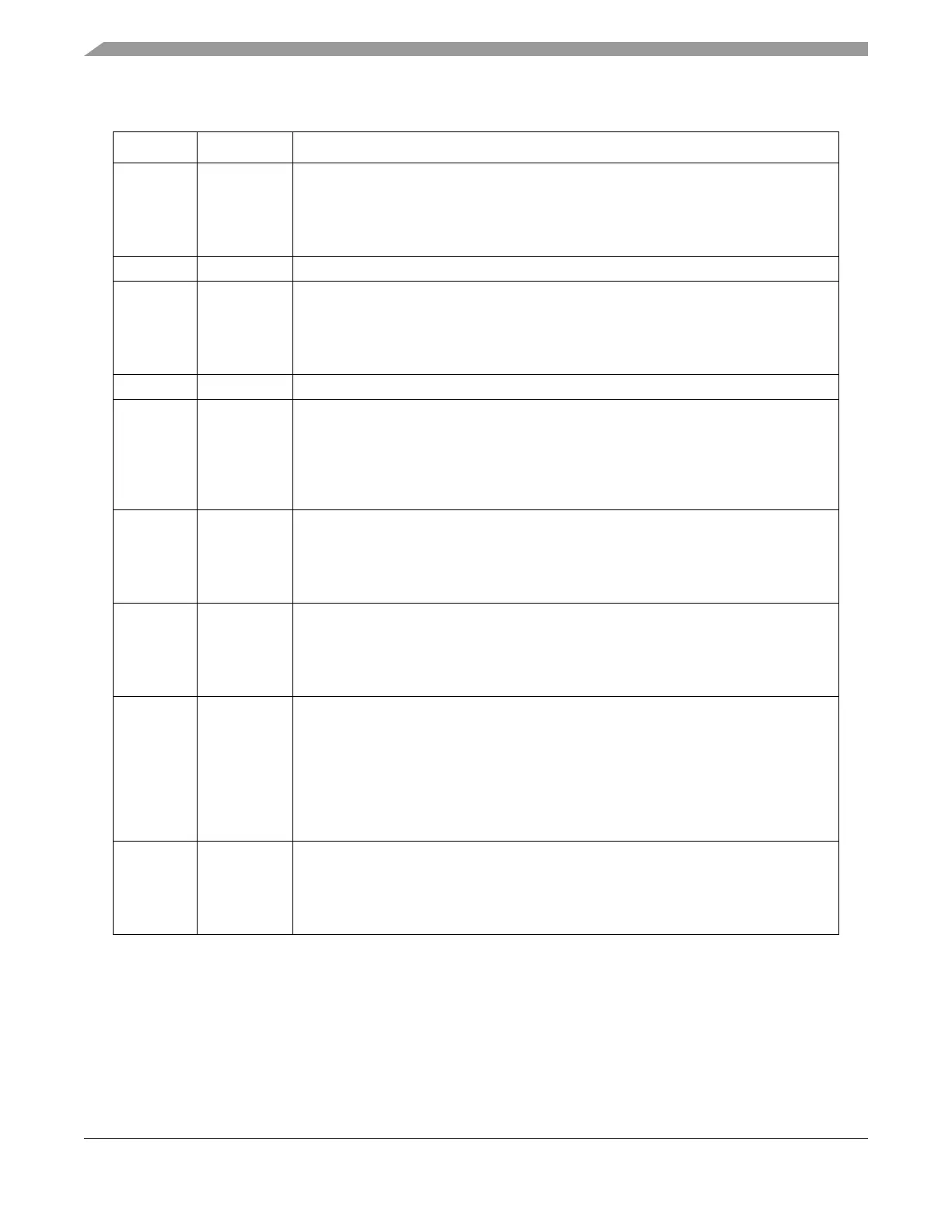

Table 20-12. DSPIx_DSICR Field Descriptions

Bits Name Description

0 MTOE Multiple transfer operation enable. Enables multiple DSPIs to be connected in a parallel

or serial configuration. See Section 20.4.4.7, “Multiple Transfer Operation (MTO),” for

more information.

0 Multiple transfer operation disabled

1 Multiple transfer operation enabled

1 — Reserved.

2–7 MTOCNT

[0:5]

Multiple transfer operation count. Selects number of bits to be shifted out during a

transfer in multiple transfer operation. The field sets the number of SCK cycles that the

bus master will generate to complete the transfer. The number of SCK cycles used will

be one more than the value in the MTOCNT field. The number of SCK cycles defined by

MTOCNT must be equal to or greater than the frame size.

8–11 — Reserved.

12 TXSS Transmit data source select. Selects the source of data to be serialized. The source can

be either data from host software written to the DSPI DSI alternate serialization data

register (DSPIx_ASDR), or parallel output pin states latched into the DSPI DSI

serialization data register (DSPIx_SDR).

0 Source of serialized data is the DSPIx_SDR

1 Source of serialized data is the DSPIx_ASDR

13 TPOL Trigger polarity. Selects the active edge of the internal hardware trigger input signal (ht).

The bit selects which edge will initiate a transfer in the DSI configuration. See

Section 20.4.4.5, “DSI Transfer Initiation Control,” for more information.

0 Falling edge will initiate a transfer

1 Rising edge will initiate a transfer

14 TRRE Trigger reception enable. Enables the DSPI to initiate a transfer when an external trigger

signal is received. The bit is only valid in DSI configuration. See Section 20.4.4.5, “DSI

Transfer Initiation Control,” for more information.

0 Trigger signal reception disabled

1 Trigger signal reception enabled

15 CID Change in data transfer enable. Enables a change in serialization data to initiate a

transfer. The bit is used in master mode in DSI and CSI configurations to control when

to initiate transfers. When the CID bit is set, serialization is initiated when the current DSI

data differs from the previous DSI data shifted out. The DSPIx_COMPR is compared

with the DSPIx_SDR or DSPIx_ASDR to detect a change in data. Refer to

Section 20.4.4.5, “DSI Transfer Initiation Control,” for more information.

0 Change in data transfer operation disabled

1 Change in data transfer operation enabled

16 DCONT DSI continuous peripheral chip select enable. Enables the PCS signals to remain

asserted between transfers. The DCONT bit only affects the PCS signals in DSI master

mode. See Section 20.4.7.5, “Continuous Selection Format,” for details.

0 Return peripheral chip select signals to their inactive state after transfer is complete

1 Keep peripheral chip select signals asserted after transfer is complete

Loading...

Loading...