MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 20-45

20.4.4.7 Multiple Transfer Operation (MTO)

In DSI configuration the MTO feature allows for multiple DSPIs within the MPC5553/MPC5554 to be

chained together in a parallel or serial configuration. The parallel chaining allows multiple DSPIs internal

to the MPC5553/MPC5554 and multiple SPI devices external to the MPC5553/MPC5554 to share SCK

and PCS signals thereby saving pins. The serial chaining allows bits from multiple DSPIs to be

concatenated into a single DSI frame. MTO is enabled by setting the MTOE bit in the DSPIx_DSICR.

In parallel and serial chaining there is one bus master and multiple bus slaves. The bus master initiates and

controls the transfers, but the DSPI slaves generate trigger signals for the bus DSPI master when an

internal condition in the slave warrants a transfer. The DSPI slaves also propagate triggers from other

slaves to the master. When a DSPI slave detects a trigger signal on its ht input, the slave generates a trigger

signal on the MTRIG output.

The SIU_DISR must be configured to use serial or parallel chaining.

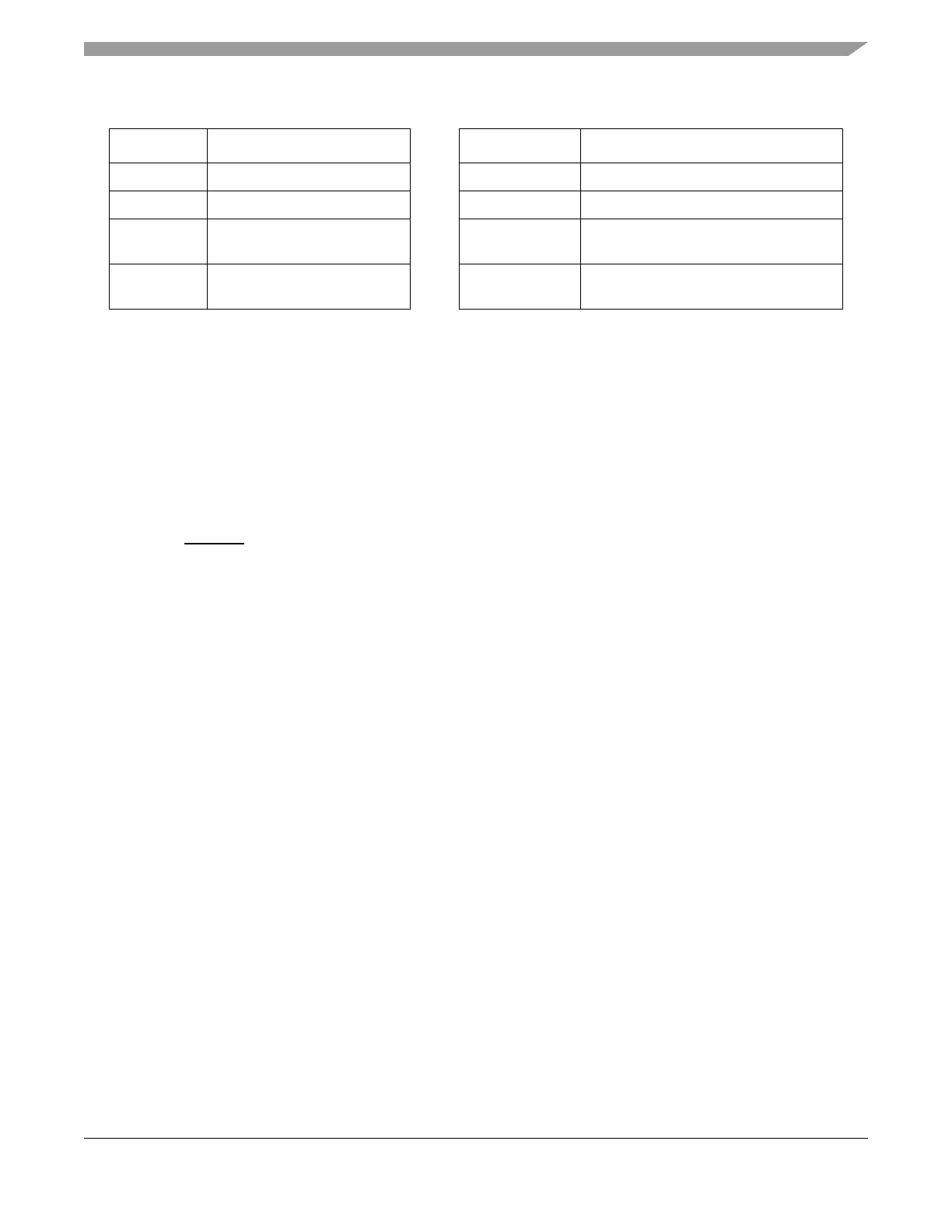

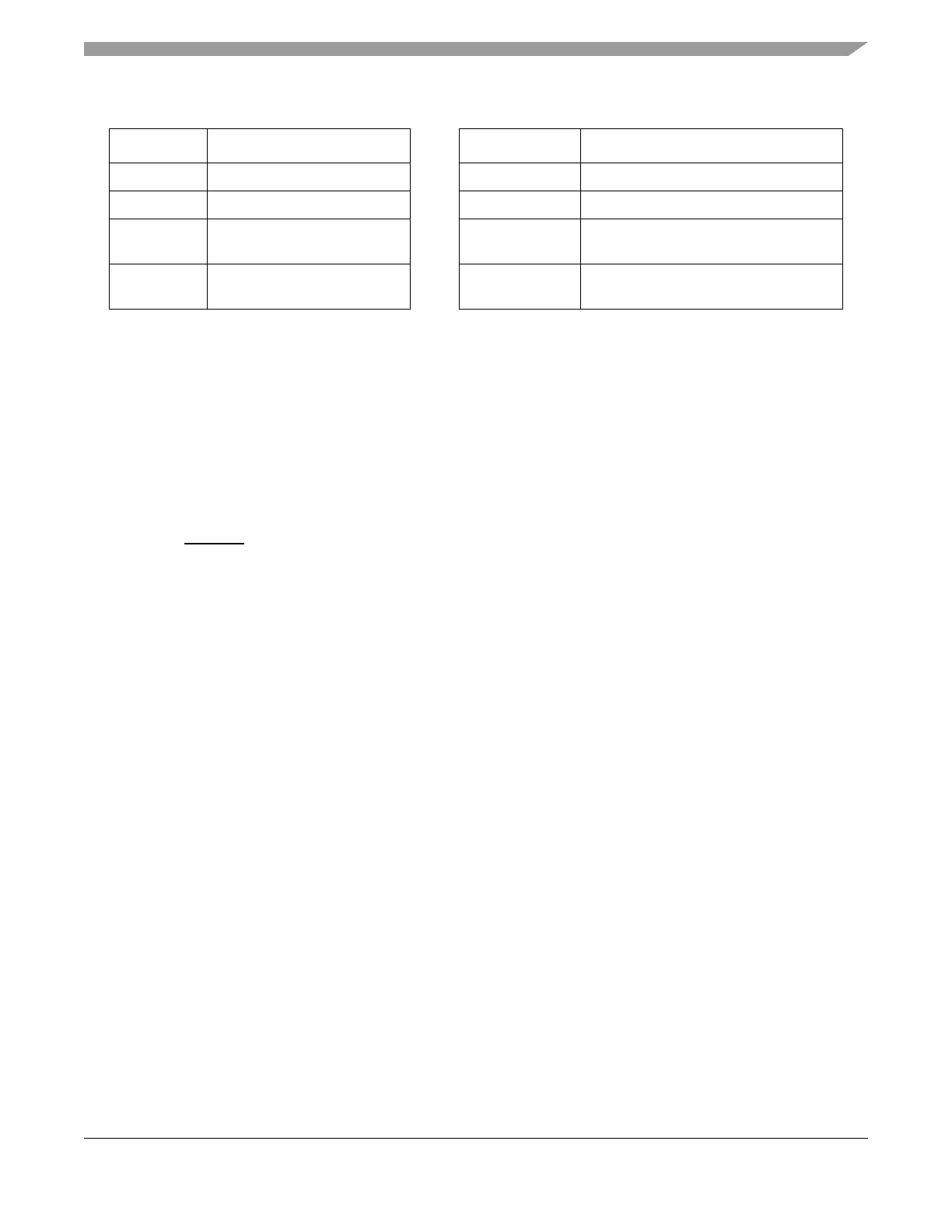

12 eTPU_A Output Channel 27 12 Input 3 on IMUX for External IRQ[10]

13 eTPU_A Output Channel 26 13 Input 3 on IMUX for External IRQ[11]

14 eTPU_A Output Channel 25 14 EMIOS Input Channel 15,

Input 3 on IMUX for External IRQ[12]

15 eTPU_A Output Channel 24 15 EMIOS Input Channel 14,

Input 3 on IMUX for External IRQ[13]

Table 20-22. DSPI_D Connectivity Table (Continued)

DSPI_D IN[n] Connected to: DSPI_D OUT[n] Connected to:

Loading...

Loading...