MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

21-18 Freescale Semiconductor

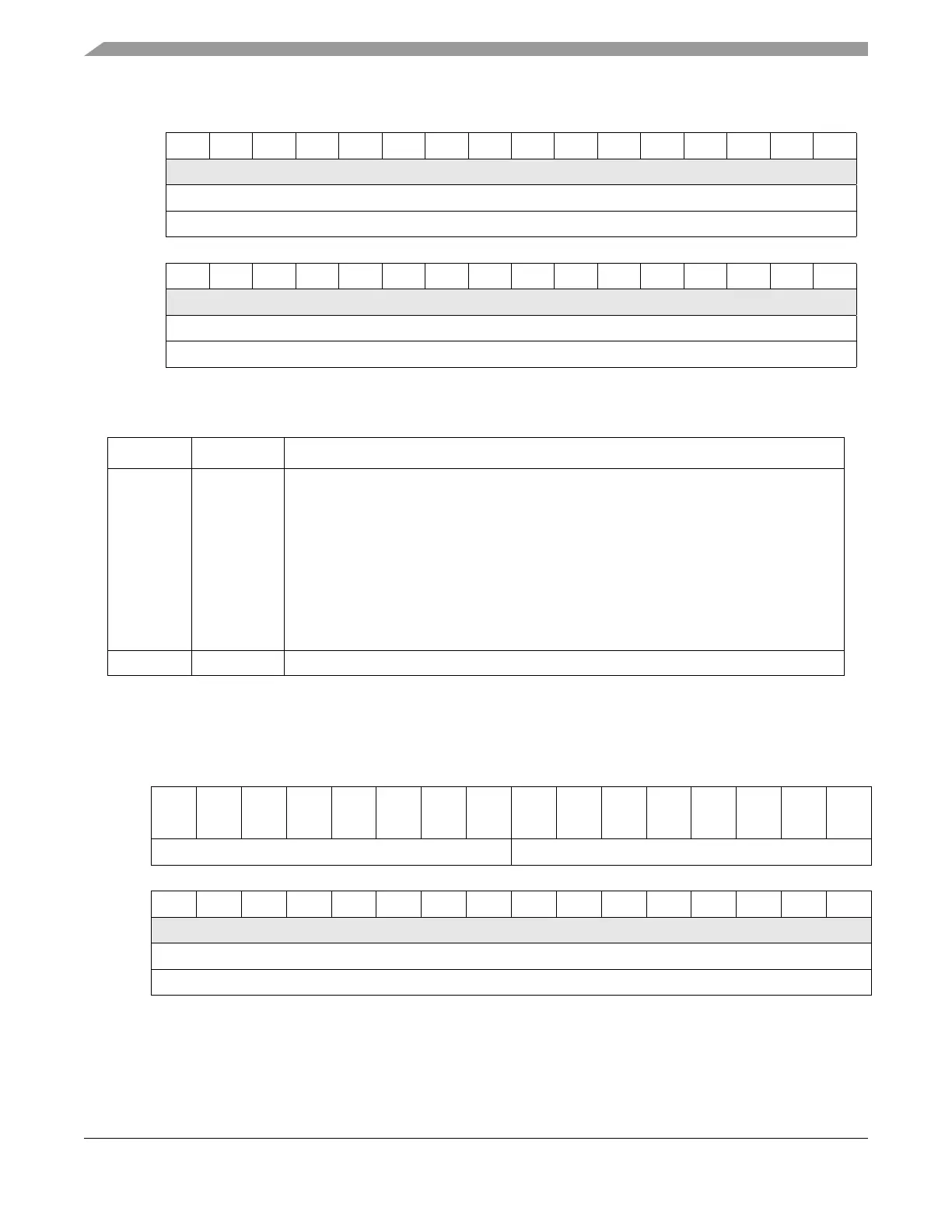

21.3.3.8 LIN CRC Polynomial Register (ESCIx_LPR)

ESCIx_LPRn can be written when there are no ongoing transmissions.

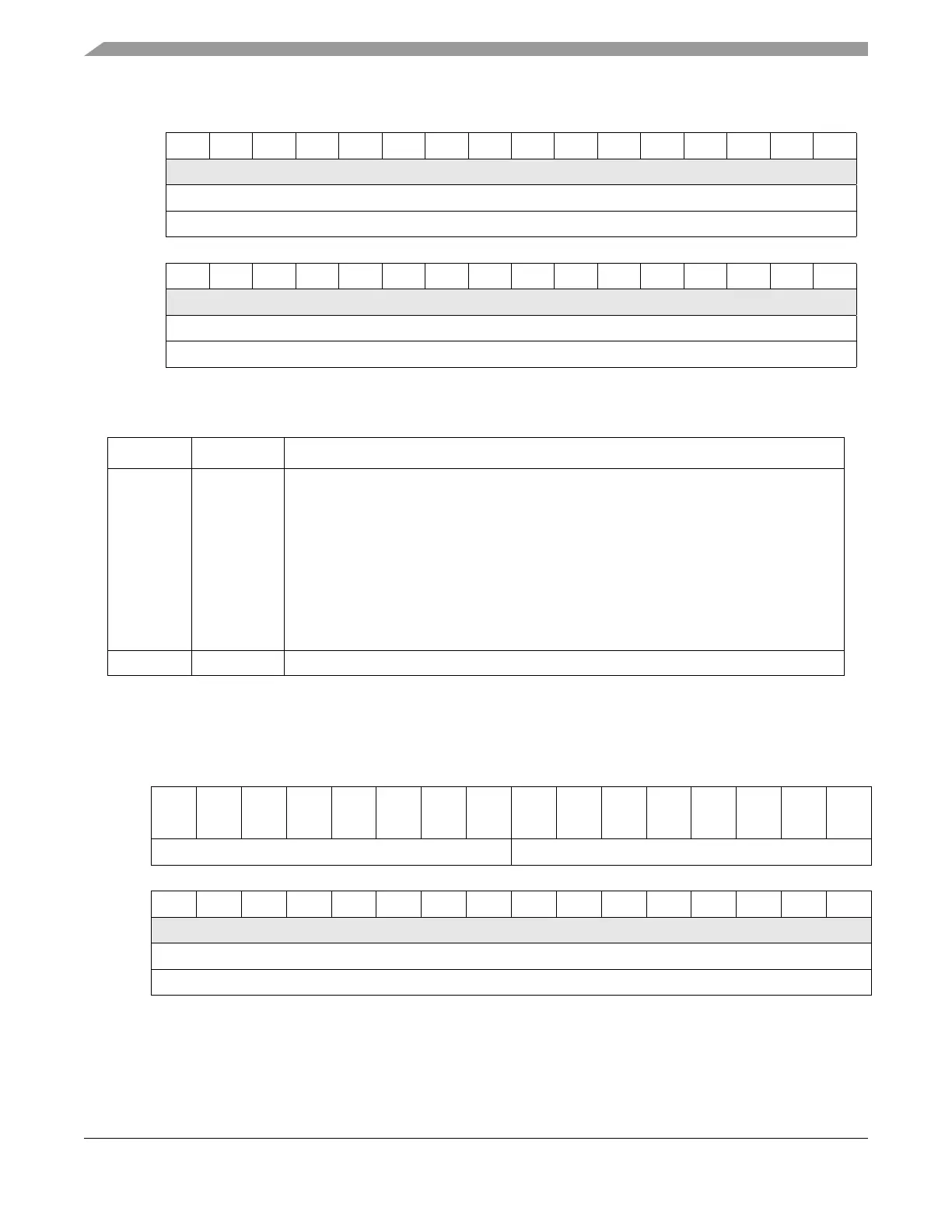

0123456789101112131415

R D7 D6 D5 D4 D3 D2 D1 D0 00000000

W

Reset 0000000000000000

Reg Addr Base + 0x0014

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x0014

Figure 21-9. LIN Receive Register (ESCIx_LRR)

Table 21-13. ESCIx_LRR Field Descriptions

Bits Name Description

0–7 Dn Data bit n. Provides received data bytes from RX frames. Data is only valid when the

ESCIx_SR[RXRDY] flag is set. CRC and checksum information will not be available in the

ESCIx_LRR unless they are treated as data. It is possible to treat CRC and checksum

bytes as data by deactivating the CSUM respectively CRC control bits in the ESCIx_LTR;

however, then CRC and CSUM checking has to be performed by software.

Data bytes must be read from the ESCIx_LRR (by CPU or DMA) before any new bytes

(including CRC or checksum) are received from the LIN bus otherwise the data byte is lost

and OVFL is set.

Note: The data must be collected and the LIN frame finished (including CRC and

checksum if applicable) before a wake-up character can be sent.

8–31 — Reserved.

0123456789101112131415

RP15P14P13P12P11P10P9P8P7P6P5P4P3P2P1P0

W

Reset1100010110011001

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x0018

Figure 21-10. LIN CRC Polynomial Register (ESCIx_LPR)

Loading...

Loading...