MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 21-17

21.3.3.7 LIN Receive Register (ESCIx_LRR)

ESCIx_LRR can be ready only when ESCIx_SR[RXRDY] is set.

NOTE

Application software must ensure that ESCIx_LRR be read before new data

or checksum bytes or CRCs are received from the LIN bus.

4–7 Tn Timeout bit n. Sets the counter to determine a NO_RESPONSE_ERROR, if the frame is a

read access to a LIN slave. Following LIN standard rev 1.3, the value

(10 N

DATA

+ 45) 1.4 is recommended. For transmissions, this counter has to be set to

0. The timeout bits 7–0 will not be written on a TX frame. For TX frames, the fourth byte

written to the LIN transmit register (ESCIx_LTR) is the first data byte, for RX frames it

contains timeout bits 7–0.The time is specified in multiples of bit times. The timeout period

starts with the transmission of the LIN break character.

8–31 — Reserved.

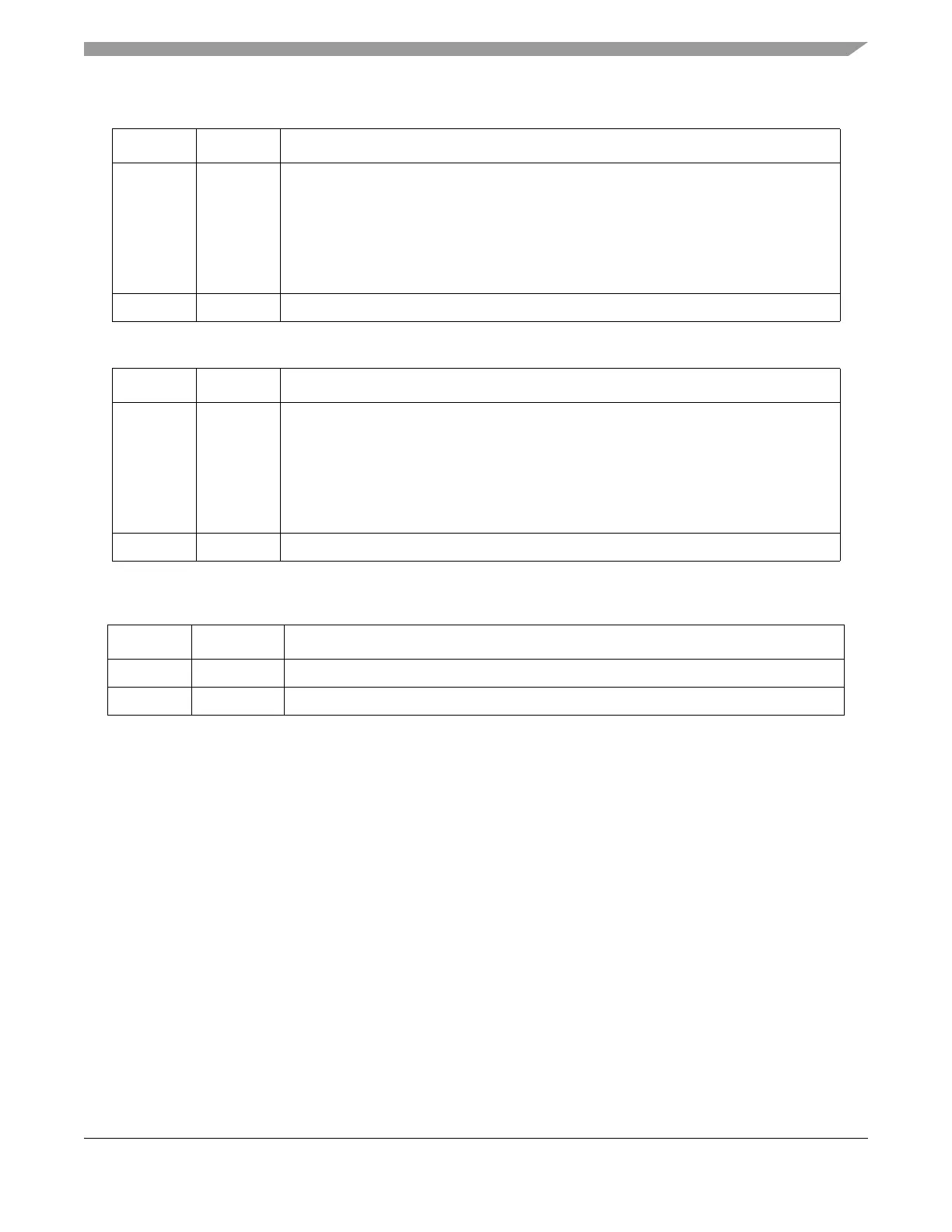

Table 21-11. ESCIx_LTR Rx Frame Fourth Byte Field Descriptions

Bits Name Description

0–7 Tn Timeout bit n. Sets the counter to determine a NO_RESPONSE_ERROR, if the frame is a

read access to a LIN slave. Following LIN standard rev 1.3, the value

(10 N

DATA

+ 45) 1.4 is recommended. For transmissions, this counter has to be set to

0. The timeout bits 7–0 will not be written on a TX frame. For TX frames, the fourth byte

written to the LIN transmit register (ESCIx_LTR) is the first data byte. For RX frames, it

contains timeout bits 7–0.The time is specified in multiples of bit times. The timeout period

starts with the transmission of the LIN break character.

8–31 — Reserved.

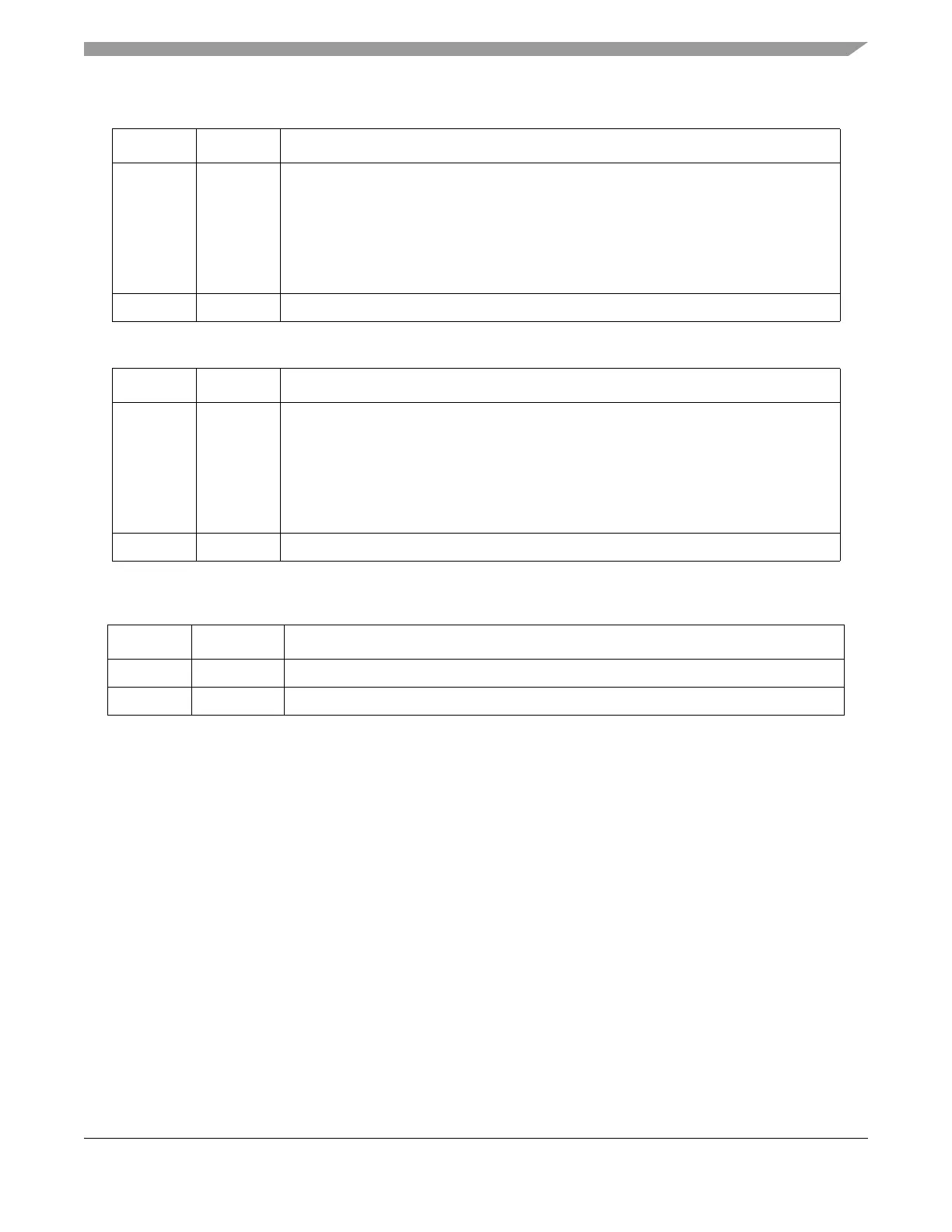

Table 21-12. ESCIx_LTR Tx Frame Fourth+ Byte/

Rx Frame Fifth+ Byte Field Description

Bits Name Description

0–7 Dn Data bits for transmission.

8–31 — Reserved.

Table 21-10. ESCIx_LTR Third Byte Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...