MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

22-12 Freescale Semiconductor

22.3.3.2 Control Register (CANx_CR)

CANx_CR is defined for specific FlexCAN2 control features related to the CAN bus, such as bit-rate,

programmable sampling point within an RX bit, loop-back mode, listen-only mode, bus off recovery

behavior, and interrupt enabling (for example, bus-off, error). It also determines the division factor for the

clock prescaler. Most of the fields in this register should only be changed while the module is disabled or

in freeze mode. Exceptions are the BOFFMSK, ERRMSK, and BOFFREC bits, which can be accessed at

any time. Note that CANx_CR is unaffected by soft reset (which occurs when CAN_MCR[SOFTRST] is

asserted).

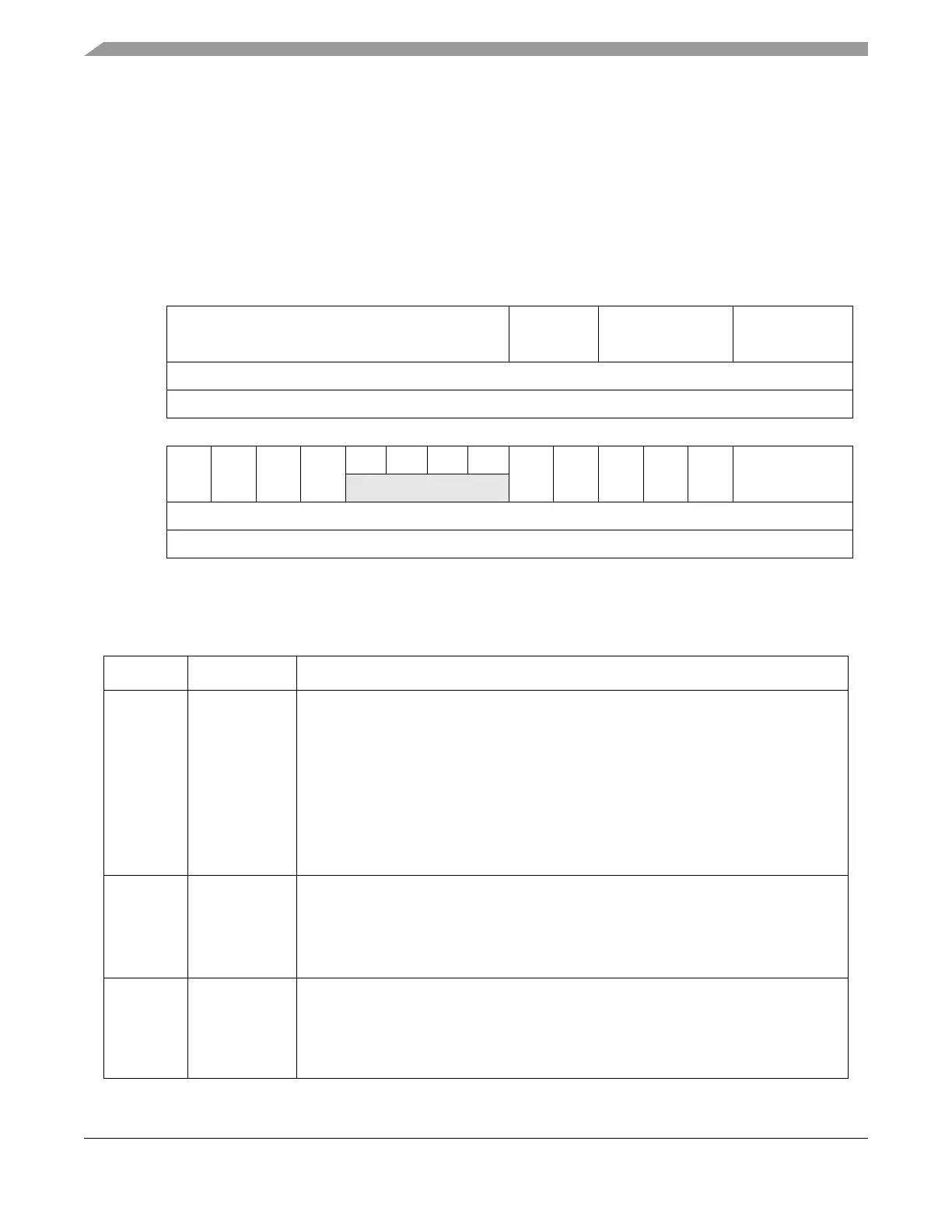

01234567 8 9101112131415

R PRESDIV RJW PSEG1 PSEG2

W

Reset0000000000000000

Reg Addr Base + 0x0004

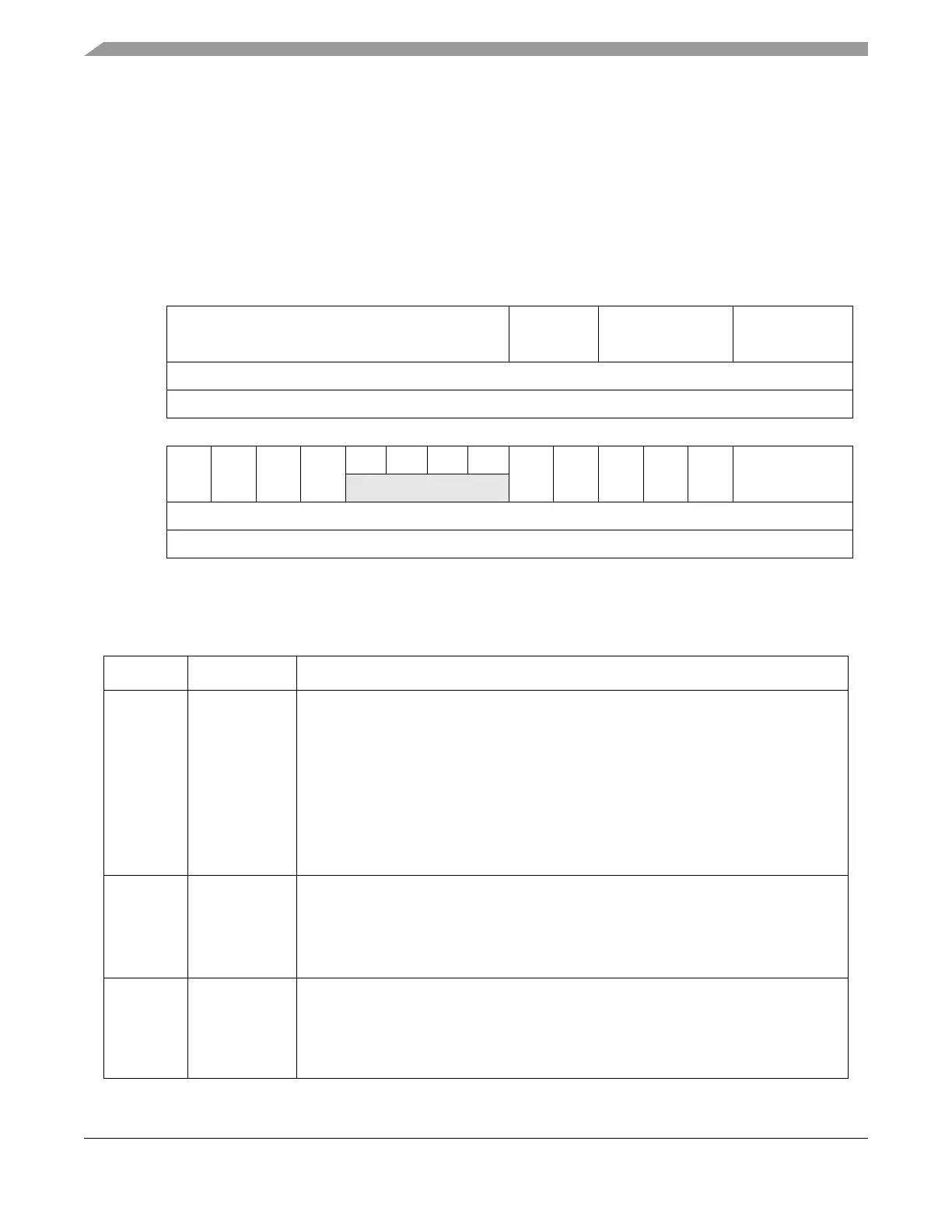

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RBOFF

MSK

ERR

MSK

CLK_

SRC

LPB0000SMPBOFF

REC

TSYN LBUF LOM PROPSEG

W

Reset0000000000000000

Reg Addr Base + 0x0004

1

CANx_CR is unaffected by soft reset (which occurs when CAN_MCR[SOFTRST] is asserted).

Figure 22-4. Control Register (CANx_CR)

Table 22-8. CANx_CR Field Descriptions

Bits Name Description

0–7 PRESDIV

[0:7]

Prescaler division factor. Defines the ratio between the CPI clock frequency and the serial

clock (SCK) frequency. The SCK period defines the time quantum of the CAN protocol.

For the reset value, the SCK frequency is equal to the CPI clock frequency. The maximum

value of this register is 0xFF, that gives a minimum SCK frequency equal to the CPI clock

frequency divided by 256. For more information, refer to Section 22.4.5.4, “Protocol

Timing.”

8–9 RJW

[0:1]

Resync jump width. Defines the maximum number of time quanta

1

that a bit time can be

changed by one re-synchronization. The valid programmable values are 0–3.

10–12 PSEG1

[0:2]

Phase segment 1. Defines the length of phase buffer segment 1 in the bit time. The valid

programmable values are 0–7.

S-clock frequency

CPI clock frequency

PRESDIV 1+

-----------------------------------------------------=

Resync Jump Width RJW + 1=

Phase Buffer Segment 1 PSEG1 + 1Time Quanta=

Loading...

Loading...