MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 22-13

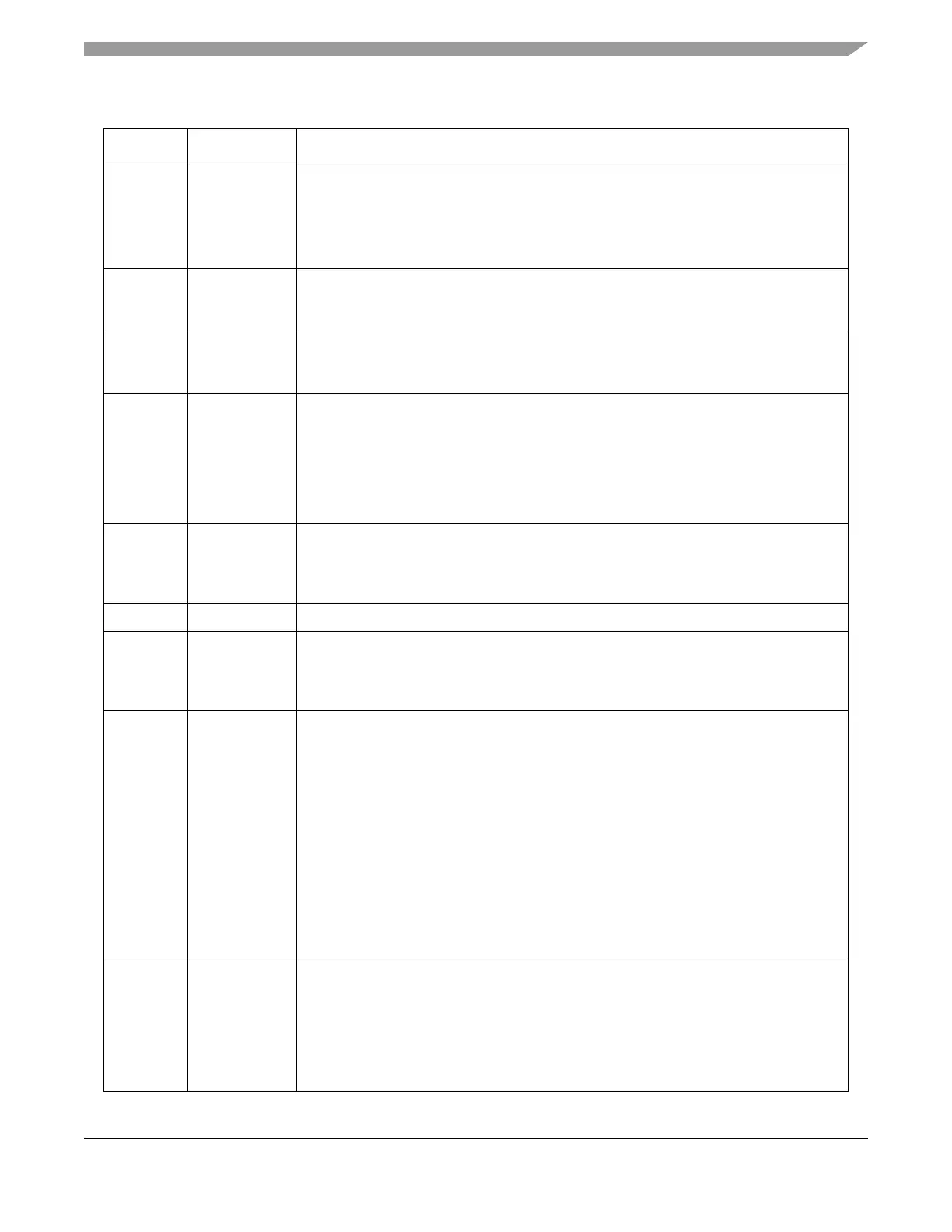

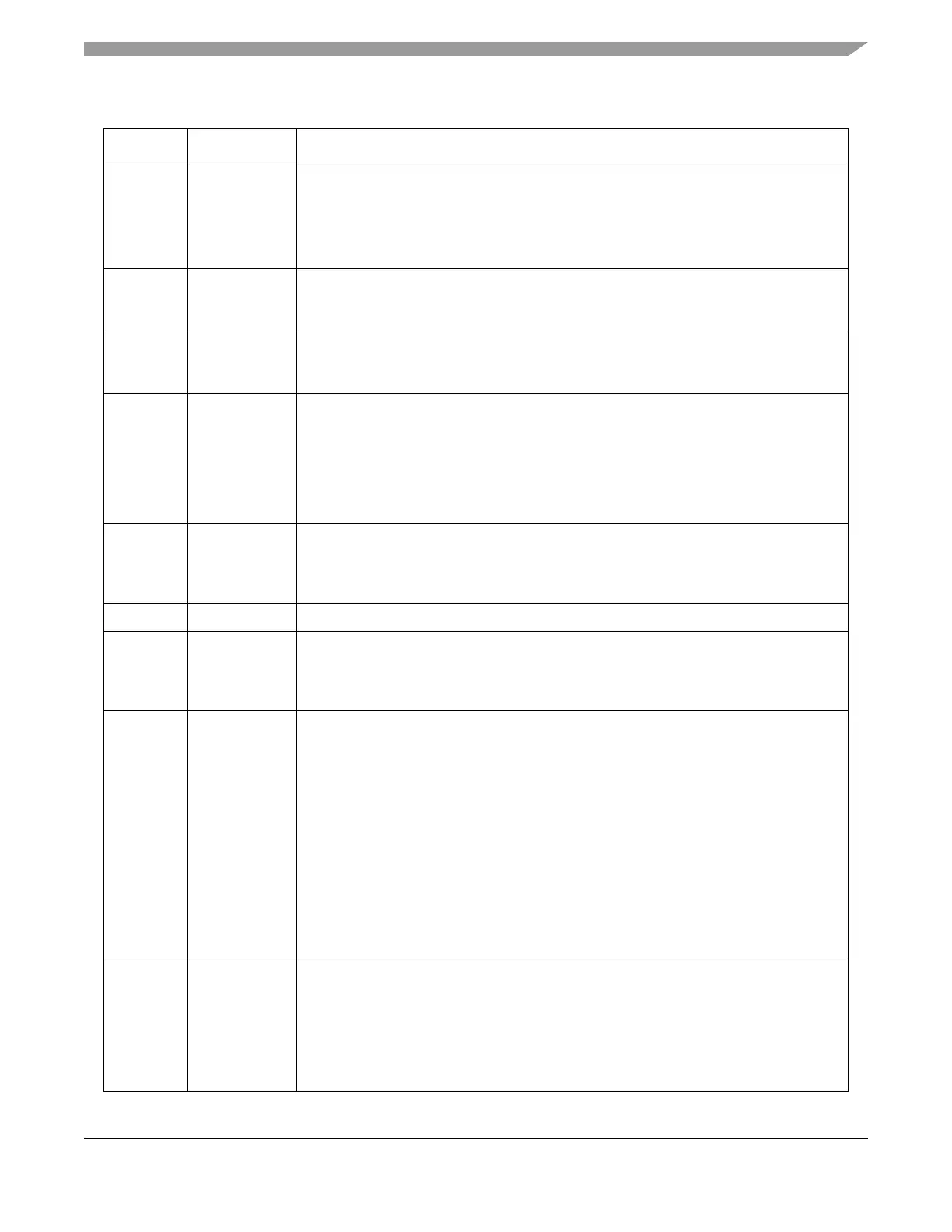

13–15 PSEG2

[0:2]

Phase segment 2. Defines the length of phase buffer segment 2 in the bit time. The valid

programmable values are 1–7.

16 BOFFMSK Bus off mask. Provides a mask for the bus off interrupt.

0 Bus off interrupt disabled

1 Bus off interrupt enabled

17 ERRMSK Error mask. Provides a mask for the error interrupt.

0 Error interrupt disabled

1 Error interrupt enabled

18 CLK_SRC CAN engine clock source. Selects the clock source to the CAN Protocol Interface (CPI)

to be either the system clock (driven by the PLL) or the crystal oscillator clock. The

selected clock is the one fed to the prescaler to generate the serial clock (SCK). In order

to guarantee reliable operation, this bit should only be changed while the module is

disabled.

0 = The CAN engine clock source is the oscillator clock

1 = The CAN engine clock source is the system clock

19 LPB Loop back. Configures FlexCAN2 to operate in loop-back mode. See Section 22.1.4,

“Modes of Operation” for information about this operating mode.

0 Loop back disabled

1 Loop back enabled

20–23 — Reserved.

24 SMP Sampling mode. Defines the sampling mode of each bit in the receiving messages (RX).

0 Just one sample is used to determine the RX bit value

1 Three samples are used to determine the value of the received bit: the regular one

(sample point) and 2 preceding samples, a majority rule is used

25 BOFFREC Bus off recovery mode. Defines how FlexCAN2 recovers from bus off state. If this bit is

negated, automatic recovering from bus off state occurs according to the CAN

Specification 2.0B. If the bit is asserted, automatic recovering from bus off is disabled and

the module remains in bus off state until the bit is negated by the user. If the negation

occurs before 128 sequences of 11 recessive bits are detected on the CAN bus, then bus

off recovery happens as if the BOFFREC bit had never been asserted. If the negation

occurs after 128 sequences of 11 recessive bits occurred, then FlexCAN2 will

re-synchronize to the bus by waiting for 11 recessive bits before joining the bus. After

negation, the BOFFREC bit can be re-asserted again during bus off, but it will only be

effective the next time the module enters bus off. If BOFFREC was negated when the

module entered bus off, asserting it during bus off will not be effective for the current bus

off recovery.

0 Automatic recovering from bus off state enabled, according to CAN Spec 2.0 part B

1 Automatic recovering from bus off state disabled

26 TSYN Timer sync mode. Enables a mechanism that resets the free-running timer each time a

message is received in message buffer 0. This feature provides means to synchronize

multiple FlexCAN2 stations with a special SYNC message (that is, global network time).

0 Timer sync feature disabled

1 Timer sync feature enabled

Note: There is a possibility of 4–5 ticks count skew between the different FlexCAN2

stations that would operate in this mode.

Table 22-8. CANx_CR Field Descriptions (Continued)

Bits Name Description

Phase Buffer Segment 2 PSEG2 + 1Time Quanta=

Loading...

Loading...