MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

22-18 Freescale Semiconductor

CANx_ESR). After the transition to the ‘error passive’ state, the TXECTR does not increment

anymore by acknowledge errors. Therefore the device never goes to the bus off state.

• If the RXECTR increases to a value greater than 127, it is not incremented further, even if more

errors are detected while being a receiver. At the next successful message reception, the counter is

set to a value between 119 and 127 to resume to ‘error active’ state.

22.3.3.6 Error and Status Register (CANx_ESR)

CANx_ESR reflects various error conditions, some general status of the device, and it is the source of two

interrupts to the CPU. The reported error conditions (bits 16–21) are those that occurred since the last time

the CPU read this register. The CPU read action clears BIT1ERR, BIT0ERR, ACKERR, CRCERR,

FRMERR, and STFERR. TXWRN, RXWRN, IDLE, TXRX, FLTCONF, BOFFINT, and ERRINT are

status bits.

Most bits in this register are read-only, except BOFFINT and ERRINT, which are interrupt flags that can

be cleared by writing 1 to them (writing 0 has no effect). See Section 22.4.7, “Interrupts,” for more details.

NOTE

A read clears BIT1ERR, BIT0ERR, ACKERR, CRCERR, FRMERR, and

STFERR, therefore these bits must not be read speculatively. For future

compatibility, the TLB entry covering the CANx_ESR must be configured

to be guarded.

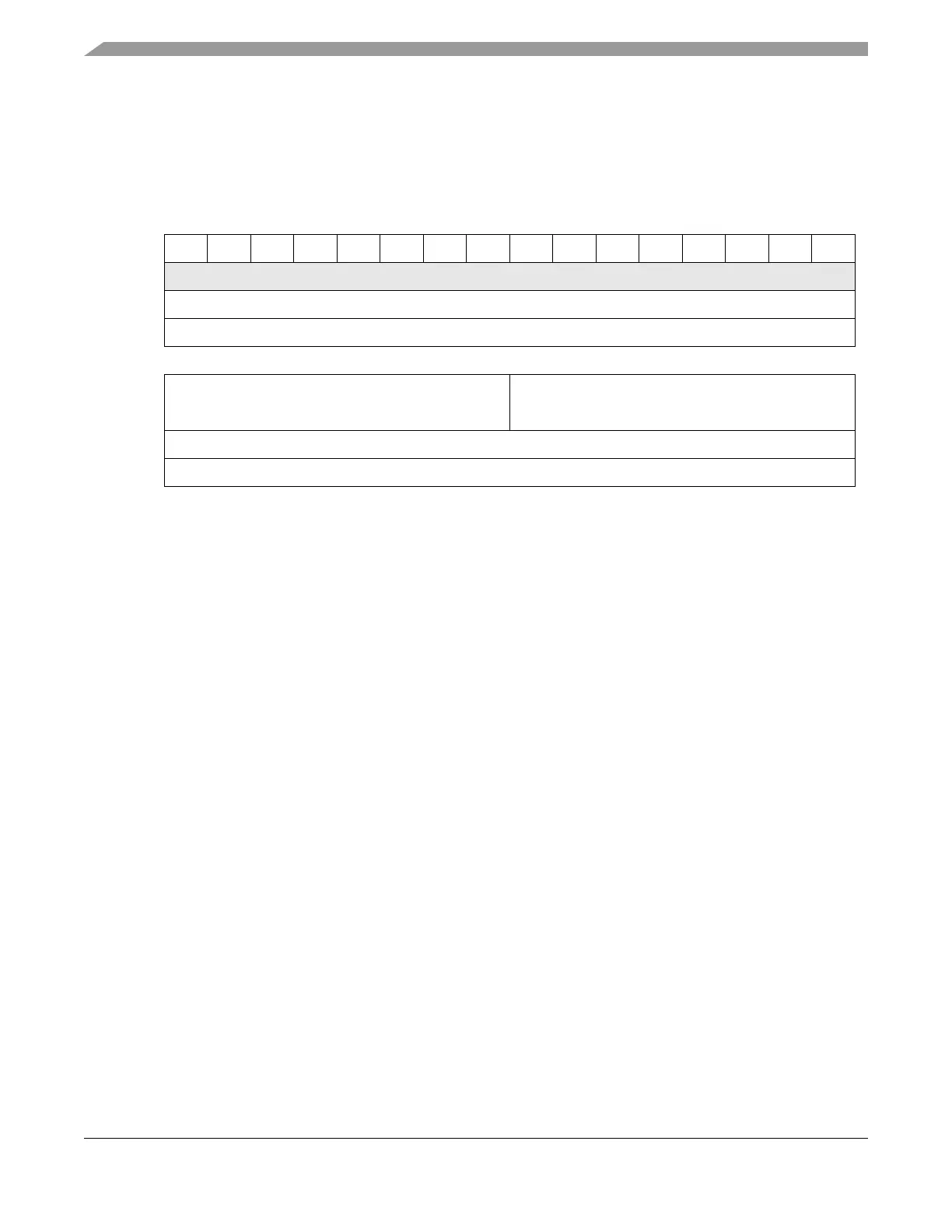

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R0000000000000000

W

Reset0000000000000000

Reg Addr Base + 0x001C

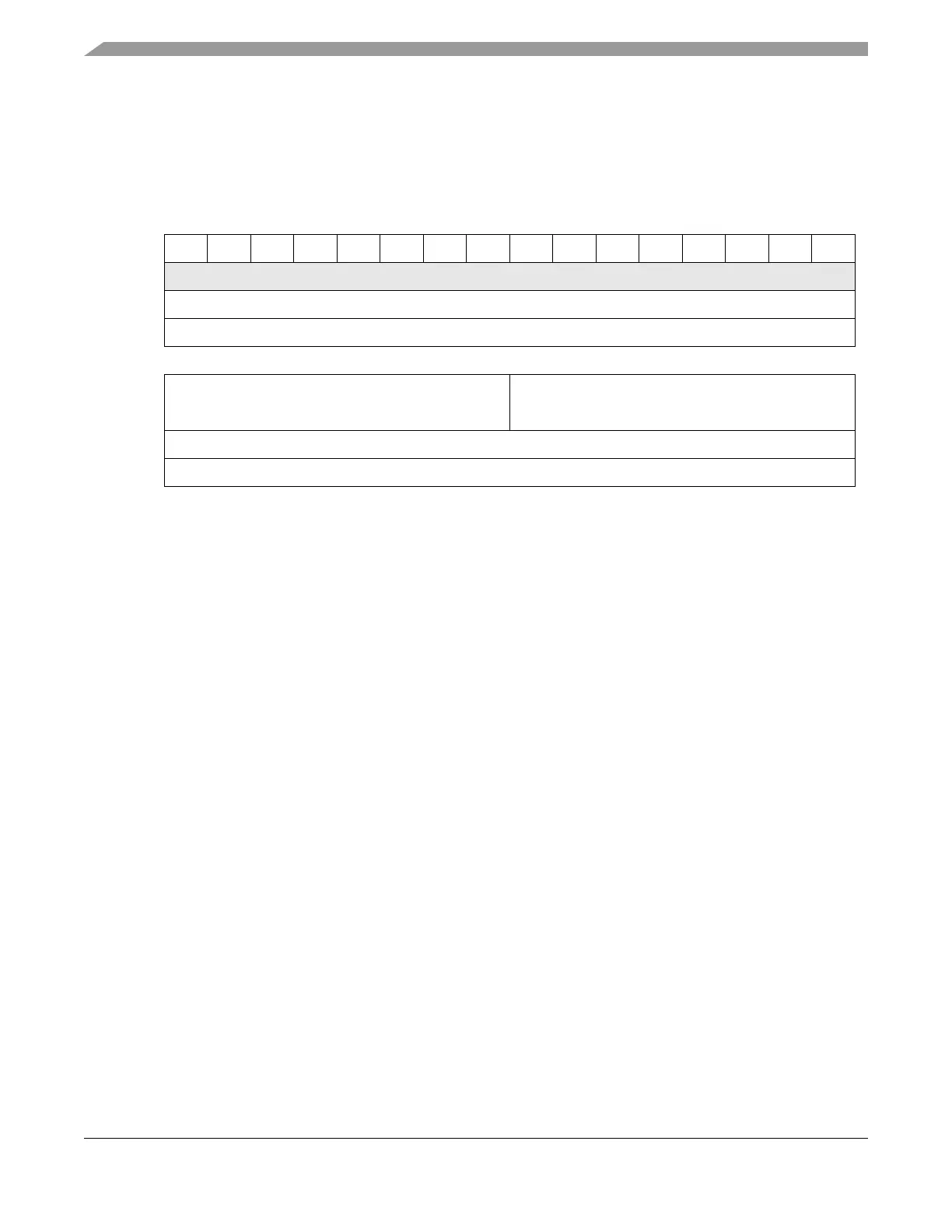

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R RXECTR TXECTR

W

Reset0000000000000000

Reg Addr Base + 0x001C

Figure 22-7. Error Counter Register (CANx_ECR)

Loading...

Loading...