MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 25-35

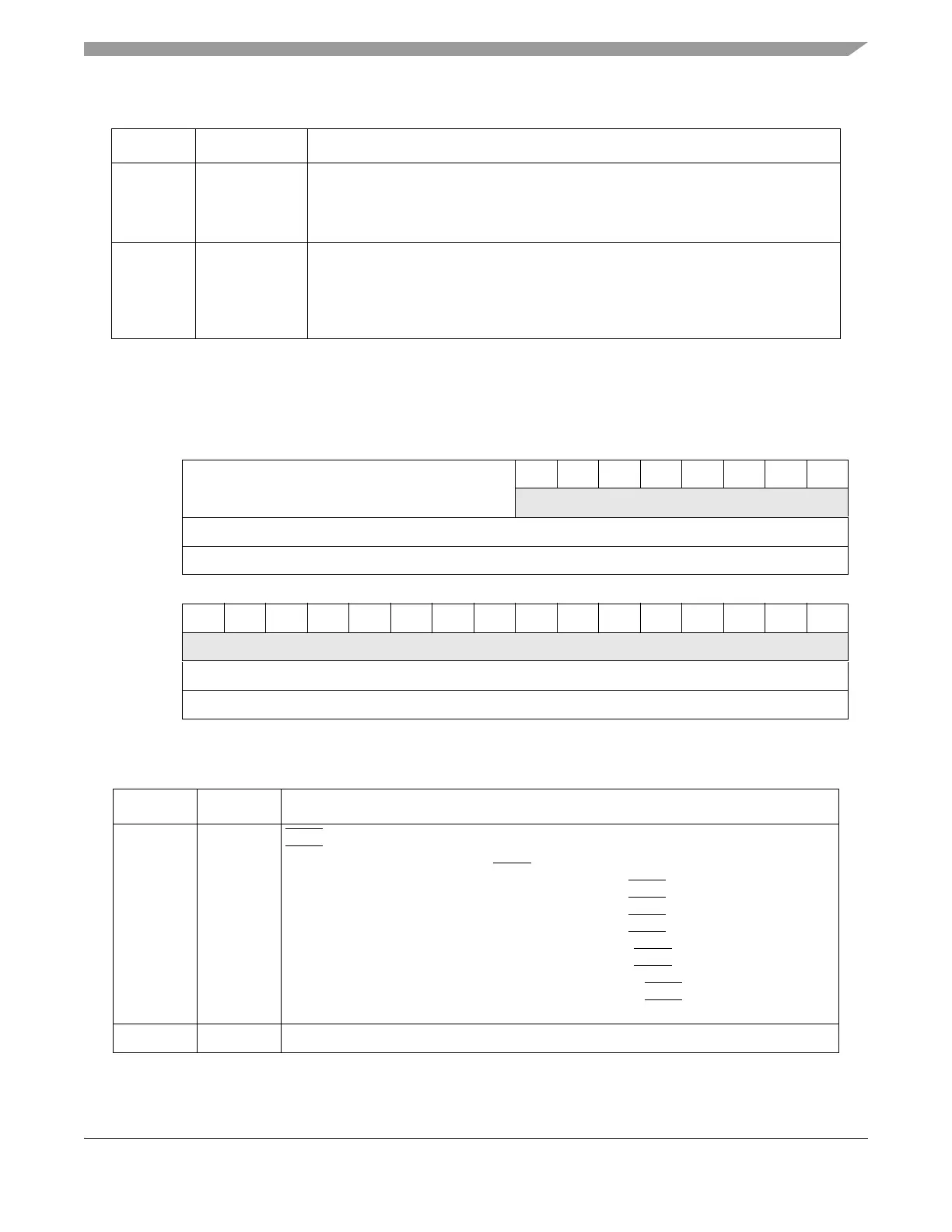

Development control register 2 is shown in Figure 25-14 and its fields are described in Table 25-26.

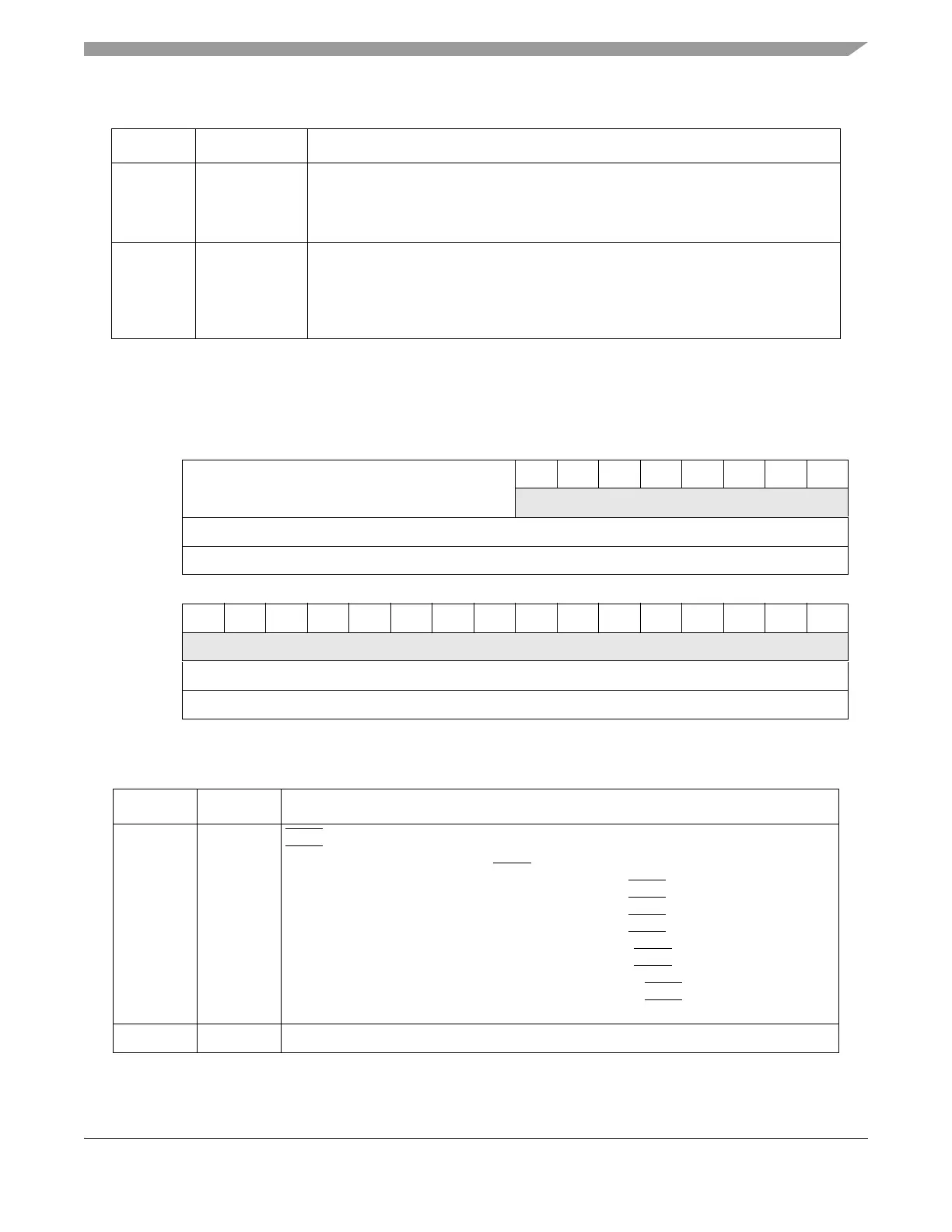

4–3 EIC

[1:0]

EVTI control.

00 EVTI is used for synchronization (program trace/ data trace)

01 EVTI is used for debug request

1X Reserved

2–0 TM

[2:0]

Trace mode. Any or all of the TM bits may set, enabling one or more traces.

000 No trace

1XX Program trace enabled

X1X Data trace enabled

XX1 Ownership trace enabled

1

The output port mode control bit (OPC) and MCKO divide bits (MCK_DIV) are shown for clarity. These functions are

controlled globally by the NPC port control register (PCR).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R EWC 00000000

W

Reset0000000000000000

Nexus Reg 0x3

1514131211109876543210

R0000000000000000

W

Reset0000000000000000

Nexus Reg 0x3

Figure 25-14. Development Control Register 2 (DC2)

Table 25-26. DC2 Field Descriptions

Bits Name Description

31–24 EWC

[7:0]

EVTO

watchpoint configuration. Any or all of the bits in EWC may be set to configure the

EVTO

watchpoint.

00000000No Watchpoints trigger EVTO

1XXXXXXXWatchpoint #0 (IAC1 from Nexus1) triggers EVTO

X1XXXXXXWatchpoint #1 (IAC2 from Nexus1) triggers EVTO

XX1XXXXXWatchpoint #2 (IAC3 from Nexus1) triggers EVTO

XXX1XXXXWatchpoint #3 (IAC4 from Nexus1) triggers EVTO

XXXX1XXXWatchpoint #4 (DAC1 from Nexus1) triggers EVTO

XXXXX1XXWatchpoint #5 (DAC2 from Nexus1) triggers EVTO

XXXXXX1XWatchpoint #6 (DCNT1 from Nexus1) triggers EVTO

XXXXXXX1Watchpoint #7 (DCNT2 from Nexus1) triggers EVTO

23–0 — Reserved.

Table 25-25. DC1 Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...