MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

25-50 Freescale Semiconductor

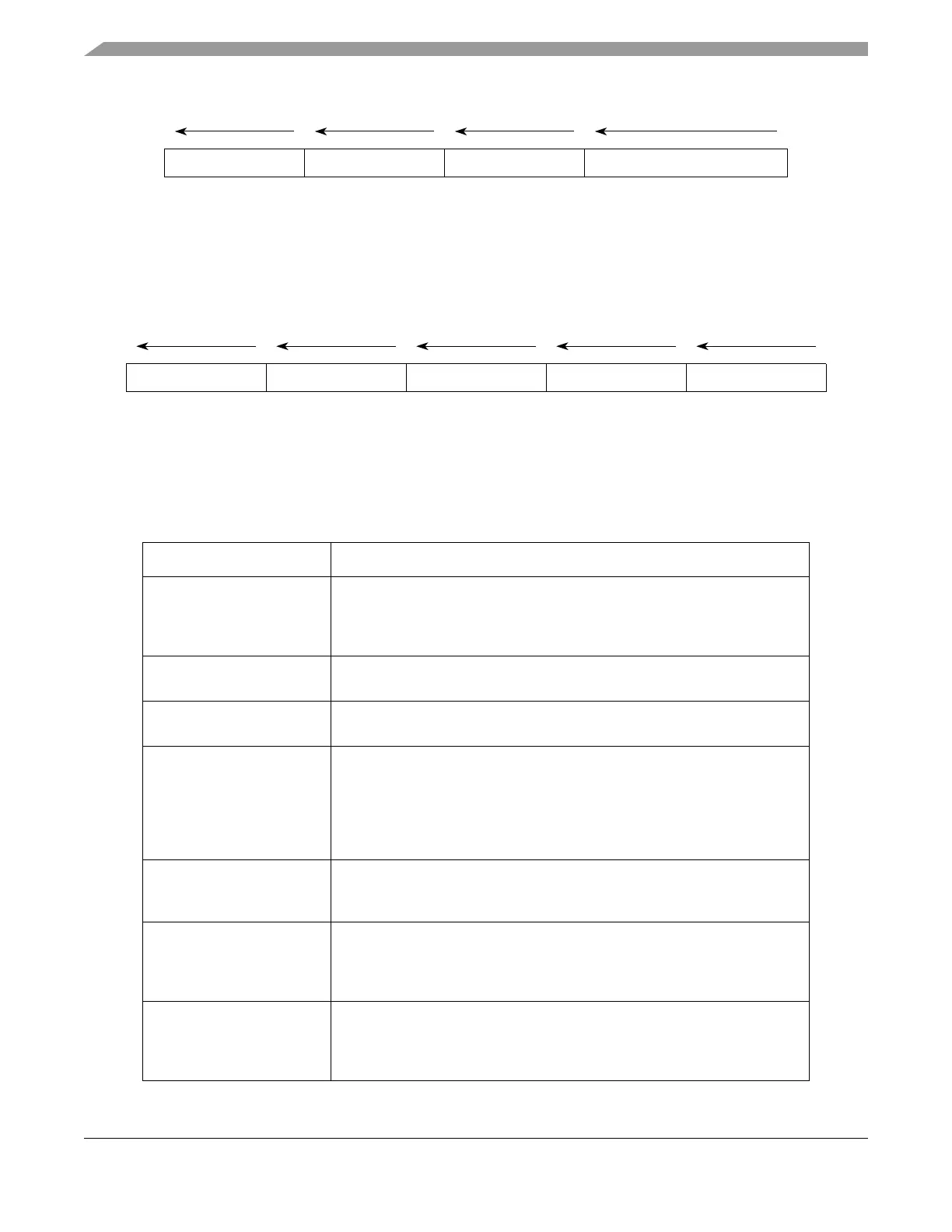

Figure 25-34. Direct/Indirect Branch with Sync Message Format

The formats for program trace direct/indirect branch with sync. messages and indirect branch history with

sync. messages are as follows

:

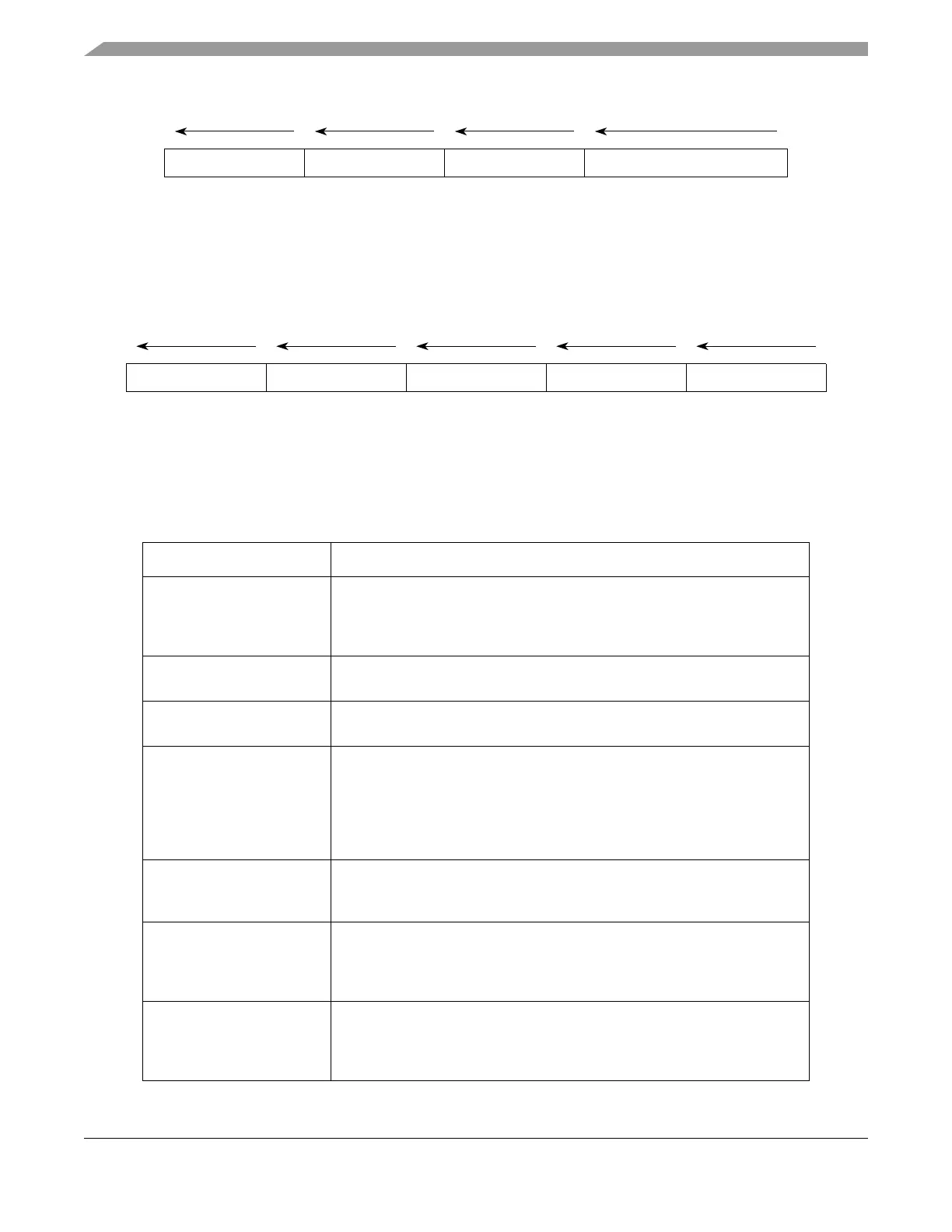

Figure 25-35. Indirect Branch History with Sync. Message Format

Exception conditions that result in program trace synchronization are summarized in Table 25-35.

Table 25-35. Program Trace Exception Summary

Exception Condition Exception Handling

System Reset Negation At the negation of JTAG reset (JCOMP), queue pointers, counters, state

machines, and registers within the NZ6C3 module are reset. Upon the first

branch out of system reset (if program trace is enabled), the first program

trace message is a direct/indirect branch with sync. message.

Program Trace Enabled The first program trace message (after program trace has been enabled) is a

synchronization message.

Exit from Low Power/Debug Upon exit from a low power mode or debug mode the next direct/indirect

branch will be converted to a direct/indirect branch with sync. message.

Queue Overrun An error message occurs when a new message cannot be queued due to the

message queue being full. The FIFO will discard messages until it has

completely emptied the queue. After it is emptied, an error message will be

queued. The error encoding will indicate which types of messages attempted

to be queued while the FIFO was being emptied. The next BTM message in

the queue will be a direct/indirect branch with sync. message.

Periodic Program Trace

Sync.

A forced synchronization occurs periodically after 255 program trace

messages have been queued. A direct/indirect branch with sync. message is

queued. The periodic program trace message counter then resets.

Event In If the Nexus module is enabled, an EVTI assertion initiates a direct/indirect

branch with sync. message upon the next direct/indirect branch (if program

trace is enabled and the EIC bits of the DC1 register have enabled this

feature).

Sequential Instruction Count

Overflow

When the sequential instruction counter reaches its maximum count (up to

255 sequential instructions may be executed), a forced synchronization

occurs. The sequential counter then resets. A program trace direct/indirect

branch with sync.message is queued upon execution of the next branch.

msb lsb

234

F-ADDR I-CNT SRC

4 bits

1

TCODE (001011 or 001100)

1-8 bits1-32 bits 6 bits

Max length = 50 bits; Min length = 12 bits

HIST

msb lsb

234

F-ADDR I-CNT SRC

5

4 bits

1

TCODE (011101)

1-8 bits1-32 bits1-32 bits 6 bits

Max length = 82 bits; Min length = 13 bits

Loading...

Loading...