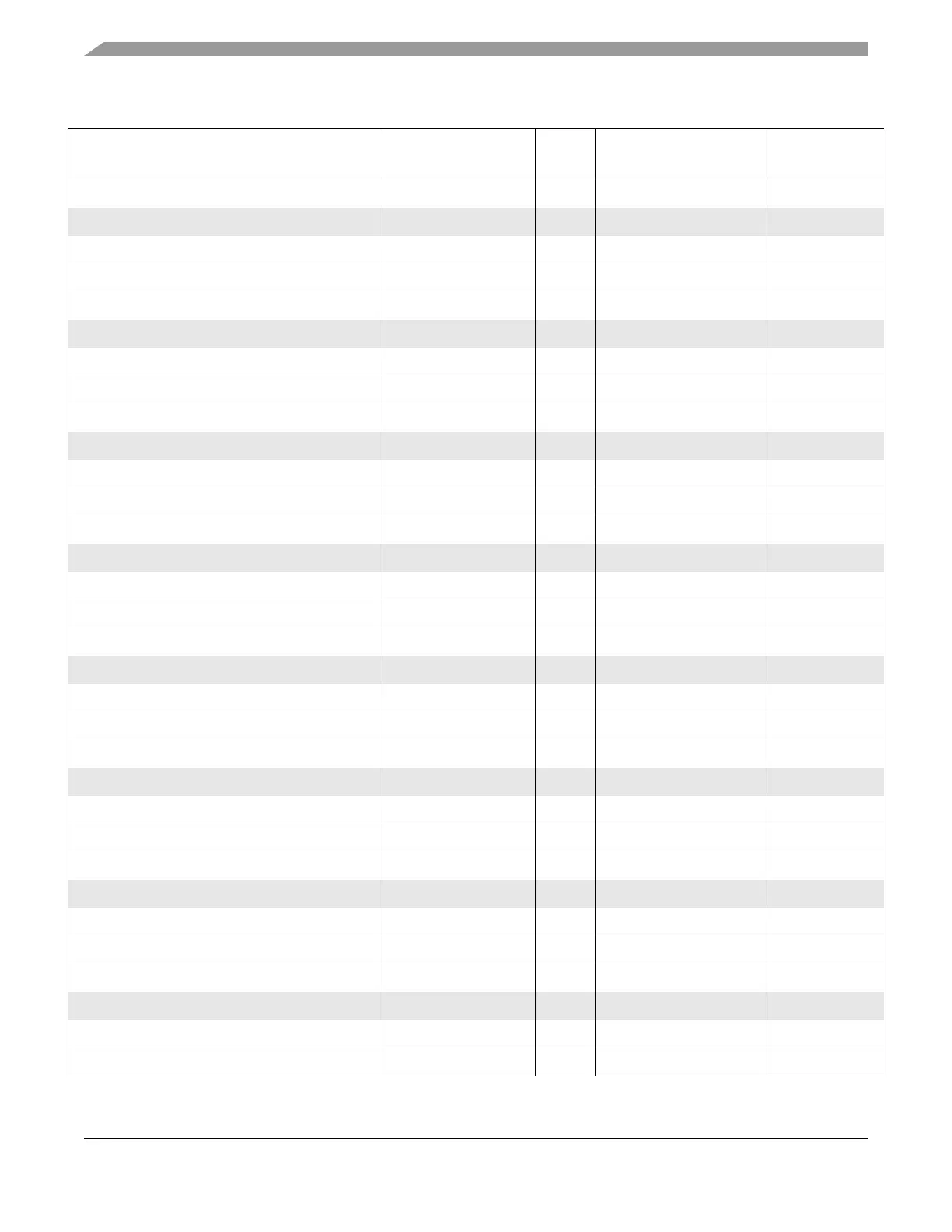

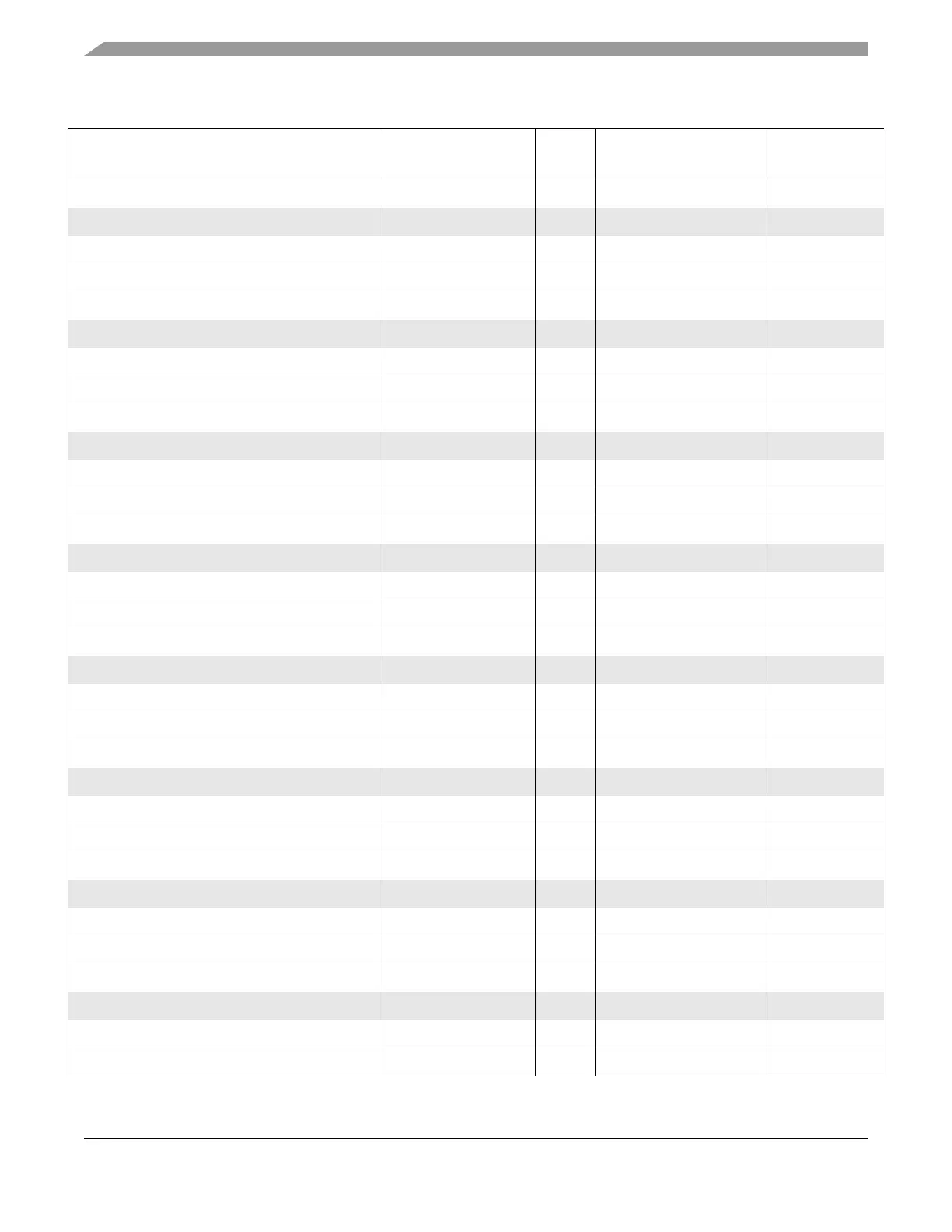

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

A-32 Freescale Semiconductor

eTPU B channel 4 host service request register

2

ETPU_C4HSRR_B

2

32-bit Base + 0x0848

Reserved — — Base + (0x084C-0x084F)

eTPU B channel 5 configuration register

2

ETPU_C5CR_B

2

32-bit Base + 0x0850

eTPU B channel 5 status and control register

2

ETPU_C5SCR_B

2

32-bit Base + 0x0854

eTPU B channel 5 host service request register

2

ETPU_C5HSRR_B

2

32-bit Base + 0x0858

Reserved — — Base + (0x085C-0x085F)

eTPU B channel 6 configuration register

2

ETPU_C6CR_B

2

32-bit Base + 0x0860

eTPU B channel 6 status and control register

2

ETPU_C6SCR_B

2

32-bit Base + 0x0864

eTPU B channel 6 host service request register

2

ETPU_C6HSRR_B

2

32-bit Base + 0x0868

Reserved — — Base + (0x086C-0x086F)

eTPU B channel 7 configuration register

2

ETPU_C7CR_B

2

32-bit Base + 0x0870

eTPU B channel 7 status and control register

2

ETPU_C7SCR_B

2

32-bit Base + 0x0874

eTPU B channel 7 host service request register

2

ETPU_C7HSRR_B

2

32-bit Base + 0x0878

Reserved — — Base + (0x087C-0x087F)

eTPU B channel 8 configuration register

2

ETPU_C8CR_B

2

32-bit Base + 0x0880

eTPU B channel 8 status and control register

2

ETPU_C8SCR_B

2

32-bit Base + 0x0884

eTPU B channel 8 host service request register

2

ETPU_C8HSRR_B

2

32-bit Base + 0x0888

Reserved — — Base + (0x088C-0088F)

eTPU B channel 9 configuration register

2

ETPU_C9CR_B

2

32-bit Base + 0x0890

eTPU B channel 9 status and control register

2

ETPU_C9SCR_B

2

32-bit Base + 0x0894

eTPU B channel 9 host service request register

2

ETPU_C9HSRR_B

2

32-bit Base + 0x0898

Reserved — — Base + (0x081C-0x081F)

eTPU B channel 10 configuration register

2

ETPU_C10CR_B

2

32-bit Base + 0x08A0

eTPU B channel 10 status and control register

2

ETPU_C10SCR_B

2

32-bit Base + 0x08A4

eTPU B channel 10 host service request register

2

ETPU_C10HSRR_B

2

32-bit Base + 0x08A8

Reserved — — Base + (0x08AC-0x08AF)

eTPU B channel 11 configuration register

2

ETPU_C11CR_B

2

32-bit Base + 0x08B0

eTPU B channel 11 status and control register

2

ETPU_C11SCR_B

2

32-bit Base + 0x08B4

eTPU B channel 11 host service request register

2

ETPU_C11HSRR_B

2

32-bit Base + 0x08B8

Reserved — — Base + (0x08BC-0x08BF)

eTPU B channel 12 configuration register

2

ETPU_C12CR_B

2

32-bit Base + 0x08C0

eTPU B channel 12 status and control register

2

ETPU_C12SCR_B

2

32-bit Base + 0x08C4

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...