MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor A-33

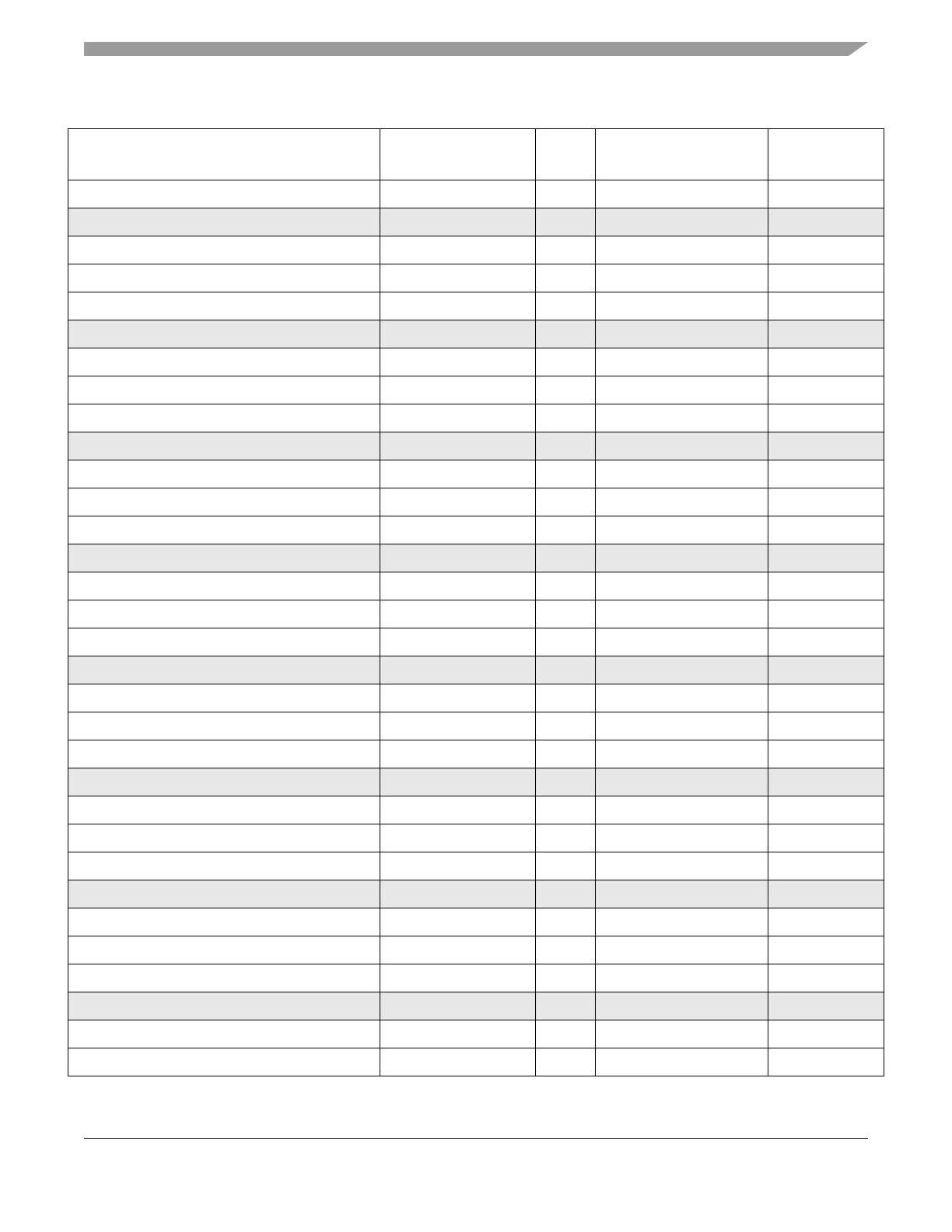

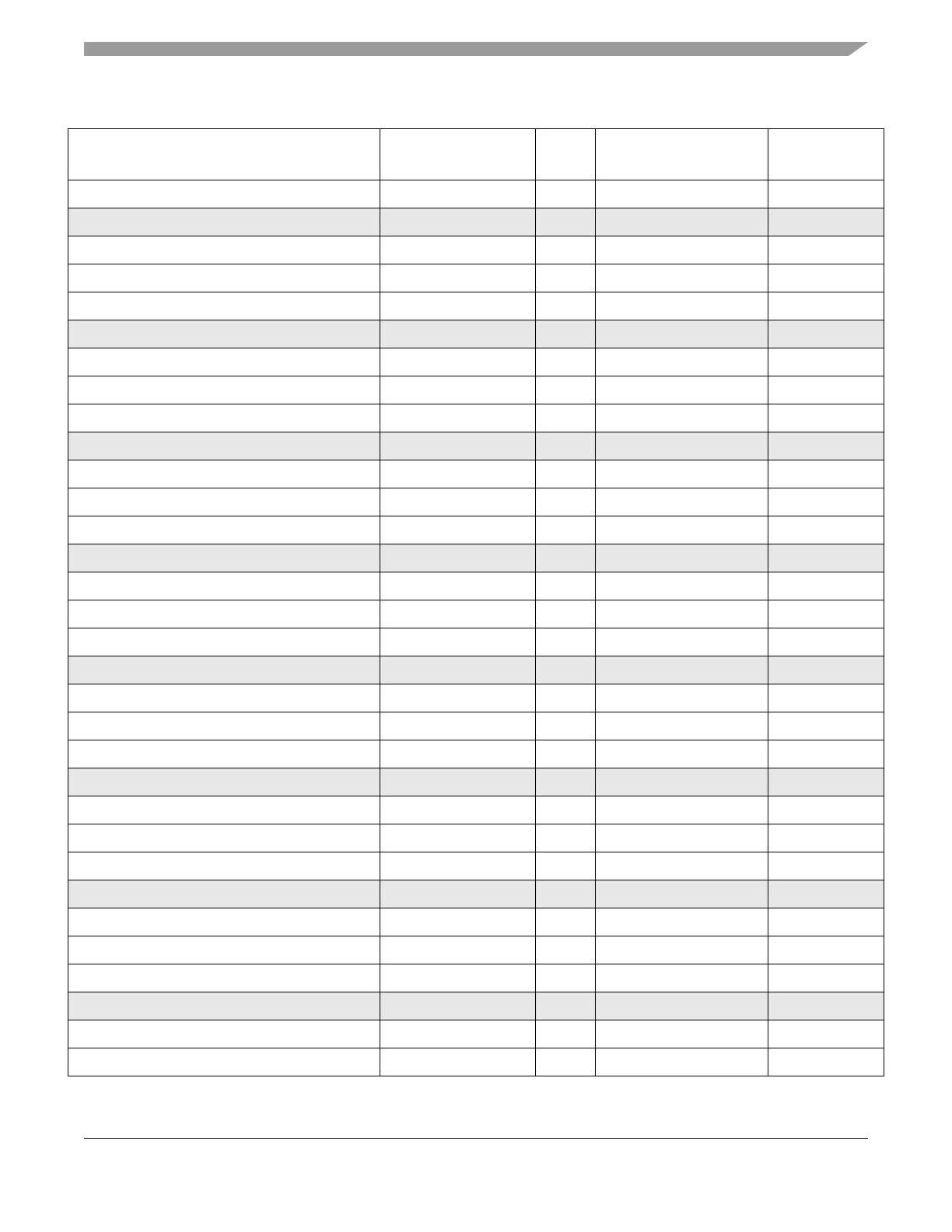

eTPU B channel 12 host service request register

2

ETPU_C12HSRR_B

2

32-bit Base + 0x08C8

Reserved — — Base + (0x08CC-0x08CF)

eTPU B channel 13 configuration register

2

ETPU_C13CR_B

2

32-bit Base + 0x08D0

eTPU B channel 13 status and control register

2

ETPU_C13SCR_B

2

32-bit Base + 0x08D4

eTPU B channel 13 host service request register

2

ETPU_C13HSRR_B

2

32-bit Base + 0x08D8

Reserved — — Base + (0x08DC-0x08DF)

eTPU B channel 14 configuration register

2

ETPU_C14CR_B

2

32-bit Base + 0x08E0

eTPU B channel 14 status and control register

2

ETPU_C14SCR_B

2

32-bit Base + 0x08E4

eTPU B channel 14 host service request register

2

ETPU_C14HSRR_B

2

32-bit Base + 0x08E8

Reserved — — Base + (0x08EC-0x08EF)

eTPU B channel 15 configuration register

2

ETPU_C15CR_B

2

32-bit Base + 0x08F0

eTPU B channel 15 status and control register

2

ETPU_C15SCR_B

2

32-bit Base + 0x08F4

eTPU B channel 15 host service request register

2

ETPU_C15HSRR_B

2

32-bit Base + 0x08F8

Reserved — — Base + (0x08FC-0x08FF)

eTPU B channel 16 configuration register

2

ETPU_C16CR_B

2

32-bit Base + 0x0900

eTPU B channel 16 status and control register

2

ETPU_C16SCR_B

2

32-bit Base + 0x0904

eTPU B channel 16 host service request register

2

ETPU_C16HSRR_B

2

32-bit Base + 0x0908

Reserved — — Base + (0x090C-0x090F)

eTPU B channel 17 configuration register

2

ETPU_C17CR_B

2

32-bit Base + 0x0910

eTPU B channel 17 status and control register

2

ETPU_C17SCR_B

2

32-bit Base + 0x0914

eTPU B channel 17 host service request register

2

ETPU_C17HSRR_B

2

32-bit Base + 0x0918

Reserved — — Base + (0x091C-0x091F)

eTPU B channel 18 configuration register

2

ETPU_C18CR_B

2

32-bit Base + 0x0920

eTPU B channel 18 status and control register

2

ETPU_C18SCR_B

2

32-bit Base + 0x0924

eTPU B channel 18 host service request register

2

ETPU_C18HSRR_B

2

32-bit Base + 0x0928

Reserved — — Base + (0x092C-0x092F)

eTPU B channel 19 configuration register

2

ETPU_C19CR_B

2

32-bit Base + 0x0930

eTPU B channel 19 status and control register

2

ETPU_C19SCR_B

2

32-bit Base + 0x0934

eTPU B channel 19 host service request register

2

ETPU_C19HSRR_B

2

32-bit Base + 0x0938

Reserved — — Base + (0x093C-0x093F)

eTPU B channel 20 configuration register

2

ETPU_C20CR_B

2

32-bit Base + 0x0940

eTPU B channel 20 status and control register

2

ETPU_C20SCR_B

2

32-bit Base + 0x0944

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...