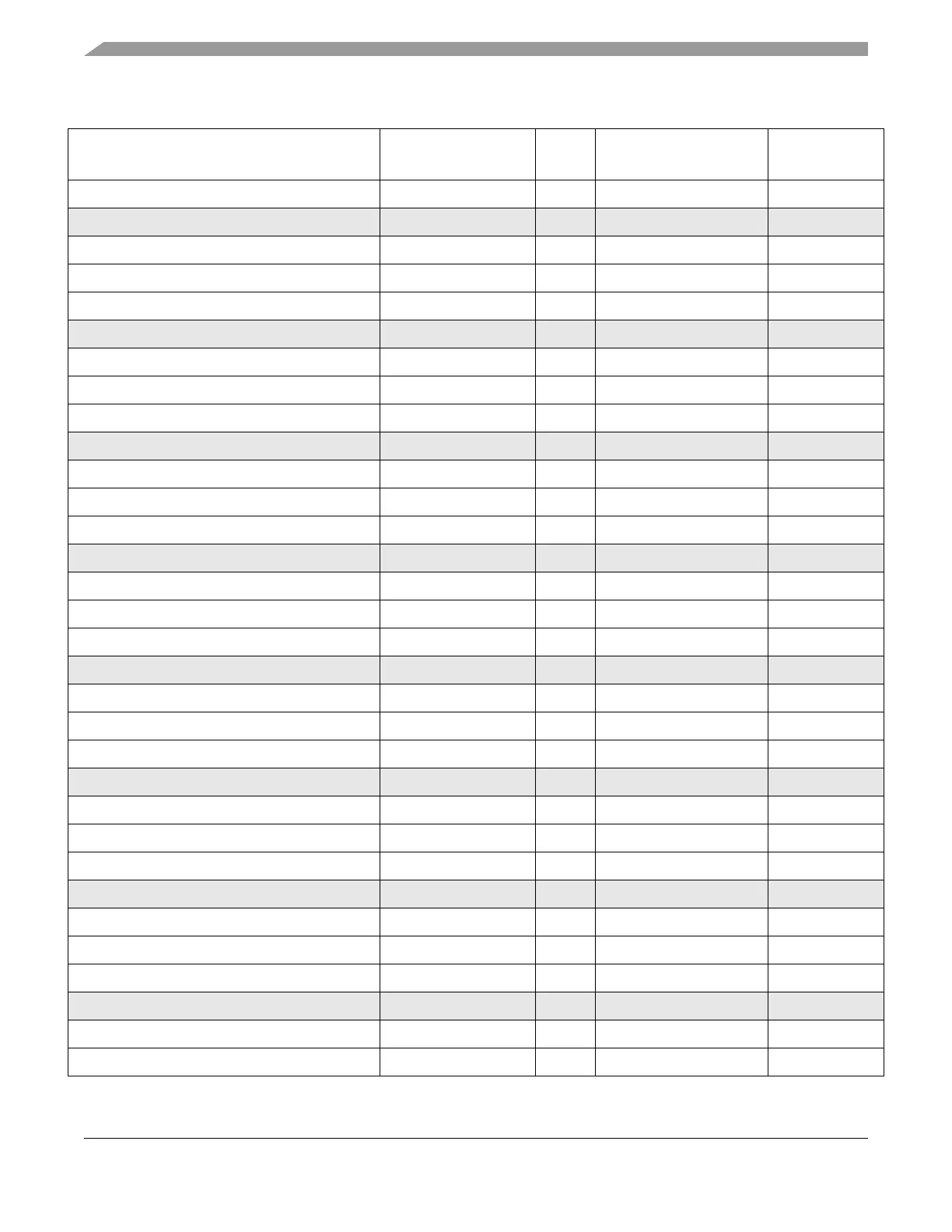

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

A-34 Freescale Semiconductor

eTPU B channel 20 host service request register

2

ETPU_C20HSRR_B

2

32-bit Base + 0x0948

Reserved — — Base + (0x094C-0x094F)

eTPU B channel 21 configuration register

2

ETPU_C21CR_B

2

32-bit Base + 0x0950

eTPU B channel 21 status and control register

2

ETPU_C21SCR_B

2

32-bit Base + 0x0954

eTPU B channel 21 host service request register

2

ETPU_C21HSRR_B

2

32-bit Base + 0x0958

Reserved — — Base + (0x095C-0x095F)

eTPU B channel 22 configuration register

2

ETPU_C22CR_B

2

32-bit Base + 0x0960

eTPU B channel 22 status and control register

2

ETPU_C22SCR_B

2

32-bit Base + 0x0964

eTPU B channel 22 host service request register

2

ETPU_C22HSRR_B

2

32-bit Base + 0x0968

Reserved — — Base + (0x096C-0x096F)

eTPU B channel 23 configuration register

2

ETPU_C23CR_B

2

32-bit Base + 0x0970

eTPU B channel 23 status and control register

2

ETPU_C23SCR_B

2

32-bit Base + 0x0974

eTPU B channel 23 host service request register

2

ETPU_C23HSRR_B

2

32-bit Base + 0x0978

Reserved — — Base + (0x097C-0x097F)

eTPU B channel 24 configuration register

2

ETPU_C24CR_B

2

32-bit Base + 0x0980

eTPU B channel 24 status and control register

2

ETPU_C24SCR_B

2

32-bit Base + 0x0984

eTPU B channel 24 host service request register

2

ETPU_C24HSRR_B

2

32-bit Base + 0x0988

Reserved — — Base + (0x098C-0x098F)

eTPU B channel 25 configuration register

2

ETPU_C25CR_B

2

32-bit Base + 0x0990

eTPU B channel 25 status and control register

2

ETPU_C25SCR_B

2

32-bit Base + 0x0994

eTPU B channel 25 host service request register

2

ETPU_C25HSRR_B

2

32-bit Base + 0x0998

Reserved — — Base + (0x099C-0x099F)

eTPU B channel 26 configuration register

2

ETPU_C26CR_B

2

32-bit Base + 0x09A0

eTPU B channel 26 status and control register

2

ETPU_C26SCR_B

2

32-bit Base + 0x09A4

eTPU B channel 26 host service request register

2

ETPU_C26HSRR_B

2

32-bit Base + 0x09A8

Reserved — — Base + (0x09AC-0x09AF)

eTPU B channel 27 configuration register

2

ETPU_C27CR_B

2

32-bit Base + 0x09B0

eTPU B channel 27 status and control register

2

ETPU_C27SCR_B

2

32-bit Base + 0x09B4

eTPU B channel 27 host service request register

2

ETPU_C27HSRR_B

2

32-bit Base + 0x09B8

Reserved — — Base + (0x09BC-0x09BF)

eTPU B channel 28 configuration register

2

ETPU_C28CR_B

2

32-bit Base + 0x09C0

eTPU B channel 28 status and control register

2

ETPU_C28SCR_B

2

32-bit Base + 0x09C4

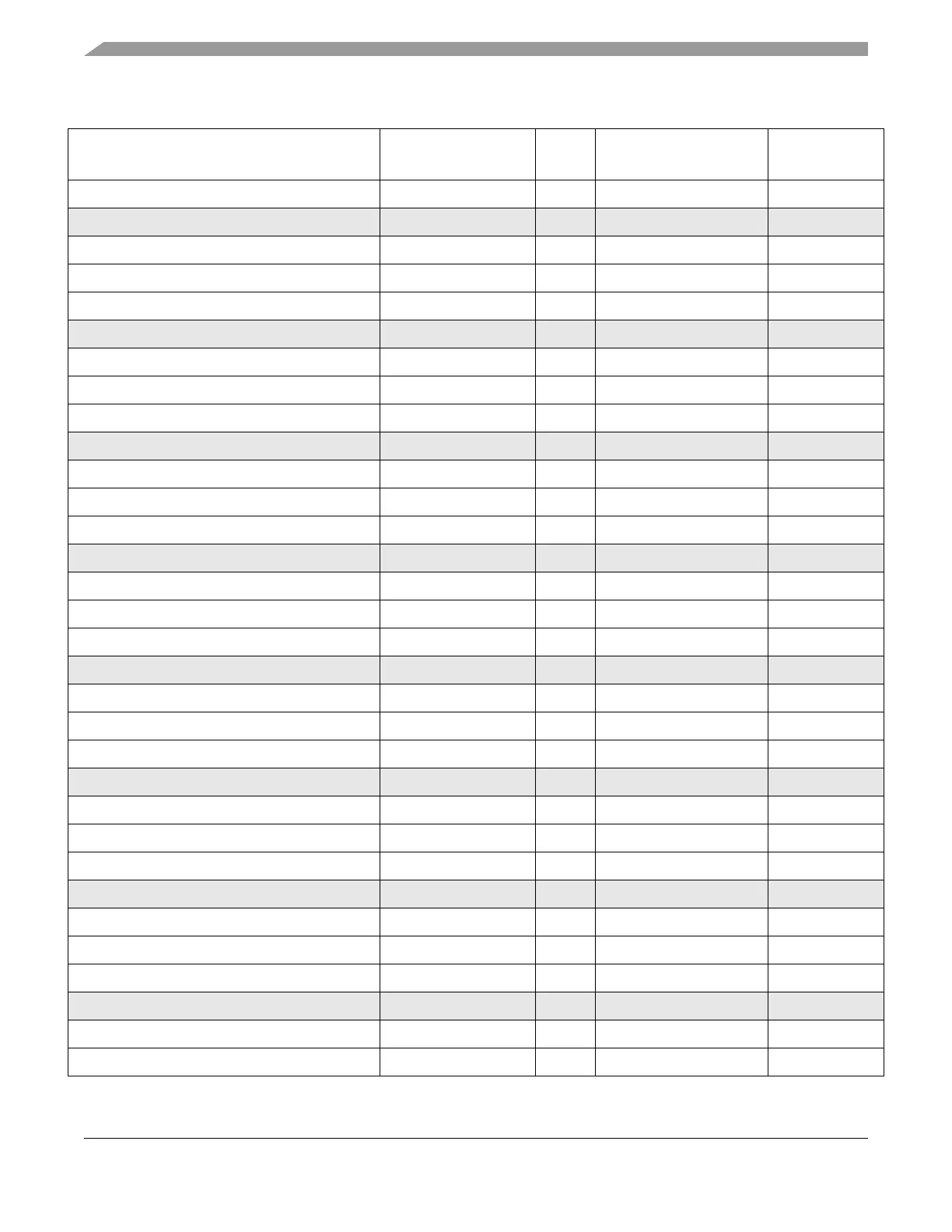

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...