MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor A-35

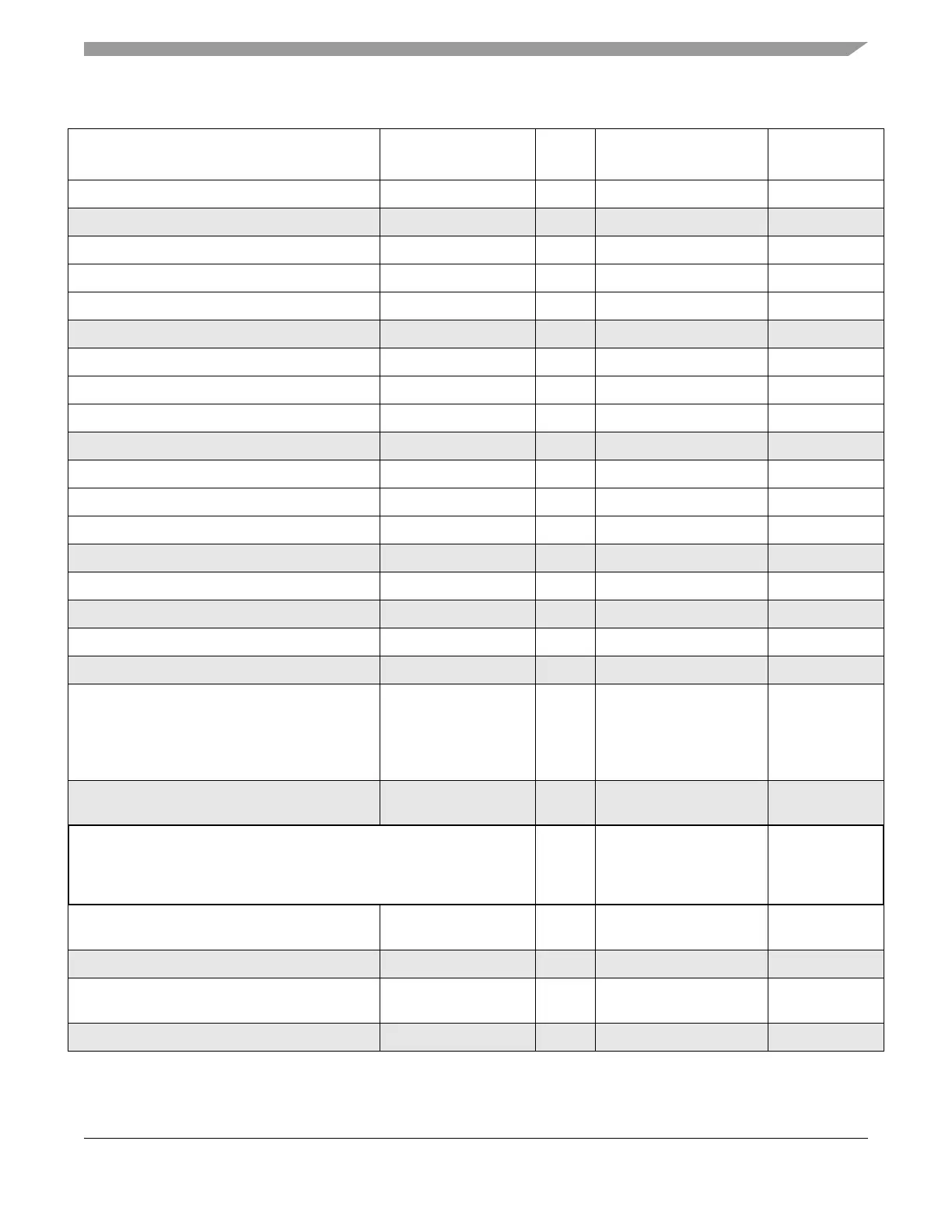

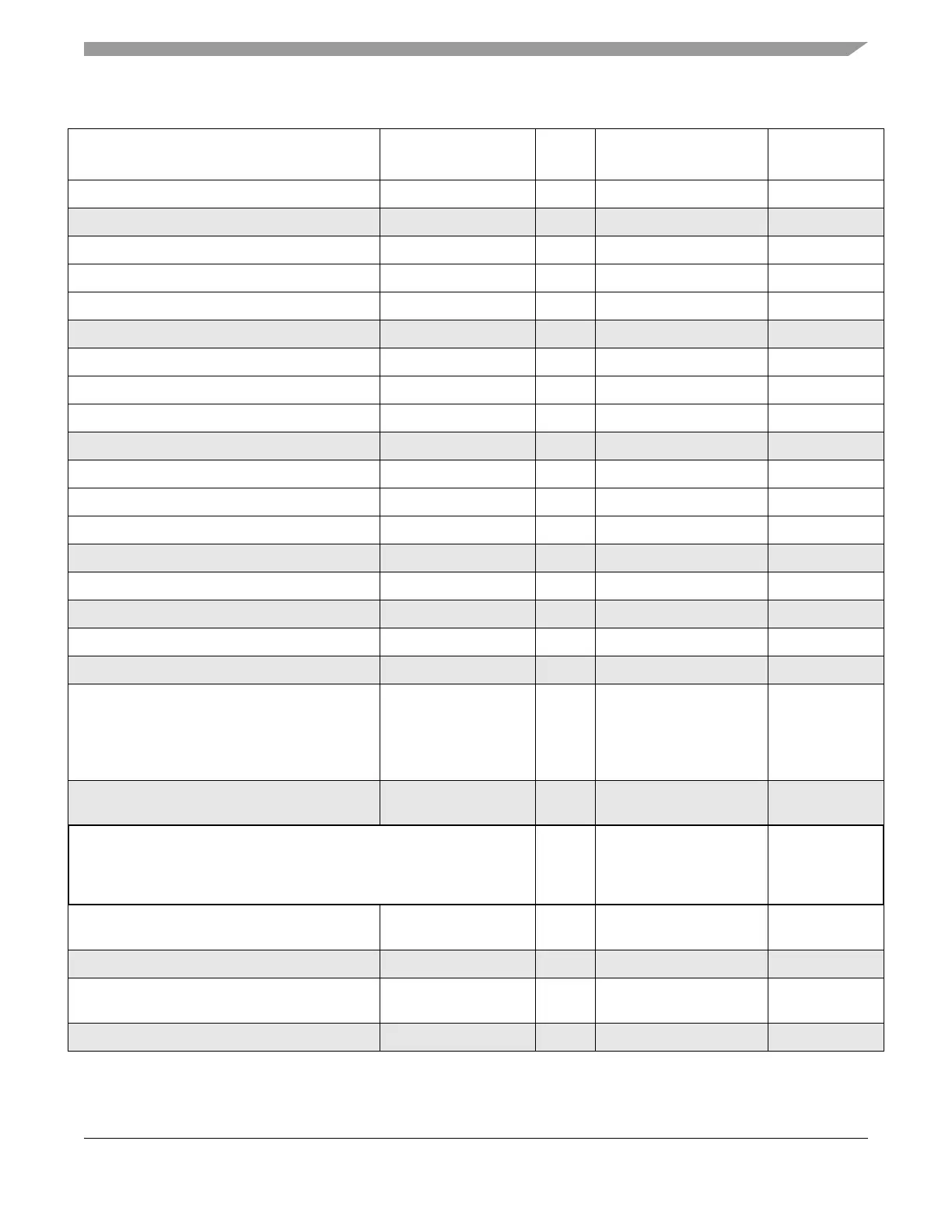

eTPU B channel 28 host service request register

2

ETPU_C28HSRR_B

2

32-bit Base + 0x09C8

Reserved — — Base + (0x09CC-0x09CF)

eTPU B channel 29 configuration register

2

ETPU_C29CR_B

2

32-bit Base + 0x09D0

eTPU B channel 29 status and control register

2

ETPU_C29SCR_B

2

32-bit Base + 0x09D4

eTPU B channel 29 host service request register

2

ETPU_C29HSRR_B

2

32-bit Base + 0x09D8

Reserved — — Base + (0x09DC-0x09DF)

eTPU B channel 30 configuration register

2

ETPU_C30CR_B

2

32-bit Base + 0x09E0

eTPU B channel 30 status and control register

2

ETPU_C30SCR_B

2

32-bit Base + 0x09E4

eTPU B channel 30 host service request register

2

ETPU_C30HSRR_B

2

32-bit Base + 0x09E8

Reserved — — Base + (0x09EC-0x09EF)

eTPU B channel 31 configuration register

2

ETPU_C31CR_B

2

32-bit Base + 0x09F0

eTPU B channel 31 status and control register

2

ETPU_C31SCR_B

2

32-bit Base + 0x09F4

eTPU B channel 31 host service request register

2

ETPU_C31HSRR_B

2

32-bit Base + 0x09F8

Reserved — — Base + (0x09FC-0x7FFF)

Shared data memory (parameter RAM) SDM 3Kbyte Base + (0x8000-0x8BFF)

Reserved — — Base + (0x8C00-0xBFFF)

SDM PSE mirror Base + (0xC000-0xCBFF)

Reserved — — Base + (0xCC00-0xFFFF)

Shared code memory SCM 16 Kbyte

(5554)

12Kbyte

(5553)

Base

+ (0x1_0000-1_3FFF)

(MPC5554)

+ (0x1_0000-1_2FFF)

(MPC5553)

Reserved — — Base + (0x1_4000-

FFEF_FFFF)

Peripheral Bridge B (PBRIDGE_B)

0xFFF0_0000 Chapter 5,

“Peripheral Bridge

(PBRIDGE_A,

PBRIDGE_B)”

Peripheral bridge B master privilege control

register

PBRIDGE_B_MPCR 32-bit Base + 0x0000

Reserved — — Base + (0x0004-0x001F)

Peripheral bridge B peripheral access control

register 0

PBRIDGE_B_PACR0 32-bit Base + 0x0020

Reserved — — Base + (0x0024-0x0027)

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...