MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

A-36 Freescale Semiconductor

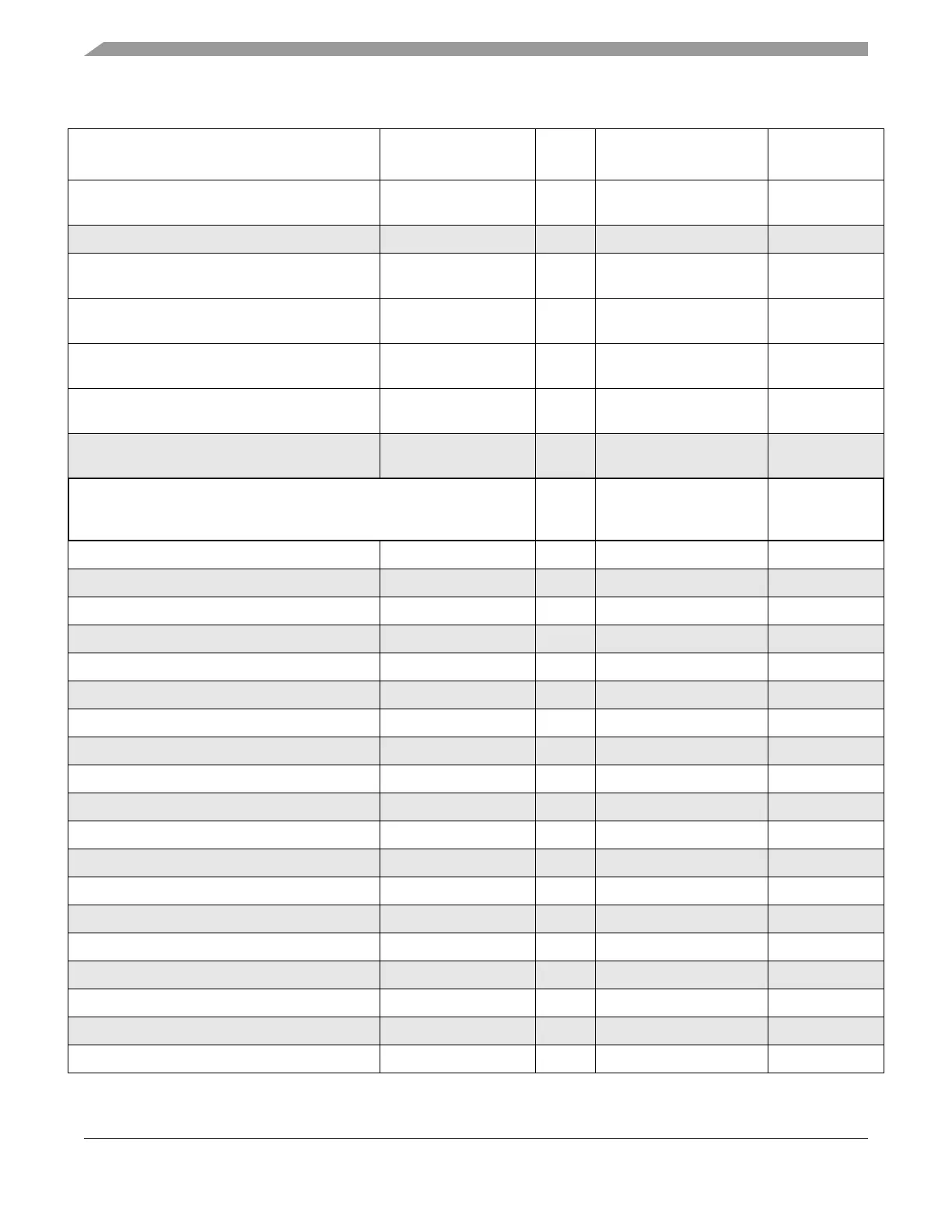

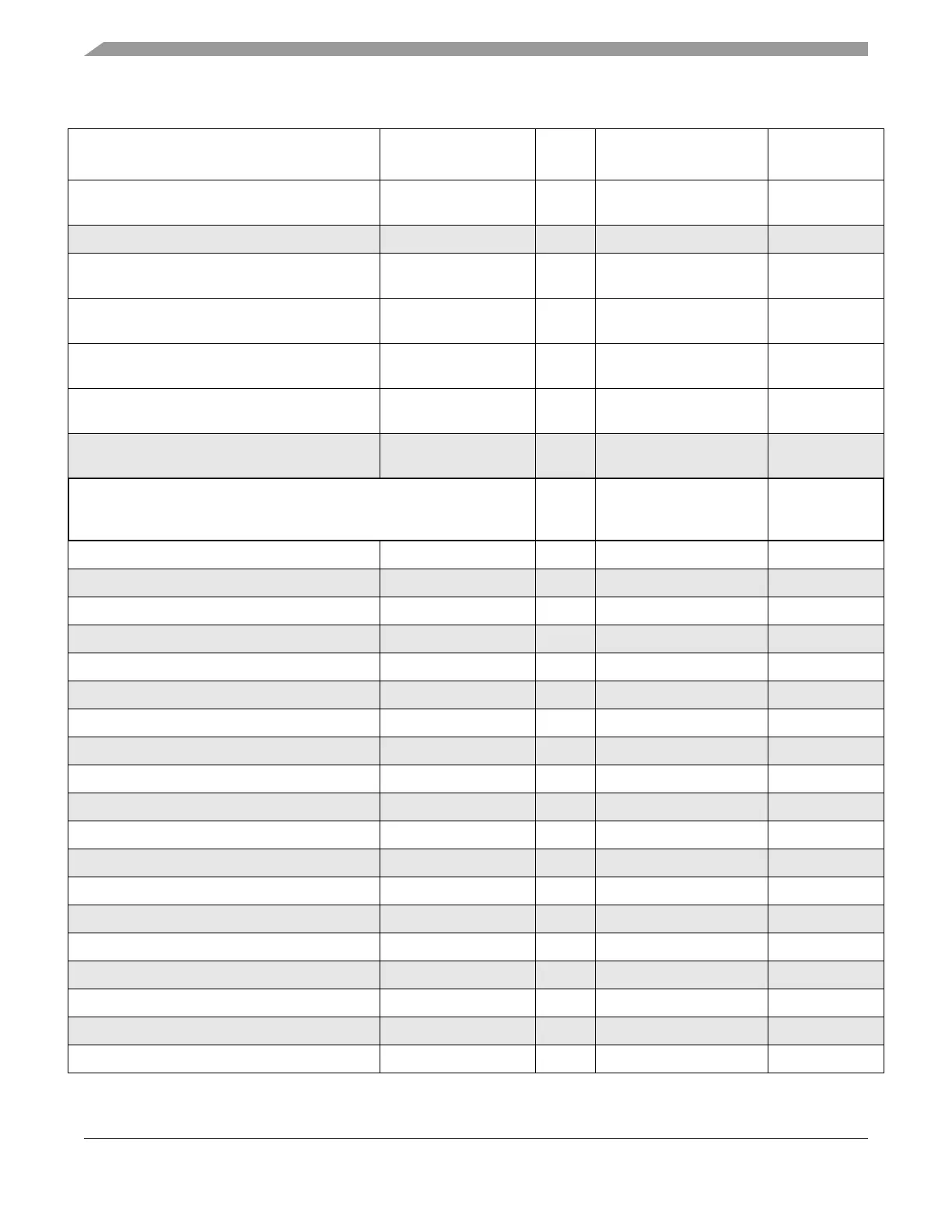

Peripheral bridge B peripheral access control

register 2

PBRIDGE_B_PACR2 32-bit Base + 0x0028

Reserved — — Base + (0x002C-0x003F)

Peripheral bridge B off-platform peripheral access

control register 0

PBRIDGE_B_OPACR0 32-bit Base + 0x0040

Peripheral bridge B off-platform peripheral access

control register 1

PBRIDGE_B_OPACR1 32-bit Base + 0x0044

Peripheral bridge B off-platform peripheral access

control register 2

PBRIDGE_B_OPACR2 32-bit Base + 0x0048

Peripheral bridge B off-platform peripheral access

control register 3

PBRIDGE_B_OPACR3 32-bit Base + 0x004C

Reserved — — (Base + 0x0050)-

0xFFF0_3FFF)

System Bus Crossbar Switch (XBAR)

0xFFF0_4000 Chapter 7,

“Crossbar Switch

(XBAR)”

Master priority register 0 XBAR_MPR0 32-bit Base + 0x0000

Reserved — — Base + (0x0004-0x000F)

Slave general purpose control register 0 XBAR_SGPCR0 32-bit Base + 0x0010

Reserved — — Base + (0x0014-0x00FF)

Master priority register 1 XBAR_MPR1 32-bit Base + 0x0100

Reserved — — Base + (0x0104-0x010F)

Slave general purpose control register 1 XBAR_SGPCR1 32-bit Base + 0x0110

Reserved — — Base + (0x0114-0x02FF)

Master priority register 3 XBAR_MPR3 32-bit Base + 0x0300

Reserved — — Base + (0x0304-0x030F)

Slave general purpose control register 3 XBAR_SGPCR3 32-bit Base + 0x0310

Reserved — — Base + (0x0314-0x05FF)

Master priority register 6 XBAR_MPR6 32-bit Base + 0x0600

Reserved — — Base + (0x0604-0x060F)

Slave general purpose control register 6 XBAR_SGPCR6 32-bit Base + 0x0610

Reserved — — Base + (0x0614-0x06FF)

Master priority register 7 XBAR_MPR7 32-bit Base + 0x0700

Reserved — — Base + (0x0704-0x070F)

Slave general purpose control register 7 XBAR_SGPCR7 32-bit Base + 0x0710

Table A-2. MPC5554 / MPC5553 Detailed Register Map (Continued)

Register Description Register Name

Used

Size

Address Reference

Loading...

Loading...