MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

3-18 Freescale Semiconductor

The MAS3 register is shown in Figure 3-10.

MAS3 fields are defined in Table 3-6

27 W Write-through required

0 This page is considered write-back with respect to the caches in the system.

1 All stores performed to this page are written through to main memory.

28 I Cache inhibited

0 This page is considered cacheable.

1 This page is considered cache-inhibited.

29 M Memory coherence required.The e200z6 does not

support the memory coherence required attribute,

and thus it is ignored.

0 Memory coherence is not required.

1 Memory coherence is required.

30 G Guarded. The e200z6ignores the guarded attribute (other than for generation of the p_hprot[4:2]

attributes on an external access), because no speculative or out-of-order processing is performed.

0 Access to this page are not guarded, and can be performed before it is known if they are required

by the sequential execution model.

1 All loads and stores to this page are performed without speculation (that is, they are known to be

required).

31 E Endianness. Determines endianness for the corresponding page.

0 The page is accessed in big-endian byte order.

1 The page is accessed in true little-endian byte order.

Permission bits

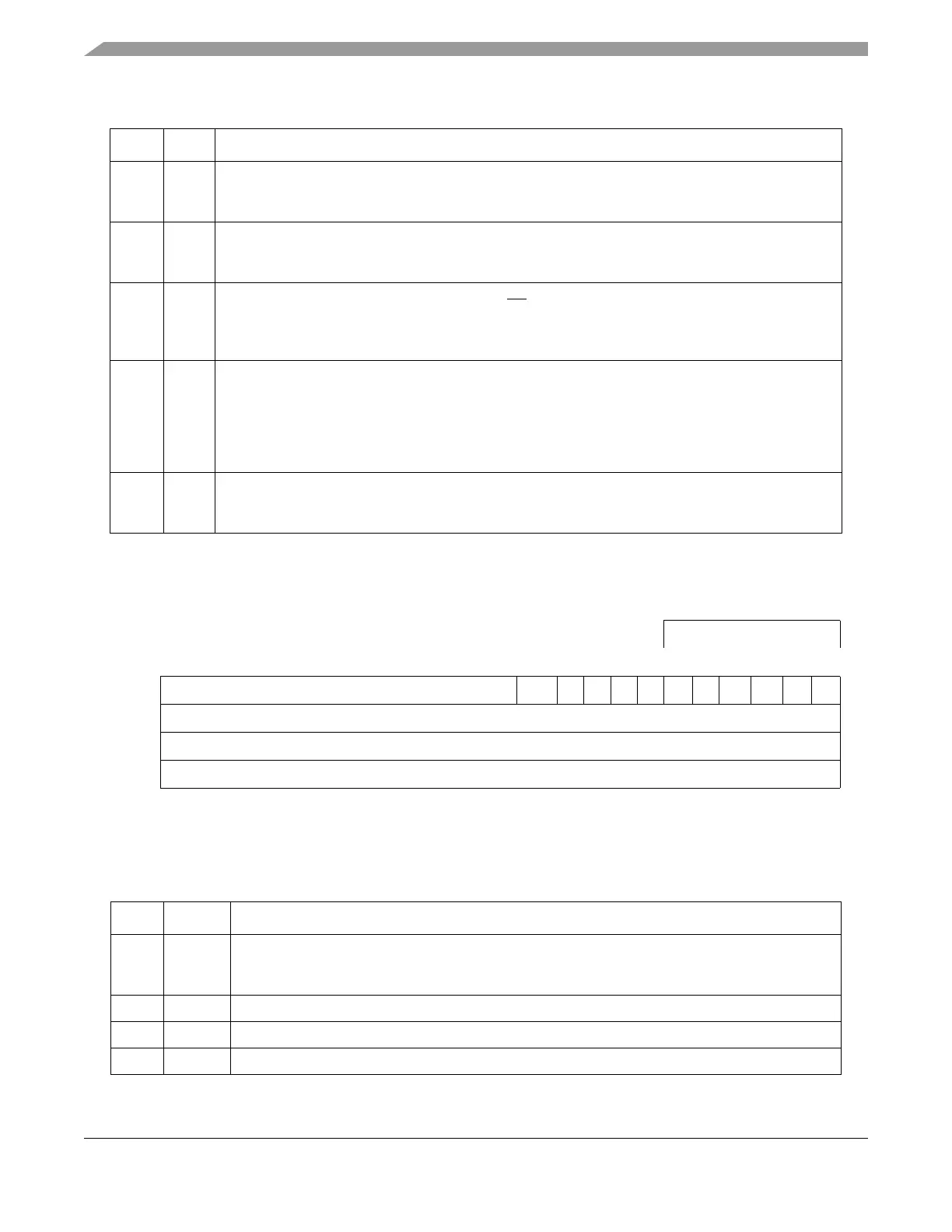

0 192021222324252627 28 29 3031

Field RPN — U0U1U2U3UXSXUWSWURSR

Reset Undefined on Power Up Unchanged on Reset

R/W R/W

SPR SPR 627

Figure 3-10. MMU Assist Register 3 (MAS3)

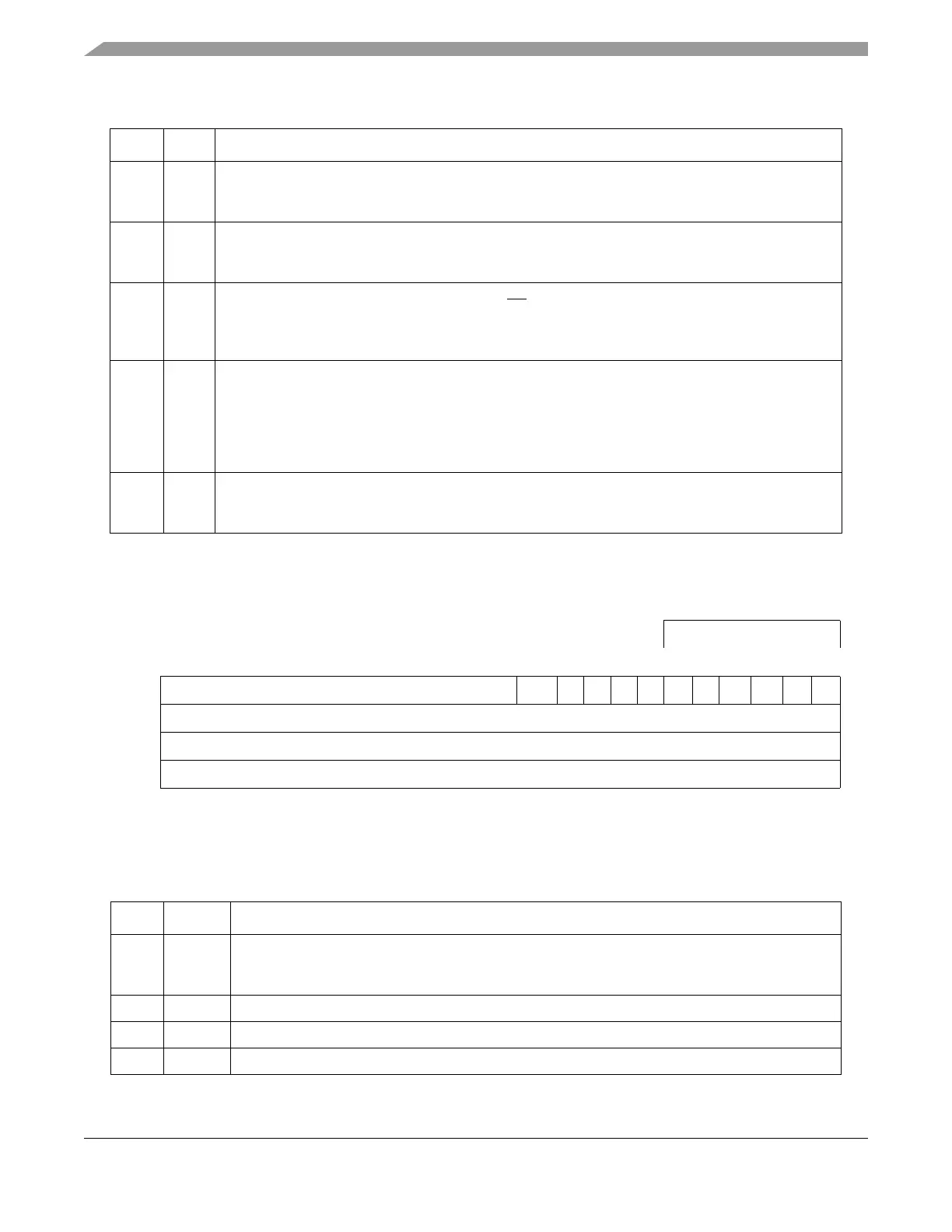

Table 3-6. MAS3—RPN and Access Control

Bits Name Description

0–19 RPN Real page number

Only bits that correspond to a page number are valid. Bits that represent offsets within a page are

ignored and should be zero.

20–21 — Reserved, should be cleared.

22–25 U0–U3 User bits

26–31 PERMIS Permission bits (UX, SX, UW, SW, UR, SR)

Table 3-5. MAS2—EPN and Page Attributes (Continued)

Bits Name Description

Loading...

Loading...