MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 4-5

4.3.1.2 System Reset Control Register (SIU_SRCR)

The system reset control register (SIU_SRCR) allows software to generate either a software system reset

or software external reset. The software system reset causes an internal reset sequence, while the software

external reset only causes the external RSTOUT pin to be asserted. When written to 1, the SER bit

automatically clears after a predetermined number of clock cycles (See Section 4.2.2, “Reset Output

(RSTOUT)”). If the value of the SER bit is 1 and a 0 is written to the bit, the bit is cleared and the RSTOUT

pin is negated regardless of whether the relevant number of clocks has expired.

The CRE bit in the SIU_SRCR allows software to enable a checkstop reset. If enabled, a checkstop reset

will occur if the checkstop reset input to the reset controller is asserted. The checkstop reset is enabled by

default.

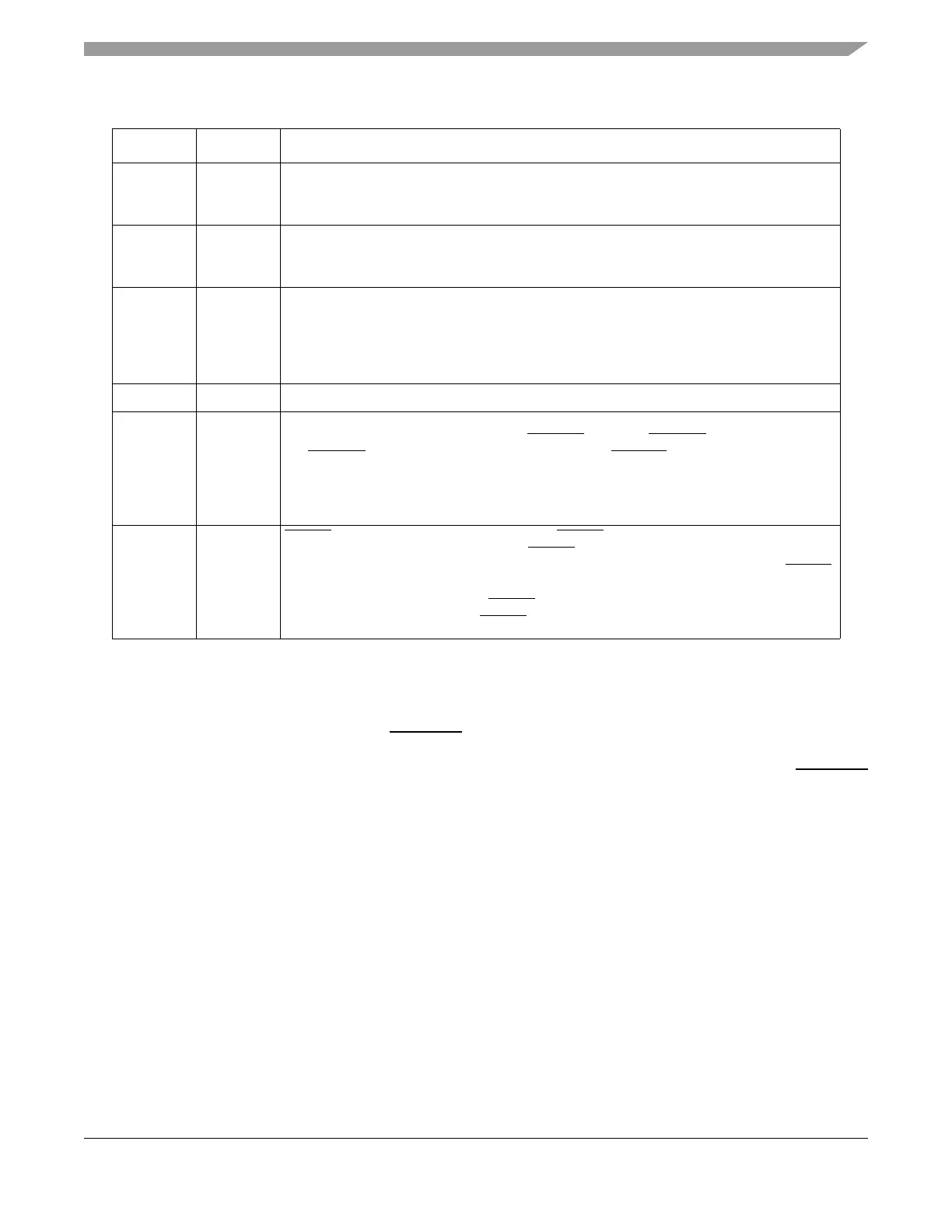

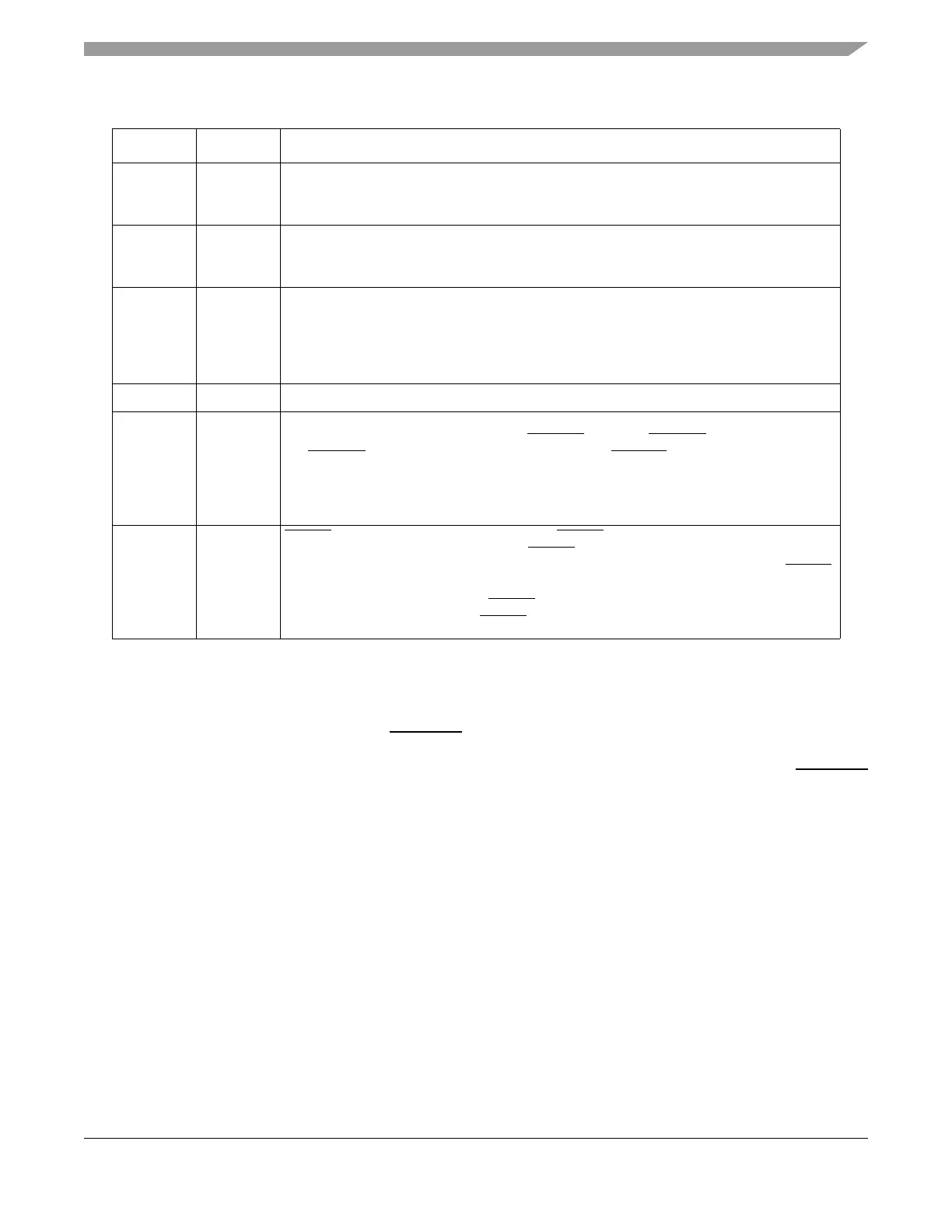

14 SSRS Software system reset status

0 No software system reset has occurred.

1 A software system reset has occurred.

15 SERF Software external reset flag

0 No software external reset has occurred.

1 A software external reset has occurred.

16 WKPCFG Weak pull configuration pin status

0 WKPCFG pin latched during the last reset was logic 0 and weak pull down is the default

setting.

1 WKPCFG pin latched during the last reset was logic 1 and weak pull up is the default

setting.

17–28 — Reserved.

29–30 BOOTCFG Reset configuration pin status. Holds the value of the BOOTCFG[0:1] pins that was latched

4 clocks before the last negation of the RSTOUT

pin, if the RSTCFG pin was asserted. If

the RSTCFG pin was negated at the last negation of RSTOUT, the BOOTCFG field is set

to the value 0b00. The BOOTCFG field is used by the BAM program to determine the

location of the reset configuration halfword. See Tab le 4 -1 1 for a translation of the reset

configuration halfword location from the BOOTCFG field value.

31 RGF RESET

glitch flag. Set by the MCU when the RESET pin is asserted for more than 2 clocks

clock cycles, but less than the minimum RESET assertion time of 10 consecutive clocks to

cause a reset. This bit is cleared by the reset controller for a valid assertion of the RESET

pin or a power-on reset or a write of 1 to the bit.

0 No glitch was detected on the RESET pin.

1 A glitch was detected on the RESET

pin.

Table 4-2. SIU_RSR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...