MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 4-11

4.4.3.2 WKPCFG Pin (Reset Weak Pullup/Pulldown Configuration)

As shown in Table 4-6, the signal on the WKPCFG pin determines whether specific eTPU and eMIOS pins

are connected to weak pull up or weak pull down devices during and after reset (see Chapter 2, “Signal

Description,” for the eTPU and eMIOS pins that are affected by WKPCFG). For all reset sources except

the software external reset, the WKPCFG pin is applied starting at the assertion of the internal reset signal

(as indicated by the assertion of RSTOUT). If the WKPCFG signal is logic high at this time, pull up

devices will be enabled on the eTPU and eMIOS pins. If the WKPCFG signal is logic low at the assertion

of the internal reset signal, pull down devices will be enabled on those pins. The value on WKPCFG must

be held constant during reset to avoid oscillations on the eTPU and eMIOS pins caused by switching pull

up/down states. The final value of WKPCFG is latched 4 clock cycles before the negation of RSTOUT.

After reset, software may modify the weak pull up/down selection for all I/O pins through the PCRs in the

SIU.

Also refer to Chapter 2, “Signal Description,” for information about the WKPCFG pin.

4.4.3.3 BOOTCFG[0:1] Pins (MCU Configuration)

In addition to specifying the RCHW location, the values latched on the BOOTCFG[0:1] pins at reset are

used to initialize the internal flash memory enabled/disabled state, and whether no arbitration or external

arbitration of the external bus interface is selected. Additionally, the RCHW can determine either directly

or indirectly how the MMU is configured, how the external bus is configured, CAN or eSCI module and

pin configuration, Nexus enabling, and password selection.

Also refer to Chapter 2, “Signal Description,” for information about the BOOTCFG pins.

4.4.3.3.1 BOOTCFG[0:1] Configuration in the 208 Package

In the 208 BGA package of the MPC5553, the BOOTCFG0 pin is unavailable and BOOTCFG1 has a

constant value based on PLLCFG0. The device configuration is mapped based on Table 4-7.

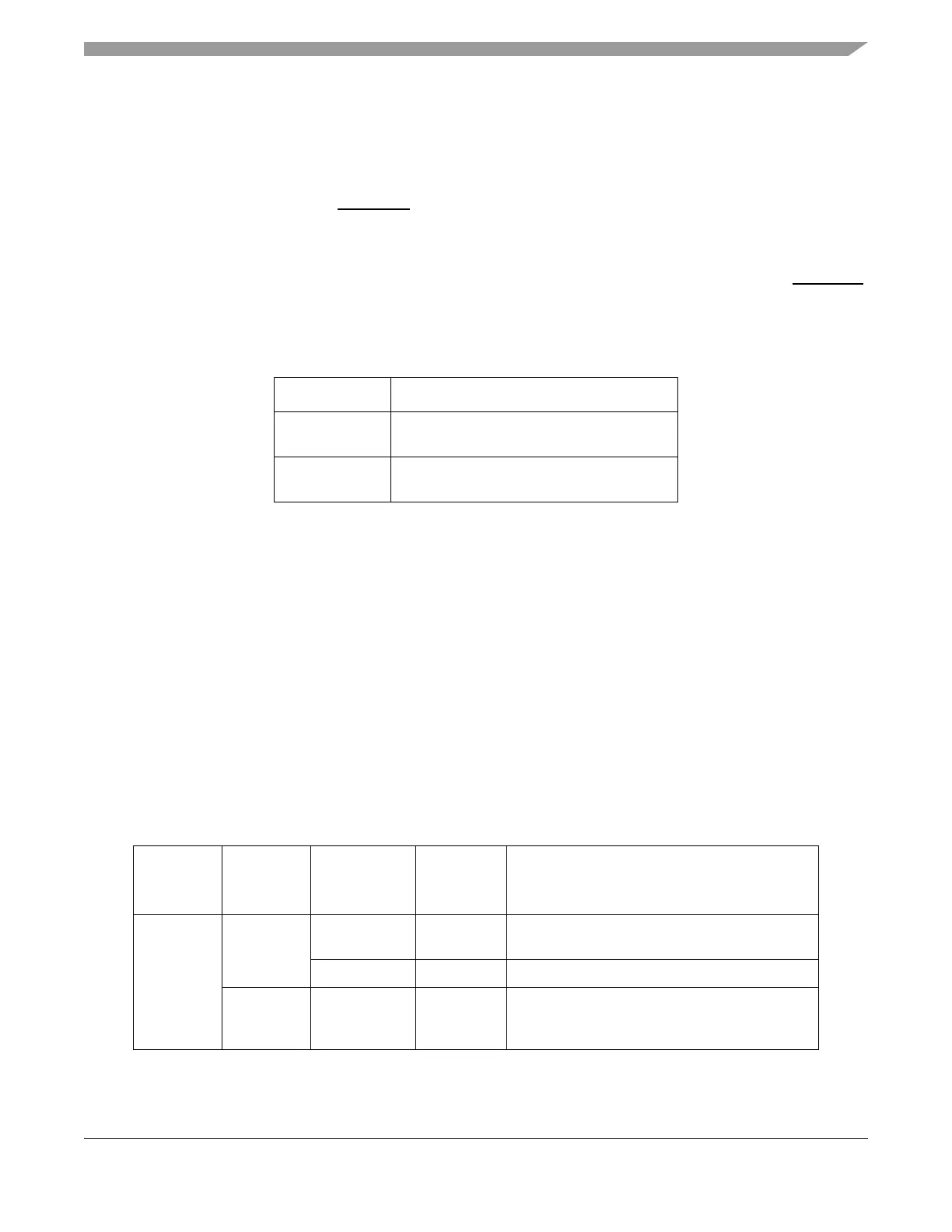

Table 4-6. WKPCFG Settings

WKPCFG Description

0 Weak pulldown applied to eTPU and eMIOS

pins at reset

1 Weak pullup applied to eTPU and eMIOS

pins at reset

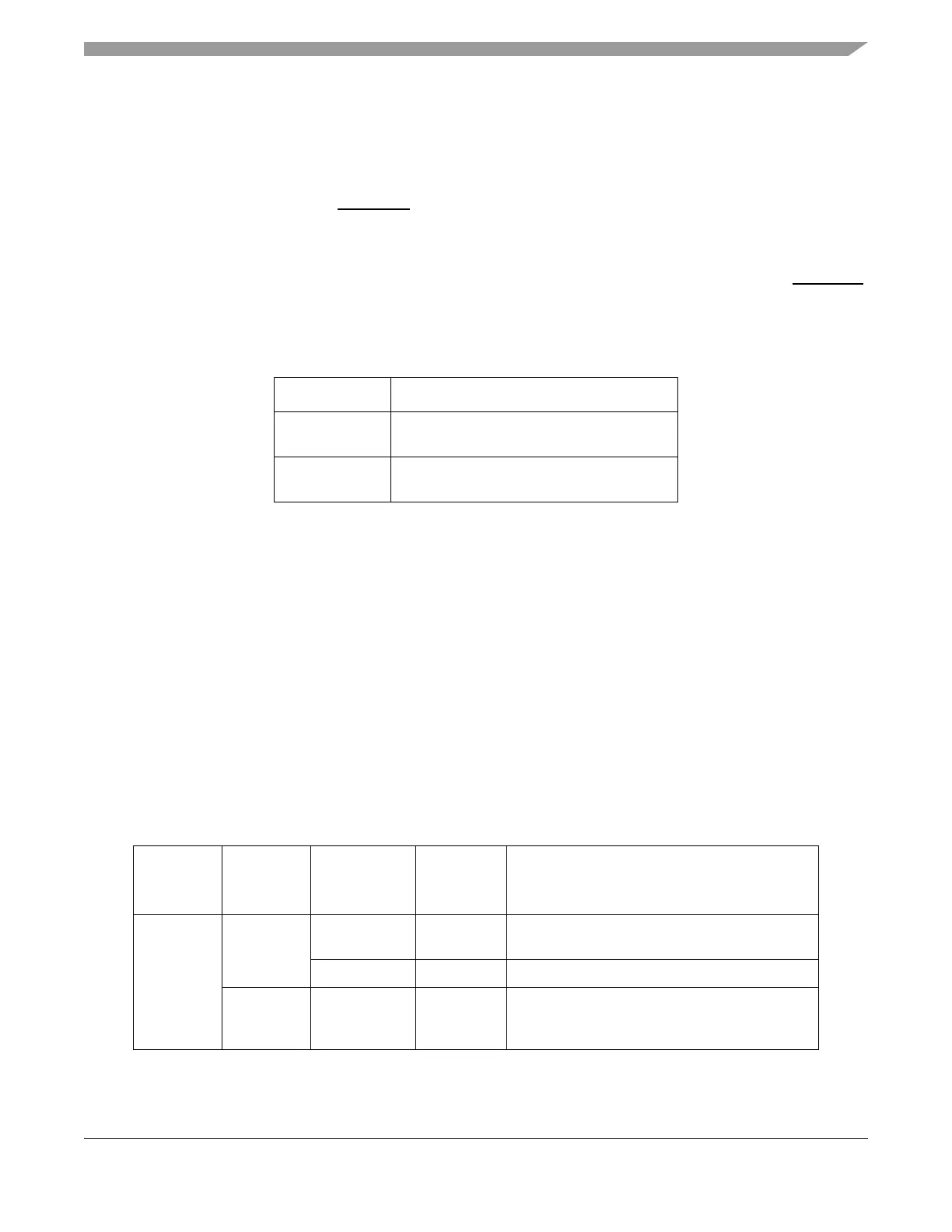

Table 4-7. Boot Configuration in the 208 BGA

PLLCFG0 BOOTCFG1

Boot Identifier

Field

(RCHW)

Boot Mode Configuration Word Source

0

0

Valid Internal The lowest address of one of the six low address

spaces (LAS) in internal flash memory.

Invalid Serial Not applicable

1 — Serial Not applicable

Loading...

Loading...