MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 9-15

9.3.1.5 eDMA Set Enable Request Register (EDMA_SERQR)

The EDMA_SERQR provides a simple memory-mapped mechanism to set a given bit in the

EDMA_ERQRH or EDMA_ERQRL to enable the DMA request for a given channel. The data value on a

register write causes the corresponding bit in the EDMA_ERQRH or EDMA_ERQRL to be set. Setting

bit 1 (SERQn) provides a global set function, forcing the entire contents of EDMA_ERQRH and

EDMA_ERQRL to be asserted. Reads of this register return all zeroes. For the MPC5553, bit 2 (SERQ1)

is not used.

9.3.1.6 eDMA Clear Enable Request Register (EDMA_CERQR)

The EDMA_CERQR provides a simple memory-mapped mechanism to clear a given bit in the

EDMA_ERQRH or EDMA_ERQRL to disable the DMA request for a given channel. The data value on

a register write causes the corresponding bit in the EDMA_ERQRH or EDMA_ERQRL to be cleared.

Setting bit 1 (CERQn) provides a global clear function, forcing the entire contents of the EDMA_ERQRH

and EDMA_ERQRL to be zeroed, disabling all DMA request inputs. Reads of this register return all

zeroes. For the MPC5553, bit 2 (CERQ1) is not used.

Table 9-5. EDMA_EEIRH, EDMA_EEIRL Field Descriptions

Bits Name Description

0–31 EEIn Enable error interrupt n.

0 The error signal for channel n does not generate an error interrupt.

1 The assertion of the error signal for channel n generate an error interrupt request.

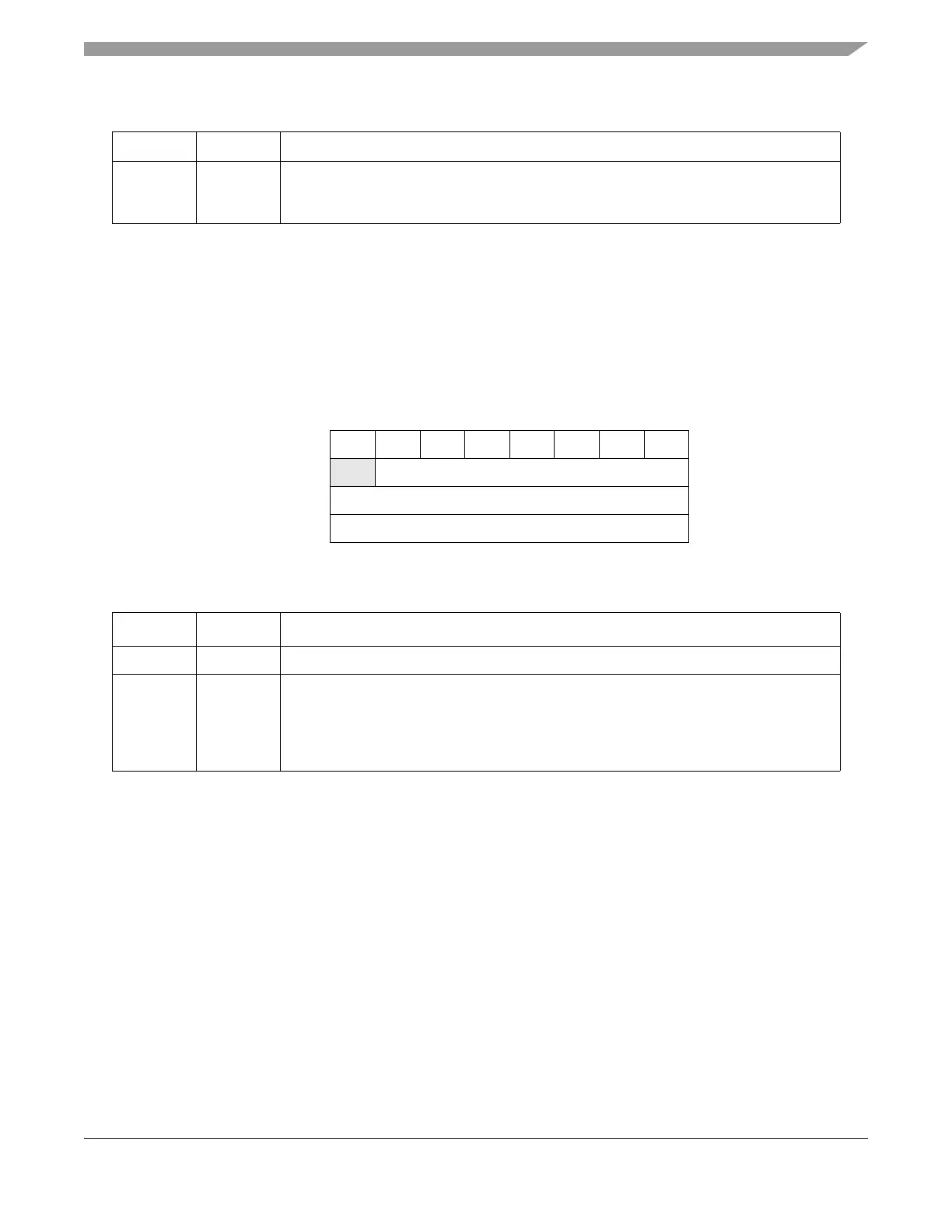

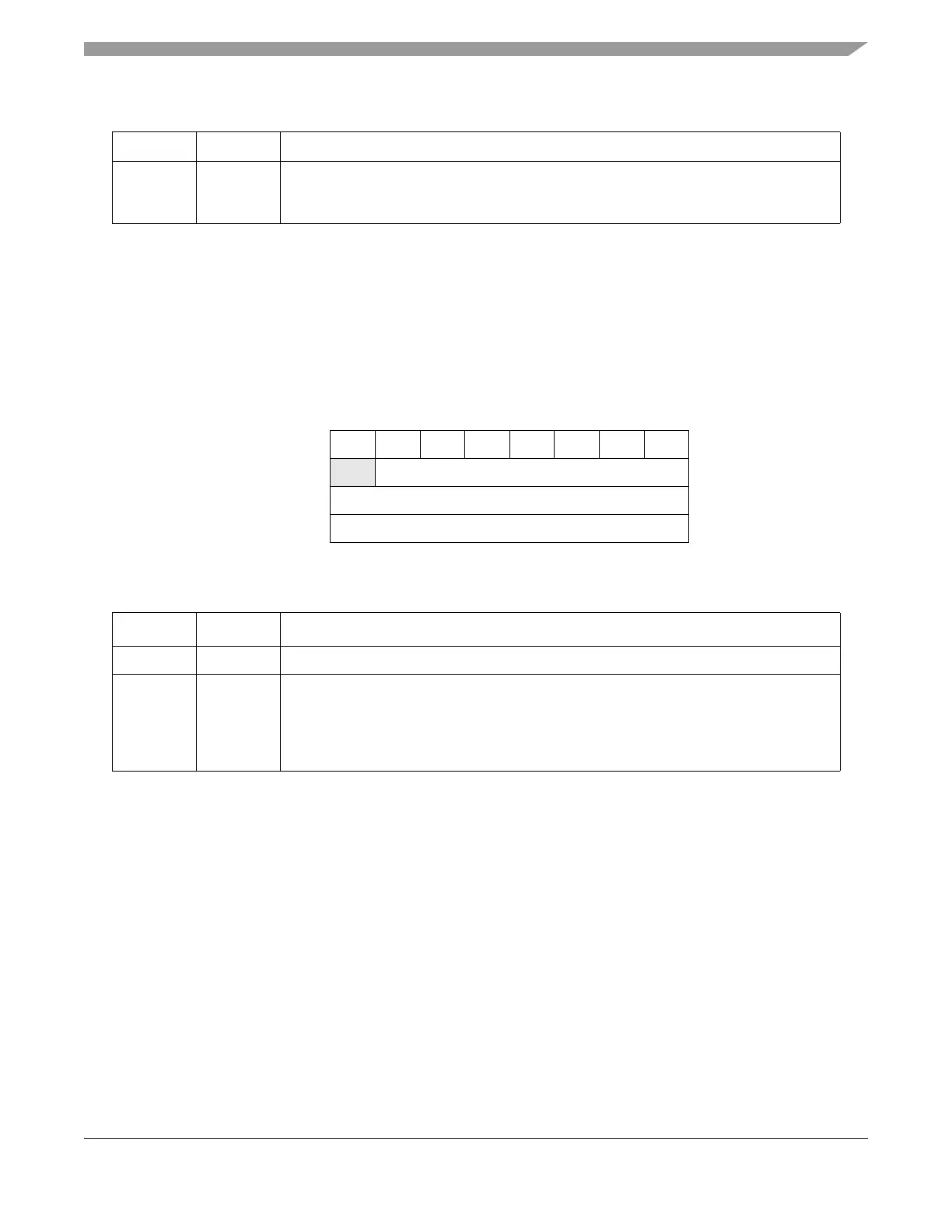

01234567

R00000000

W SERQ[0:6]

Reset00000000

Reg Addr Base + 0x0018

Figure 9-8. eDMA Set Enable Request Register (EDMA_SERQR)

Table 9-6. EDMA_SERQR Field Descriptions

Bits Name Description

0 — Reserved.

1–7 SERQ

[0:6]

Set enable request.

0–63 Set the corresponding bit in EDMA_ERQRH or EDMA_ERQRL

64–127 Set all bits in EDMA_ERQRH and EDMA_ERQRL

Note: For the MPC5553, the value 32-63 [bit 2 (SERQ1)] is reserved.

Loading...

Loading...