MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

9-22 Freescale Semiconductor

9.3.1.15 eDMA Channel n Priority Registers (EDMA_CPRn)

When the fixed-priority channel arbitration mode is enabled (EDMA_CR[ERCA] = 0), the contents of

these registers define the unique priorities associated with each channel within a group. The channel

priorities are evaluated by numeric value; that is, 0 is the lowest priority, 1 is the next higher priority, then

2, 3, etc. Software must program the channel priorities with unique values, otherwise a configuration error

will be reported. The range of the priority value is limited to the values of 0 through 15. When read, the

GRPPRI bits of the EDMA_CPRn register reflect the current priority level of the group of channels in

which the corresponding channel resides. GRPPRI bits are not affected by writes to the EDMA_CPRn

registers. The group priority is assigned in the EDMA_CR. See Figure 9-2 and Table 9-2 for the

EDMA_CR definition.

Channel preemption is enabled on a per-channel basis by setting the ECP bit in the EDMA_CPRn register.

Channel preemption allows the executing channel’s data transfers to be temporarily suspended in favor of

starting a higher priority channel. After the preempting channel has completed all of its minor loop data

transfers, the preempted channel is restored and resumes execution. After the restored channel completes

one read/write sequence, it is again eligible for preemption. If any higher priority channel is requesting

service, the restored channel will be suspended and the higher priority channel will be serviced. Nested

preemption (attempting to preempt a preempting channel) is not supported. After a preempting channel

begins execution, it cannot be preempted. Preemption is only available when fixed arbitration is selected

for both group and channel arbitration modes.

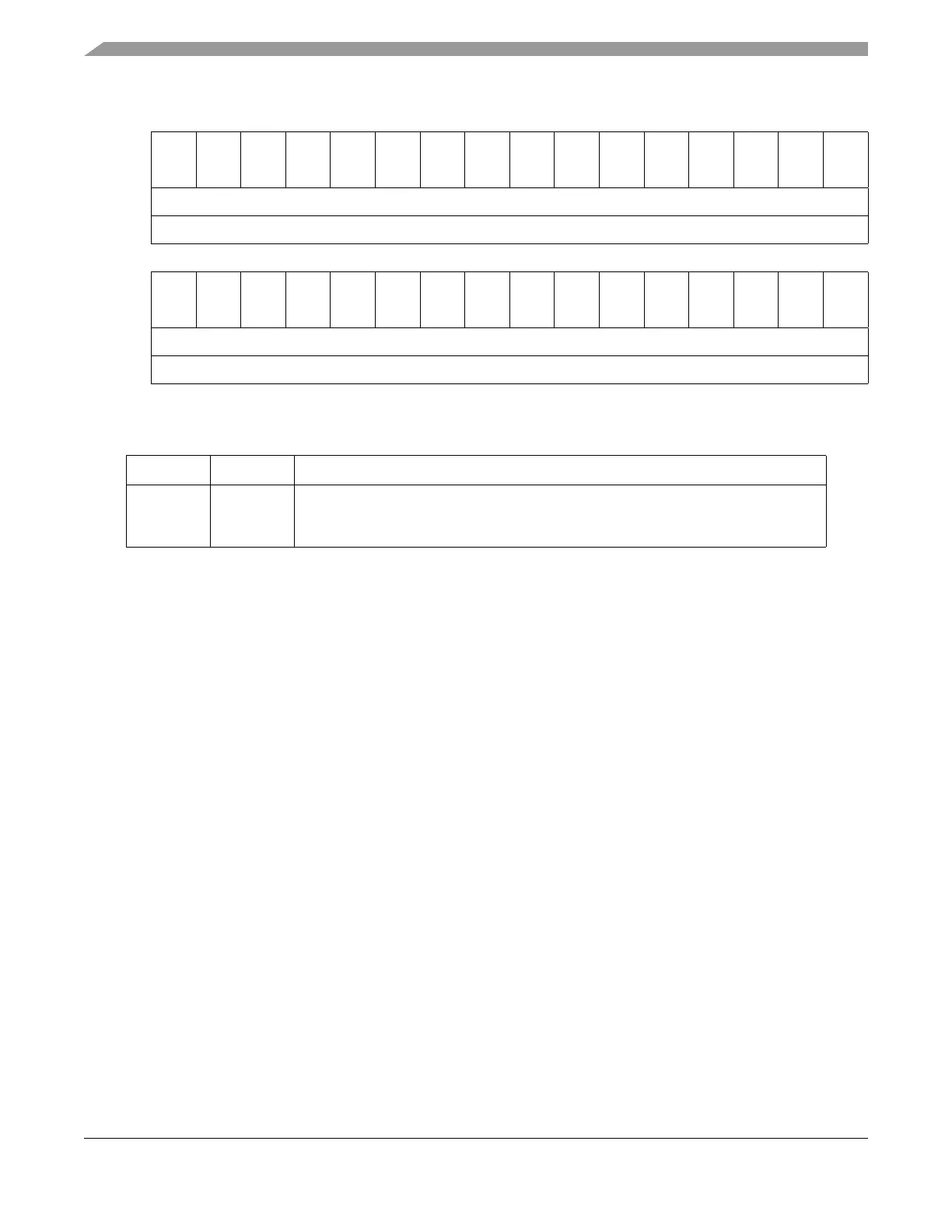

0123456789101112131415

RERR

31

ERR

30

ERR

29

ERR

28

ERR

27

ERR

26

ERR

25

ERR

24

ERR

23

ERR

22

ERR

21

ERR

20

ERR

19

ERR

18

ERR

17

ERR

16

W

Reset0000000000000000

Base + 0X002C

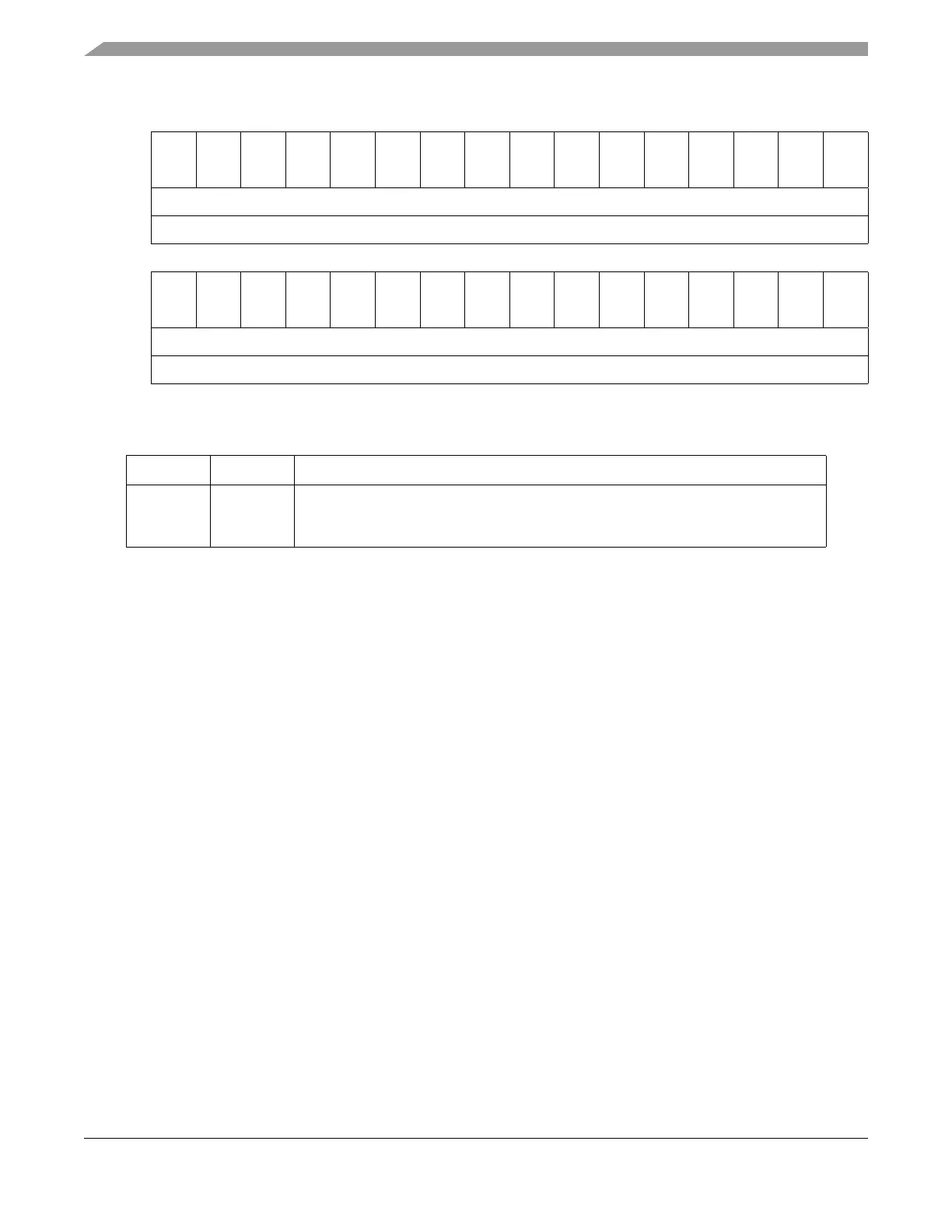

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RERR

15

ERR

14

ERR

13

ERR

12

ERR

11

ERR

10

ERR

09

ERR

08

ERR

07

ERR

06

ERR

05

ERR

04

ERR

03

ERR

02

ERR

01

ERR

00

W

Reset0000000000000000

Base + 0X002C

Figure 9-19. eDMA Error Low Register (EDMA_ERL)

Table 9-15. EDMA_ERH, EDMA_ERL Field Descriptions

Bits Name Description

0–31 ERRn eDMA Error n.

0 An error in channel n has not occurred.

1 An error in channel n has occurred.

Loading...

Loading...