MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 9-23

9.3.1.16 Transfer Control Descriptor (TCD)

Each channel requires a 256-bit transfer control descriptor for defining the desired data movement

operation. The channel descriptors are stored in the local memory in sequential order: channel 0, channel

1,... channel 63 (MPC5554) or channel 0, channel 1,... channel 31 (MPC5553). The definitions of the TCD

are presented as twenty-three variable-length fields. Table 9-17 is field list of the basic TCD structure.

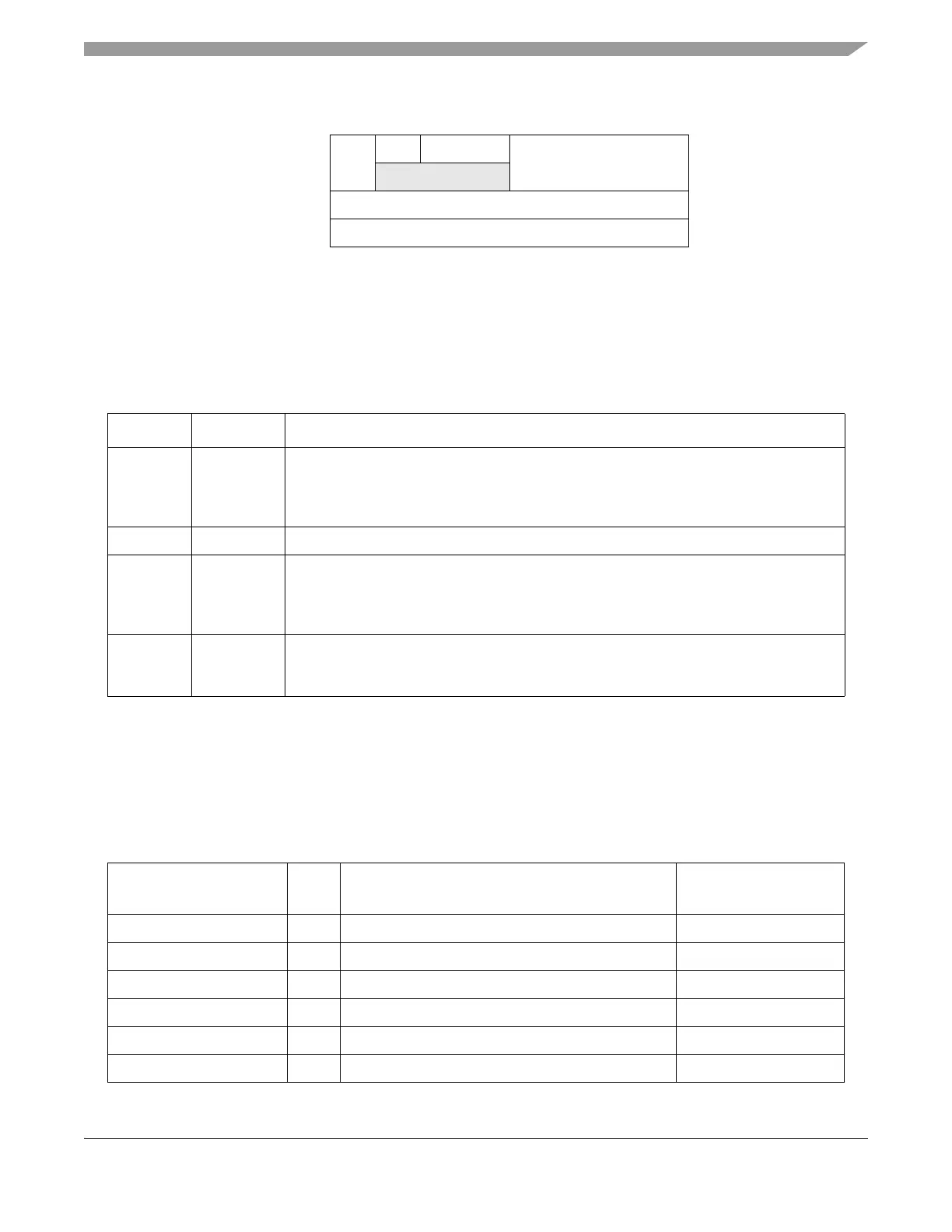

01234567

R ECP 0 GRPPRI CHPRI

W

Reset 0 0 —

1

Reg Addr Base + 0x100 + n

1

The reset value for the group and channel priority fields,

GRPPRI[0–1] and CHPRI[0–3], is equal to the

corresponding channel number for each priority register;

that is, EDMA_CPR31[GRPPRI] = 0b01 and

EDMA_CPR31[CHPRI] = 0b1111.

Figure 9-20. eDMA Channel n Priority Register (EDMA_CPRn)

Table 9-16. EDMA_CPRn Field Descriptions

Bits Name Description

0 ECP Enable channel preemption.

0 Channel n cannot be suspended by a higher priority channel’s service request.

1 Channel n can be temporarily suspended by the service request of a higher priority

channel.

1 — Reserved.

2–3 GRPPRI

[0:1]

Channel n current group priority. Group priority assigned to this channel group when

fixed-priority arbitration is enabled. These two bits are read only; writes are ignored. The

reset value for the group priority fields, is equal to the corresponding channel number for

each priority register; that is, EDMA_CPR31[GRPPRI] = 0b01.

4–7 CHPRI

[0:3]

Channel n arbitration priority. Channel priority when fixed-priority arbitration is enabled.

The reset value for the channel priority fields CHPRI[0–3], is equal to the corresponding

channel number for each priority register; that is, EDMA_CPR31[CHPRI] = 0b1111.

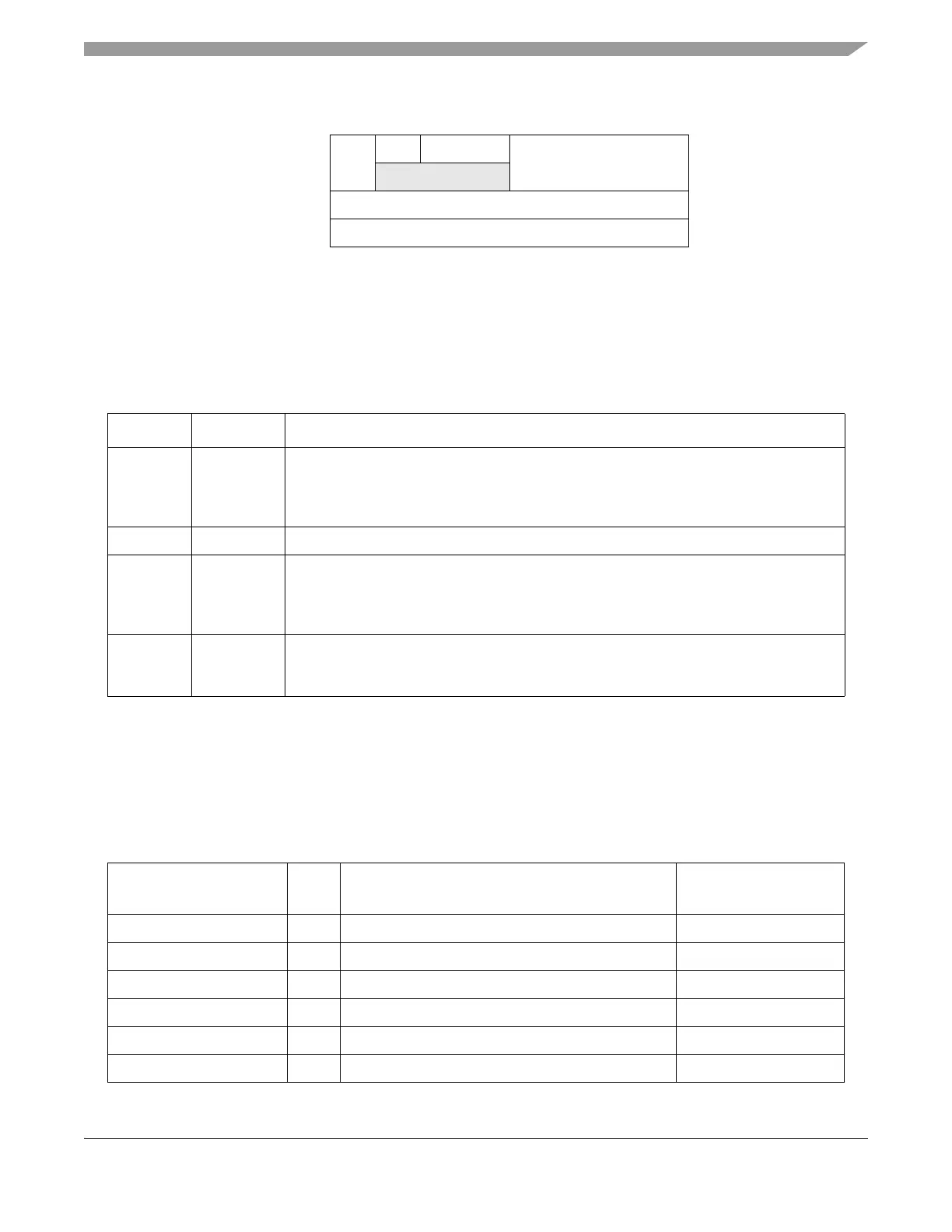

Table 9-17. TCDn 32-bit Memory Structure

eDMA Bit Offset

Lengt

h

TCDn Field Name TCDn Abbreviation

0x1000 + (32 x n) + 0 32 Source Address SADDR

0x1000 + (32 x n) + 32 5 Source address modulo SMOD

0x1000 + (32 x n) + 37 3 Source data transfer size SSIZE

0x1000 + (32 x n) + 40 5 Destination address modulo DMOD

0x1000 + (32 x n) + 45 3 Destination data transfer size DSIZE

0x1000 + (32 x n) + 48 16 Signed Source Address Offset SOFF

Loading...

Loading...